フラッシュADC入門

フラッシュADC (パラレルADCとも呼ばれる) は、変換速度が非常に速いため、ADCアーキテクチャにおいて特別な位置を占めています。「フラッシュ」という名前は、カメラのフラッシュに似た、比較的即座に変換を行うADCの能力に由来しています。フラッシュADCは、速度が重要でレイテンシを最小限に抑える必要がある場合に頻繁に使用されます。

フラッシュADCの基本的な考え方はシンプルで、入力アナログ値を多数の基準電圧と比較し、1ステップでデジタル出力を提供します。アナログ入力のデジタル表現に到達するために反復または逐次プロセスを利用する他のADCアーキテクチャとは異なり、フラッシュADCはシングルパスでそれを行います。

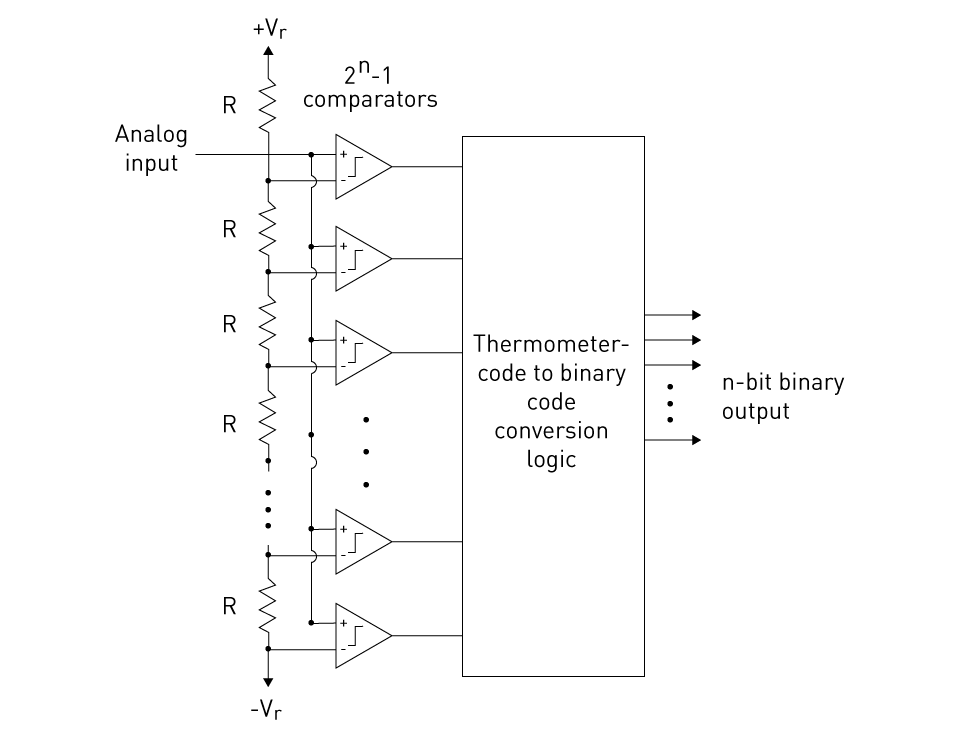

コンパレータの配列、抵抗ラダー、エンコーダはフラッシュADCの基本部品です。アレイ内の各コンパレータは、入力電圧を所定の基準電圧と比較する役割を果たします。基準電圧は抵抗ラダーによって生成され、これはフルスケールの入力電圧範囲を多くのより小さな間隔に分離します。コンパレータ配列は、上位ビット数で表される値の単項表現である温度計コードを生成します。エンコーダはこのコードを通常のバイナリ形式に変換します。

簡単な例として、ある数が他の数と比較するとどうかを素早く評価しなければならない状況を考えてみましょう。一つ一つの比較を評価するのではなく、フラッシュADCは、それぞれに特定の数が割り当てられた複数の審判のように動作し、それらすべてが同時に判断を行います。この並列判断処理により、アナログ信号をデジタル出力に迅速に変換することができます。

しかし、この速度にはコストがかかります。フラッシュADCの並列アーキテクチャは、分解能が向上するにつれて部品の数が増加し、結果として消費電力が増加し、複雑さと容量が増加します。その結果、速度が最も重要であり、分解能の要件が妥当である場合に一般的に使用されます。

以下のパートでは、フラッシュADCのアーキテクチャ、それらの動作、利点と欠点、それらが最も適しているアプリケーション、および重要な設計上の考慮事項とトレードオフについて詳しく見ていきます。

フラッシュADCのアーキテクチャ

コンパレータアレイ

フラッシュADCの中心的な部品はコンパレータアレイです。このアレイはコンパレータの並列配置で構成されており、各コンパレータは入力アナログ電圧を指定された基準電圧と比較します。配列に必要なコンパレータの数は2^N-1と計算され、Nはビット単位の分解能を表します。例えば、8ビットフラッシュADCでは、2^8-1=255のコンパレータが必要です。

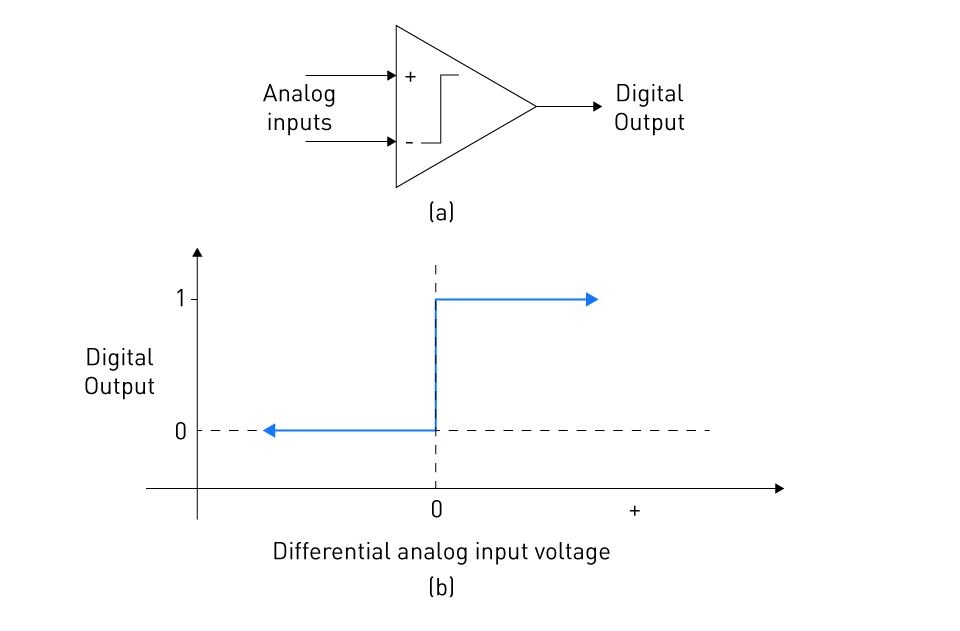

図1 : コンパレータ (a) コンパレータシンボル (b) コンパレータ入出力伝達関数

実際、配列内の各コンパレータは入力電圧が対応する基準電圧より大きいか小さいかに基づいて通常、「1」または「0」で表されるバイナリ出力を生成します。すべてのコンパレータからの出力は、温度計のマークと似ているため、「温度計コード」と呼ばれるものを形成します。このコードで、より多い「1」の存在はより高いレベルを示し、温度計の上昇する水銀に似ています。

図2 : nビットフラッシュADC

抵抗ラダー

抵抗ラダーは、本質的に直列接続された抵抗のネットワークであり、入力電圧が比較される基準電圧を生成します。電圧リファレンス全体はこのラダーによって等間隔に分割されます。NビットフラッシュADCの抵抗ラダーには、2^Nの抵抗があります。

抵抗ラダーは、入力電圧を比較するための増分段を確立するために重要です。ラダーの各タップは配列のコンパレータの1つにリンクされています。抵抗ラダーのタップ間の電圧差は、フルスケール電圧範囲を2^Nで除算したもので、ADCが検出できる電圧変化の最小値です。

エンコーダ

温度計コードとして表されるコンパレータ配列の出力はエンコーダに渡されます。エンコーダの仕事は、温度計のコードをデジタル機器で読み取ることができるバイナリコードに変換することです。温度計のコードは非生産的であるため (特に高分解能で)、エンコーダはデータをよりコンパクトなバイナリ形式に圧縮します。様々なエンコーディングアルゴリズムがあり、プライオリティエンコーディングが最も多く使用されます。例えば、8つのコンパレータがあり、入力電圧が最初の5つの基準電圧を超える場合、温度計コードは「11111000」になります。エンコーダは温度計コードをバイナリに変換します。この場合、3ビットフラッシュADCではに101になります。

フラッシュADCの動作

並列比較

フラッシュADCの基本的な動作は機能である並列比較を中心に展開され、カメラフラッシュのような高速なアナログ・デジタル変換に由来します。同時に、入力アナログ電圧は、前に説明したように、抵抗ラダーによって生成される複数の基準電圧と比較されます。

並列セットアップでは、アレイ内の各コンパレータは入力電圧を受け取り、指定された基準電圧と比較します。この同時比較プロセスにより、フラッシュADCの高速動作が可能になります。

この並列比較の結果、出力は温度計コードの形式になります。温度計コードは、入力電圧がそれぞれの基準電圧より高いコンパレータがすべて「1」を出力し、残りのコンパレータでは「0」を出力する、ワンショットのバイナリパターンを表します。例えば、入力電圧がフラッシュADCの5つのコンパレータのうち3つの基準電圧を超えるものとします。そのようなシナリオでは、結果として温度計コードは「11100」になります。

エンコード処理

並列比較の後、温度計コードはエンコーダを介して処理され、そこで温度計コードの従来のバイナリ表現への変換が行われます。この重要なステップは、出力ラインの数を最小限に抑え、さらなるデジタル処理タスクのためにより便利なデータをレンダリングするのに役立ちます。

優先エンコーディングは、フラッシュADCで使用される代表的なエンコーディング方式です。プライオリティエンコーディングは、温度計コードを、最上位の「1」の位置を表す2進数に変換するプロセスです。温度計コード「11100」の最上位の「1」は3位であり、3ビットADCの2進法に相当する値は「011」です。アプリケーションによっては、グレイコードのエンコーディングなどの他のエンコーディングシステムを利用することができます。

重要な考慮事項は、フラッシュADCの性能を損なうことなく高速性能を確保するために、エンコーディング処理を迅速に実行する必要性です。この目的を達成するために、最適化されたゲートレベル設計を特徴とする特殊なエンコーディング回路が一般的に使用されています。これらの専用回路は効率的で高速なエンコーディングを保証するように調整されており、フラッシュADCの全体的な速度と有効性をサポートします。

フラッシュADCの利点

速度

フラッシュADCの速度は、最も注目すべき利点の1つです。変換プロセスの同時性のため、フラッシュADCのアーキテクチャは本質的に高速動作に適しています。前に述べたように、フラッシュADCは入力電圧を多数の基準値と同時に比較する並列比較アプローチを使用します。

これは、他のADCシステムでは代表的で、反復的な性質のために実行に時間がかかる逐次近似やカウント法の必要要件を回避します。この並列性により、フラッシュADCはミリ秒以下の変換時間を達成できます。このため、フラッシュADCは、オシロスコープ、レーダーシステム、高周波通信など、リアルタイムまたは超高速のデータ収集を必要とするアプリケーションに最適です。

シンプルさ

コンセプトのシンプルさはフラッシュADCの利点の1つです。基本的な手続きは並列比較とエンコーディングの二段階だけで構成されます。変換プロセスには複雑なアルゴリズムや反復的な手法は含まれていません。このような使いやすさは、技術者や学生の理解を容易にし、学習曲線を短くすることにつながります。

さらに、シンプルであるということは、ADCが他のタイプのADCに比べて必要な部品が少ないため、よりコンパクトになる可能性があることを意味します。特定のアプリケーションでは、このシンプルさは費用対効果につながる場合があり、特に高速が基本的なニーズで分解能がそれほど高くない場合にそうです。

それでも、フラッシュADCのシンプルさは利点を提供する一方で、一定の欠点を伴うことを認識することが非常に重要です。希望の分解能が高まるにつれて、必要なコンパレータの数が大幅に増加し、拡張性の懸念、およびレイアウトと消費電力に関する複雑さの増加へとつながります。これらの課題にもかかわらず、フラッシュADCは、そのシンプルさと迅速な動作により、高性能と中程度の分解能が優先される特定のアプリケーションにとって優れた選択肢であり続けています。

フラッシュADCの欠点

拡張性と消費電力

フラッシュADCには速度とシンプルさの点で利点がありますが、大きな欠点もあります。フラッシュADCの主要な問題の1つは拡張性です。Nビットの分解能のために、アーキテクチャは2^N-1コンパレータを必要とします。結果として、必要とされるコンパレータの数は、分解能が1ビット増えるたびに指数関数的に増加します。この特性は高分解能フラッシュADCの構築の実行可能性を著しく制限します。

拡張性の問題に加えて、消費電力は深刻な欠点になります。コンパレータの数が増えると、必要な電力も増加します。アレイ内の各コンパレータは電力を消費するため、中程度の分解能を持つフラッシュADCは、他のADCアーキテクチャよりも大幅に多くの電力を消費する場合があります。このような高い消費電力により、電力効率が重要なアプリケーションが制限される可能性があり、これにはバッテリー駆動デバイスや温度制約のあるシステムが含まれます。

高分解能用の複雑さ

利点のセクションで述べたように、フラッシュADCのシンプルさは分解能が大きくなるにつれて低下する傾向があります。ビット数が増えると、アーキテクチャは指数関数的に多くのコンパレータとより洗練された抵抗ラダーネットワークを必要とします。前述したように、これは消費電力に影響を与え、設計とレイアウトの複雑さをもたらします。

一例として、配線の決定と配置の複雑さは構成要素の多さによって増加します。さらに、コンパレータ間のアライメントを達成することは、線形性を維持するために重要であり、そこではわずかな誤差でさえ変換プロセス中にかなりの不正確さをもたらす可能性があります。これは綿密な計画が必要で、しばしば較正メカニズムを伴うため、さらに複雑になります。

また、部品点数を増やすことで、ADCに対応するために必要なチップ面積が拡大するため、スペースが限られている状況では不利になる可能性があります。この複雑さの増大は製造コストにも影響を及ぼし、フラッシュADCは、逐次近似ADCやシグマデルタADCなどの代替アーキテクチャと比較して、高分解能でコスト効率が比較的低くなります。

フラッシュADCに適したアプリケーション

拡張性と消費電力の点で限界があるにもかかわらず、フラッシュADCはその卓越した速度と単純さのために、特定のアプリケーションで依然としてADCとして選ばれています。超高速データ収集とビデオ処理は、フラッシュADCの2つの一般的なアプリケーションです。

超高速データ収集

フラッシュADCは、データを非常に高速で捕らえることが重要な状況で不可欠です。例えば、レーダーやオシロスコープのような高周波信号サンプリングのアプリケーションでは、データは従来のADCアーキテクチャでは到達できない速度で捕らえられ、デジタル化される必要があります。

レーダーシステムにおけるエコー信号の迅速な捕捉は、物体の位置と速度を検出するために重要です。フラッシュADCの速度のため、これらの信号を高い時間分解能で捕捉することができ、より正確でタイムリーな分析が可能になります。

オシロスコープ、特に高周波信号を捕捉するために設計されたオシロスコープの領域では、フラッシュADCは十分なデータポイントの収集を保証する重要な役割を果たし、それによって波形の正確な再構築を可能にします。これは、信号の忠実性と正確なタイミングの維持が基本的な必須条件となる電気通信のような分野では非常に重要です。

ビデオ処理

ビデオ処理もフラッシュADCが一般的に使用される分野です。ビデオ信号処理とは、連続したアナログ信号をデジタル形式に変換し、処理、保存、転送することです。ビデオの完全性を確保するには、高いサンプリングレートで動作可能なADCが必要です。

高精細テレビ (HDTV) や高フレームレートカメラのように、各フレームに含まれるデータ量が大きく、毎秒のフレーム周波数も高くなる状況では、変換を迅速に実行できるため、フラッシュADCが適切な選択肢として出現しています。これにより、そのようなアプリケーションに固有の実質的なデータスループットの管理に非常に適しています。

また、遅延を最小限に抑えることが不可欠なプロ用ビデオ機器の分野では、フラッシュADCが示す高速変換が重要であり、シームレスなリアルタイム性能を保護する役割を実証しています。

設計上の考慮事項とトレードオフ

特定のアプリケーションに合わせたフラッシュADCを策定または選択する過程で、技術者はADCの運用効率、費用対効果、包括的なシステム内での実行可能性に影響を与える多くの要因について熟考する必要があります。その後の議論では、フラッシュADCの領域に内在する主要な設計上の検討と妥協を浮き彫りにするいくつかの重要な側面について掘り下げます。

分解能と複雑さ: フラッシュADCの分解能の増大に伴い、必要なコンパレータの数が指数関数的に急増します。nビット分解能の場合、2^n-1のコンパレータまで必要になります。このように部品数が急速に増加することで、複雑さ、コスト、電力使用量が増加します。ほとんどの場合、高い分解能の追求とそれに続くトレードオフの間の微妙な均衡をとることが必須になります。

速度と消費電力: フラッシュADCは、その速度が非常に速いという評判を築いてきましたが、この特性は電力消費の増大という形で、特に分解能の上昇とともに犠牲を生んでいます。設計の過程で、設計者はシステム内の電力割り当てを熟考し、利用可能な電力貯蔵とは対照的に変換速度を加速するメリットを細心の注意を払って評価する必要があります。

入力キャパシタンス: フラッシュADCに起因する入力キャパシタンスは、コンパレータの並列配置のため、比較的大きなレベルを示すことがあります。この現象は、特に高周波を特徴とするアプリケーションにおいて、駆動回路とシグナルインテグリティの維持に影響を及ぼす可能性があります。したがって、駆動アンプの選択とインピーダンス整合の追求に細心の注意が必要となります。

熱に関する考慮: フラッシュADCの動作構成は、多数の同時動作部品に代表され、注目に値する発熱を引き起こす可能性があります。この状況では、ヒートシンクの利用や適切な気流の提供を含む効果的な熱管理戦略の実施が最も重要な役割を担います。これは、分解能の要求の高さを特徴とする場合に特に当てはまります。

量子化ノイズと線形性: フラッシュADCの高速化は、量子化ノイズの増加や線形性の低下を犠牲にすることがあります。アプリケーションによっては、これは許容できるトレードオフかもしれませんが、より高い精度を必要とするアプリケーションには代替ADCアーキテクチャの方が適しているかもしれません。

コスト: フラッシュADCは複雑で部品数が多いため、特に分解能が上がるにつれて、他のADCアーキテクチャよりも高価になることがよくあります。他のタイプのADCは、コストが大きな制約であるが変換速度が低いアプリケーションでより経済的なソリューションを提供するかもしれません。

レイアウトとルーティングの考慮事項: フラッシュADCの特徴である固有の並列アーキテクチャでは、PCB上の構成要素の物理的なレイアウトとルーティングに細心の注意を払う必要があります。ここでの包括的な目標は、シグナルインテグリティを保護すると同時に、動作性能に影響を及ぼす可能性のある寄生容量とインダクタンスの影響を軽減することです。

アプリケーションの要件: 最終的な分析では、フラッシュADCの採用または製造に関する意思決定プロセスは、基本的に所定のアプリケーションによって示される正確な前提条件に依存します。例えば、超高速のデータ収集を必要とする状況では、フラッシュADCが提供する本来の速度の利点が、消費電力とコストが伴う関連譲歩を目立たなくするかもしれません。

アカウントにログイン

新しいアカウントを作成