ADC誤差入門

アナログ信号をデジタルシステムで処理可能なデジタルデータに変換するためには、A/Dコンバータ (ADC) が不可欠です。その後のデジタル信号処理の有効性はこの変換の精度に大きく依存し、これもデジタル表現の標準に影響を与えます。

正確さの重要性

アナログ・デジタルコンバータ (ADC) の精度は、ADCからのデジタル出力と入力アナログ信号の実際の値との近接性を確立するため、非常に重要な意味を持っています。これは、医療機器、精密測定機器、オーディオ操作などの分野で非常に重要です。変換プロセスの小さな不一致でさえ、実質的な影響をもたらす場合があります。例として、医用画像では、不正確さが患者の状態の誤った評価を引き起こす可能性があります。同様に、オーディオ操作を扱う場合、歪みを引き起こしたり、全体的な音質を損なう可能性があります。したがって、ADC内の誤差要因とその緩和を包括的に把握することは、変換されたデータの信頼性を維持する上で極めて重要です。

誤差がADC性能に与える影響

ADCは、オフセット誤差、ゲイン誤差、線形性誤差、量子化誤差、ノイズ、ジッタなど、さまざまな不正確さや誤差の原因に遭遇します。これらの各要因は、ADCの性能に独特の影響を及ぼします。

オフセット誤差: オフセット誤差は、ADCの本物の出力と理論上の出力との間の一貫した不一致として現れます。その結果、伝達関数全体が変位を経験します。センサデータの取得のように正確な直流 (DC) 精度を必要とする状況では、オフセット誤差は本物の値からかなりの逸脱をもたらす可能性を持っています。

ゲイン誤差: ゲイン誤差は、理想勾配からのADCの伝達関数の勾配の相違に対応します。この不一致は、入力信号の増幅または減衰された表現につながる可能性があります。ゲイン誤差の重要性は、きめ細かい振幅情報が重要である分光法のようなアプリケーションにおいてより顕著です。

線形誤差: 微分非線形性 (DNL) と積分非線形性 (INL) を含む線形性に関連する誤差は、直線からのADCの伝達特性の逸脱に関連します。この逸脱は量子化レベルの一貫性に影響を与え、顕著な精度を要求するアプリケーションでは著しく不利になります。

量子化誤差: 量子化誤差は、実際のアナログ入力と最も近いデジタル表現との間の区別を示します。アナログ-デジタル変換のプロセスに固有の現象であり、この現象はADCの分解能に影響を与えます。

ノイズ: 熱雑音や量子化雑音を含む様々な形態の雑音は、信号に確率論的な揺らぎをもたらします。この干渉は、小さな信号の変動を区別するADCの能力を阻害し、特に低振幅信号を含むアプリケーションにおいて重大な課題を提起します。

ジッタ: ジッタとは、サンプリングクロックのタイミングの変動を指します。その主な影響は高周波信号にあり、時間領域に不確実性をもたらします。その結果、この不確実性はデジタル化された信号の大きさの誤差に変換することができます。

オフセット誤差

A/Dコンバータ (ADC) では、オフセット誤差に起因する不一致は、アナログ信号のデジタルレンダリングの忠実性を損なう可能性のある不正確さの根本的な原因になります。オフセット誤差に関する包括的な知識を習得し、その影響を見極め、それらを測定して軽減する技術を把握することは、ADCの設計と応用において極めて重要です。

定義

入力がゼロスケールまたは最小のとき、オフセット誤差はADCの出力と理想出力の差です。各変換に一定のバイアスを加えた結果、出力値は入力範囲全体にシフトします。オフセットミスは、伝達関数を横軸に沿って移動することによってコード遷移点に変化を生じます。

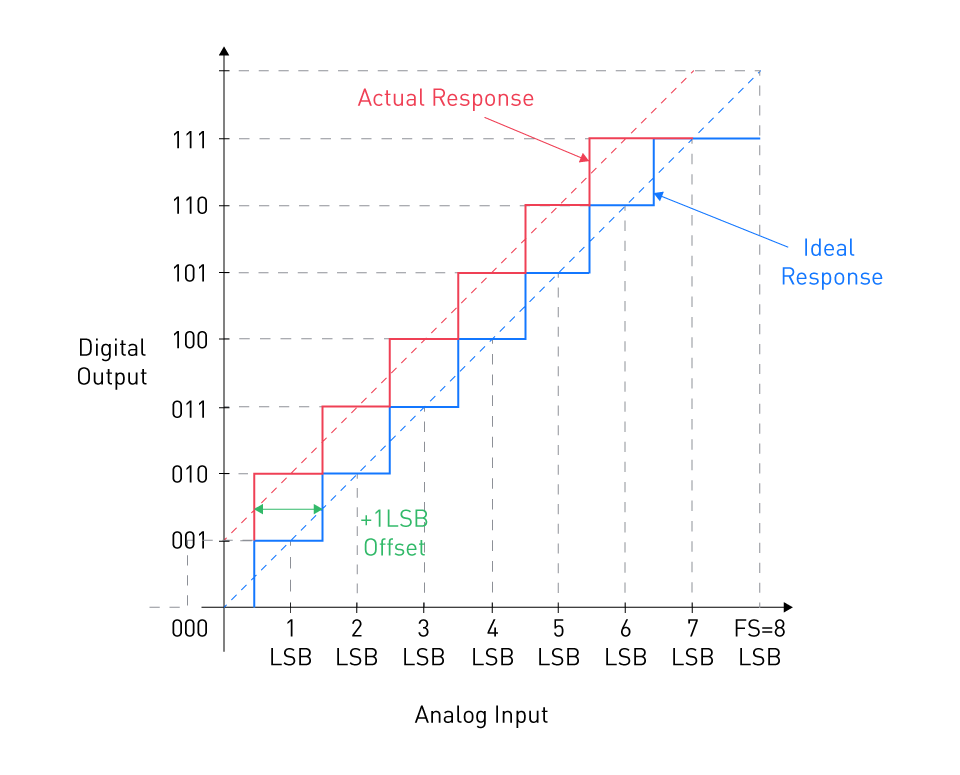

図1 : +1 LSBオフセット、実際の応答、および理想的な応答を示すグラフ

ユニポーラ3ビット理想ADCでは、初期遷移は0.5最小有意ビット (LSB) で行われ、出力が000から001にシフトします。しかし、図1に示すように実際の応答を調べると、ADC出力は0.5 LSBマークで001から010に変化することがわかります。理想的なシナリオでは、001から010への遷移は1.5 LSBで起こるはずです。したがって、これは非理想的な応答が理想特性に比べて左に向かって1LSBシフトすることを意味します。この不一致は+1 LSBのオフセット誤差として定義されます。非理想的応答の線形モデル (図のオレンジ色の線で示されている) を考えると、システムが0V入力に対して001の出力を生成することが明らかで、これは+1 LSBのオフセットを意味します。

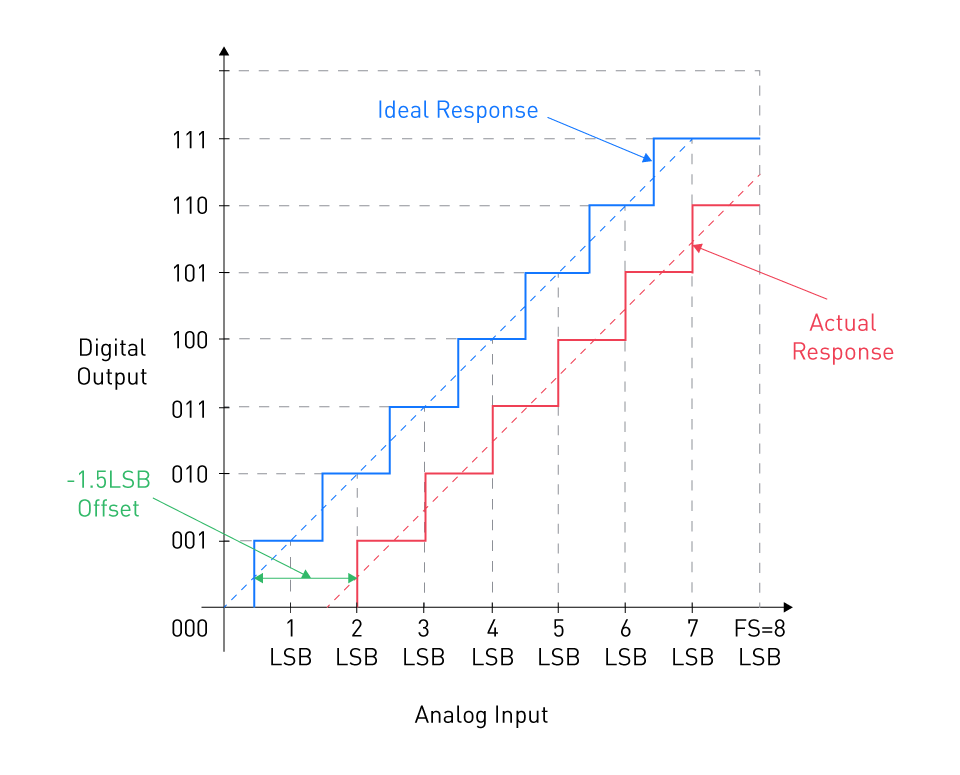

図2 : -1.5 LSBオフセット誤差を伴うADCの応答

原因

オフセット誤差の主な原因は次のとおりです。

部品の不一致: 抵抗やコンデンサなどの内部ADC素子の製造中に生じる欠陥や不規則性は、オフセット誤差として現れる不一致を引き起こす可能性があります。

温度ドリフト: 周囲温度の変化は電子部品の属性を変更する能力を持ち、それらの値に変化させ、それによってオフセット誤差を生じます。

供給電圧の変動: 電源電圧の振動は、基準電圧とアナログ入力の範囲に影響を与え、最終的にオフセット誤差を引き起こす可能性があります。

ADC出力への影響

オフセット誤差がある場合、ADC出力値は均一に動きます。これは、ADCの伝達特性全体を上方または下方にシフトすると見なせるかもしれません。これは、入力がゼロまたは最小でもADC出力がゼロ以外の数値を示すということです。正確なDC測定を必要とするアプリケーションや、小さな電圧変動が重要な差動測定システムでは、これは特に困難なことです。

オフセット誤差を測定する方法

ADCでこの問題を特性化して修正するには、オフセット誤差を測定する必要があります。一般的なアプローチは次のとおりです。直接測定: 最小入力 (通常はゼロ電圧) でADCを起動し、結果のデジタル出力を記録します。この読取り値と理想出力 (通常はゼロ) の間の不一致はオフセット誤差を示します。

ベストフィットライン法: ADCに認識された入力電圧の配列を使用し、対応する出力値のグラフを作成します。線形回帰アルゴリズムを用いてこれらの点を通る直線をフィッティングすることにより、予想されるゼロ入出力からのこの直線の逸脱がオフセット誤差を特徴づけます。

ヒストグラム方式: ADCの入力範囲の中間点付近に既知の定電圧を実装し、相当量のサンプルを収集します。このデータセットからヒストグラムを作成すると、平均値が明らかになります。この平均値を入力値と比較することで、オフセット誤差が明らかになります。

オフセット誤差を計算する場合、処理フェーズ中にADCの出力に補正係数を追加することで、ソフトウェアでオフセット誤差を調整して補正することがしばしば可能であることを覚えておくことが重要です。

ゲイン誤差

ゲイン誤差は、アナログ・デジタルコンバータ (ADC) における重大なミスの原因です。ADCシステムが正確かつ確実に機能するためには、その定義、原因、効果、測定技術を理解することが不可欠です。

定義

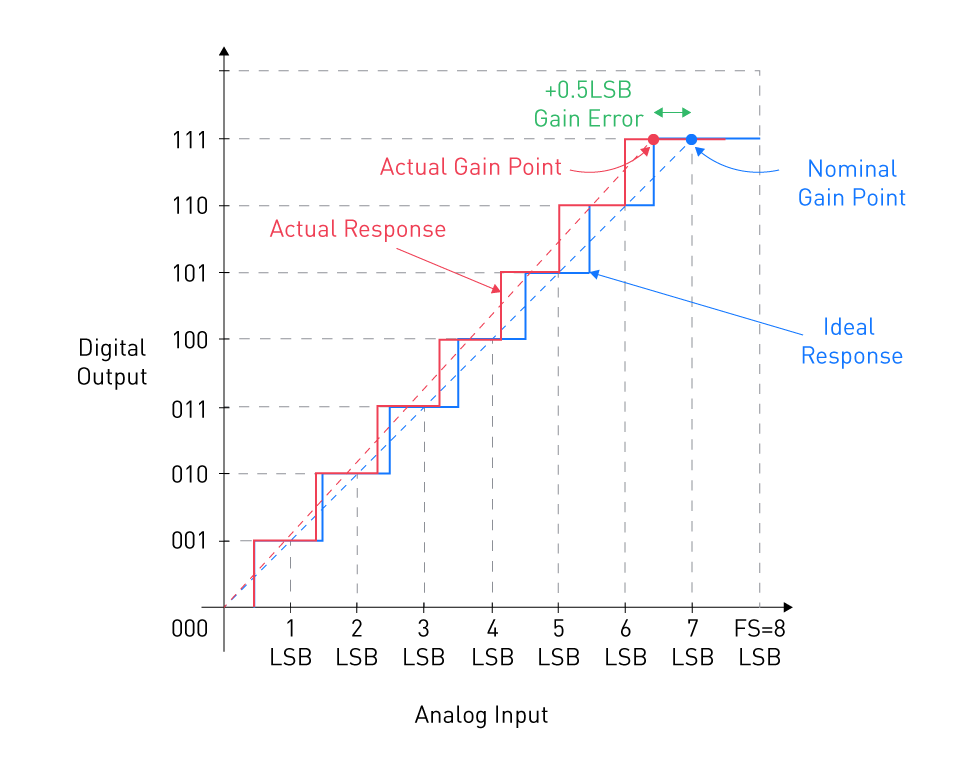

ゲイン誤差はフルスケール誤差とも呼ばれ、ADCの実際の出力スロープと理想的な出力スロープの差です。単純に言えば、ADCの出力が理想的な線形応答に対して圧縮または伸張されるスケーリングミスを表します。わかりやすくするために、ゲインミスを図3に示します。

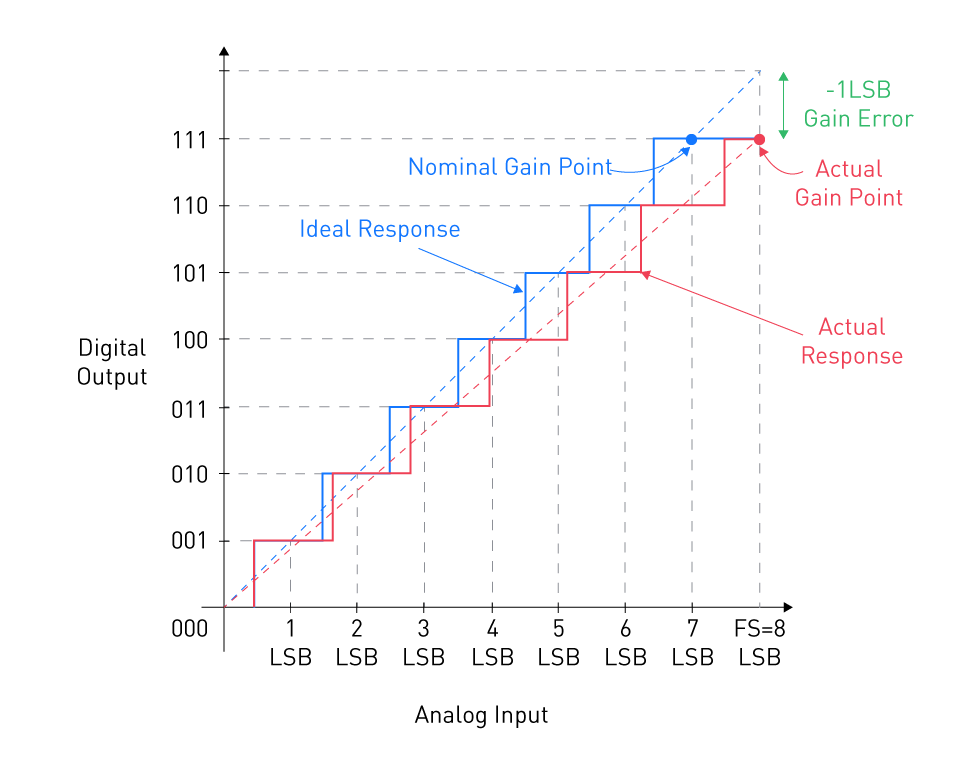

図3 : ゲイン誤差の概念を示すグラフ

ここで、「ゲインポイント」という用語は、前の遷移よりも半LSB上にあるものとします。オフセット誤差が修正されると、予測ゲインポイントと実現されたゲインポイントの間の不一致がゲイン誤差を確定します。

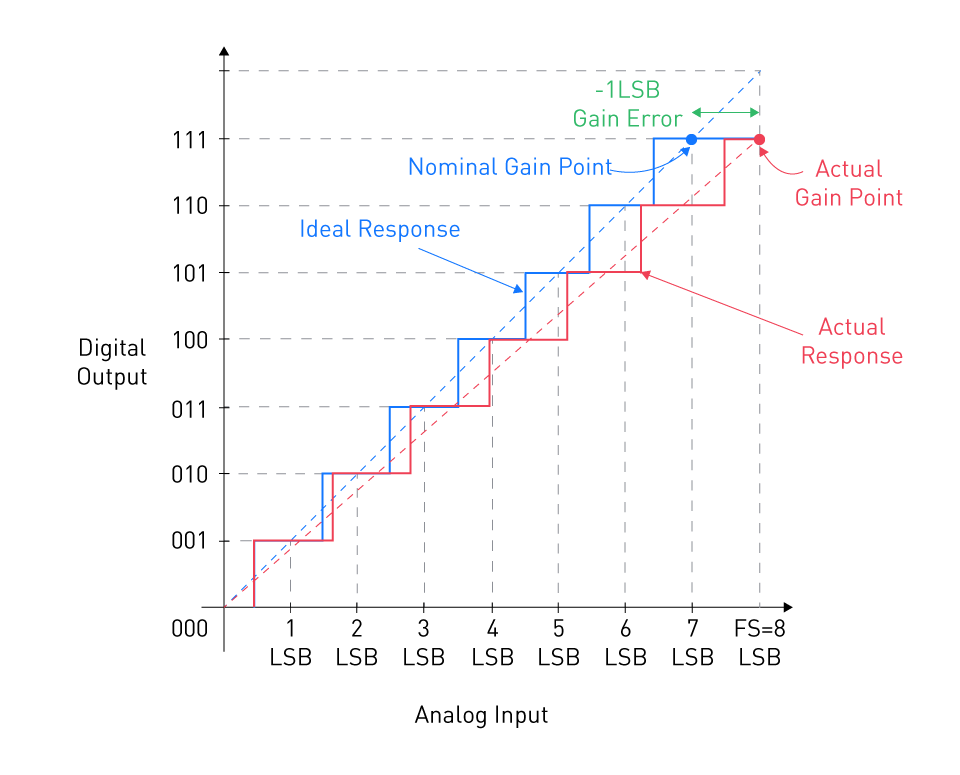

前述の例では、非理想的特性は+0.5 LSBのゲイン誤差を示します。図中のオレンジ色の線は非理想的な応答の線形表現です。測定されたゲインポイントと理論的なゲインポイントの間の相違が実際にシステムの線形モデルの勾配を修正することは明らかです。図4に示すのは、-1 LSBのゲイン誤差を特徴とするADCの応答です。

図4 : -1 LSBのゲイン誤差を持つADCの応答

逆に、ある技術文書では、利得誤差を実際の利得点と理想的なADCを表す線形モデルとの間の垂直方向のずれとして説明しています。図4に示されているシナリオを考える、このアプローチは図5に示されている視覚化をもたらします。

理論的線形モデルは勾配が一貫しているため、結果は垂直および水平の両方の不均衡について一貫しています。

原因

ゲイン誤差の主な原因は次のとおりです。

部品の許容誤差: ADC内のコンデンサと抵抗の許容誤差の変動はゲインに影響を与える可能性があります。例えば、抵抗値の違いは抵抗ラダーネットワークのスケーリング係数を変えることができます。

基準電圧の不正確さ: ADCの入力範囲は主にその基準電圧によって決まります。ゲインの不正確さは、この基準電圧の変化によってもたらされます。

温度変化: オフセットミスと同様に、温度の変化は部品の特性に影響を与え、結果としてADCのゲインに影響を与える可能性があります。

図5 : 実際のゲインポイントとADCの直線モデルとの垂直差としてのゲイン誤差

ADC出力への影響

ADCの出力スケーリングは、入力範囲全体にわたってゲイン誤差の影響を受けます。ゲイン誤差は、連続シフトであるオフセット誤差とは対照的に、入力と出力の比例関係を修正します。これは、相対的な測定や正確な振幅表現が重要であり、入力振幅の不正確な表現をもたらす可能性があるアプリケーションにおいて特に重要です。

ゲイン誤差を測定する方法

ゲイン誤差の理解と定量化は、補償と較正に不可欠です。一般的な方法は次のとおりです。

エンドポイント方式: このアプローチでは、2つの認識された電圧をADCに導入することを必要とします。1つは入力範囲の下限 (通常はゼロ) に、もう1つは上限です。出力コードを測定し、それらを期待値と比較することによって、伝達関数の事実上の傾斜と予想される傾斜の対比としてゲイン誤差を推定することができます。

ベストフィットライン法: オフセット誤差の測定に適用されるのと同様に、ベストフィットライン法はゲイン誤差の決定にも有益であることが証明されています。既知の入力電圧のシーケンスを導入し、出力データポイントに最も一致するラインを設定することにより、このラインの勾配をゲイン誤差を計算するための理想的な勾配と比較することができます。

コード密度テスト: この方法では、ノイズの多い信号がADCに向けられ、かなりの量のサンプルが記録されます。出力コードの普及は非線形な傾向を明らかにし、ゲイン誤差の計算を簡単にします。

ゲイン誤差を定量化する際には、信号処理の過程でADCの出力にスケーリング係数を適用することで補正することができます。

線形誤差

線形性はADCの精度と精度を決定する重要な要素です。ADCの出力が予測された線形の挙動から逸脱すると、線形性誤差を示します。微分非線形性 (DNL) と積分非線形性 (INL) は線形性欠陥の2つの基本的なカテゴリです。

微分非線形性 (DNL)

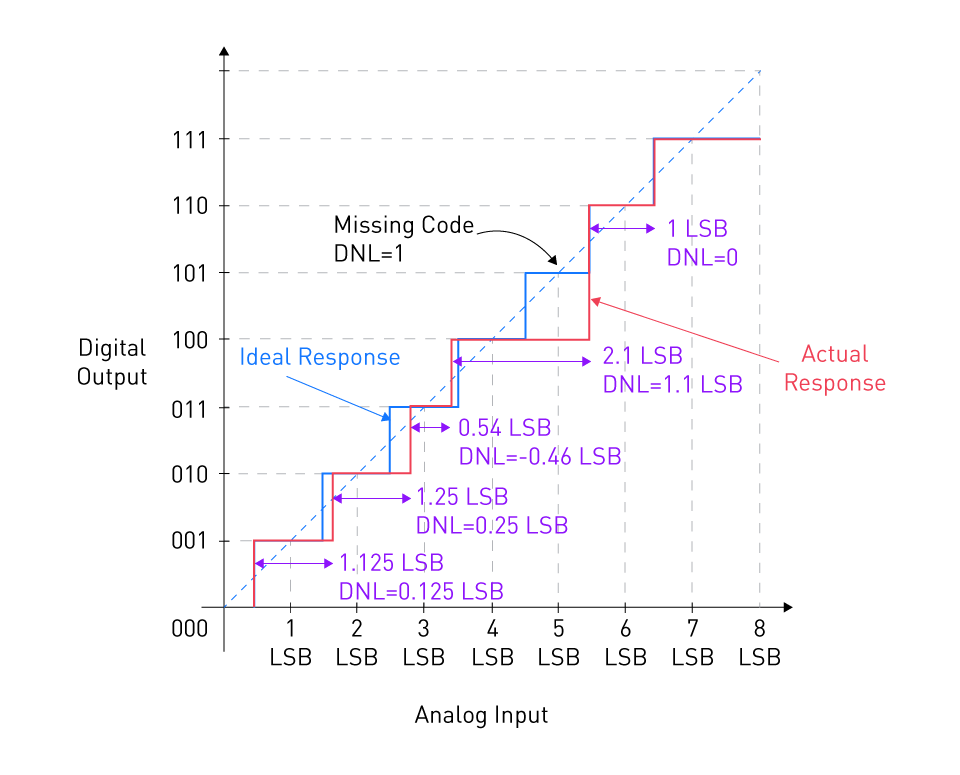

微分非線形性 (Differential Non-Linearity、DNL) は、ADCの伝達関数の事実上のステップ範囲と予測されるステップ幅の間の不一致を測定します。理想的なADCでは、各コード幅は1の最下位ビット (LSB) に等しいはずです。それでも、実際のADCでは、これらのステップの大きさに一定の変動があるかもしれません。図6の紫色の線を考えてみましょう。これは、ステップサイズが均一性を欠く理論的ADCの応答を表しています。この図の中で、コード010は1.25 LSBの幅を示していますが、後続のコードでは0.54 LSBに幅が縮小されています。DNL仕様は、ADCステップが予想される値からどの程度逸脱するかをカプセル化しています。

図6 : DNL誤差の概念を示すグラフ

DNL は、次のように計算できます。

$$DNL(n)=\frac {W(n)-1LSB}{1LSB}$$ここで、Wnはコードnの幅を表します。

例として、図6のコード1 (または001) の場合、次のようになります。

$$DNL(1)=\frac {W(1)-1LSB}{1LSB} = \frac {1.125LSB-1LSB}{1LSB}=0.125$$その結果、コード1の幅は本来あるべき値より0.125 LSB大きくなります。コード3 (または011) の負のDNLは幅0.54 LSBであり、-0.46 LSBです。

潜在的な「ミッシングコード」は-1以下のDNL誤差で示され、これは入力に関係なくADCによって一部の出力コードが生成されない可能性があるという意味です。DNLの誤りはデータをゆがめ、ADCの有効ビット数 (ENOB) を下げることができます。

積分非直線性 (INL)

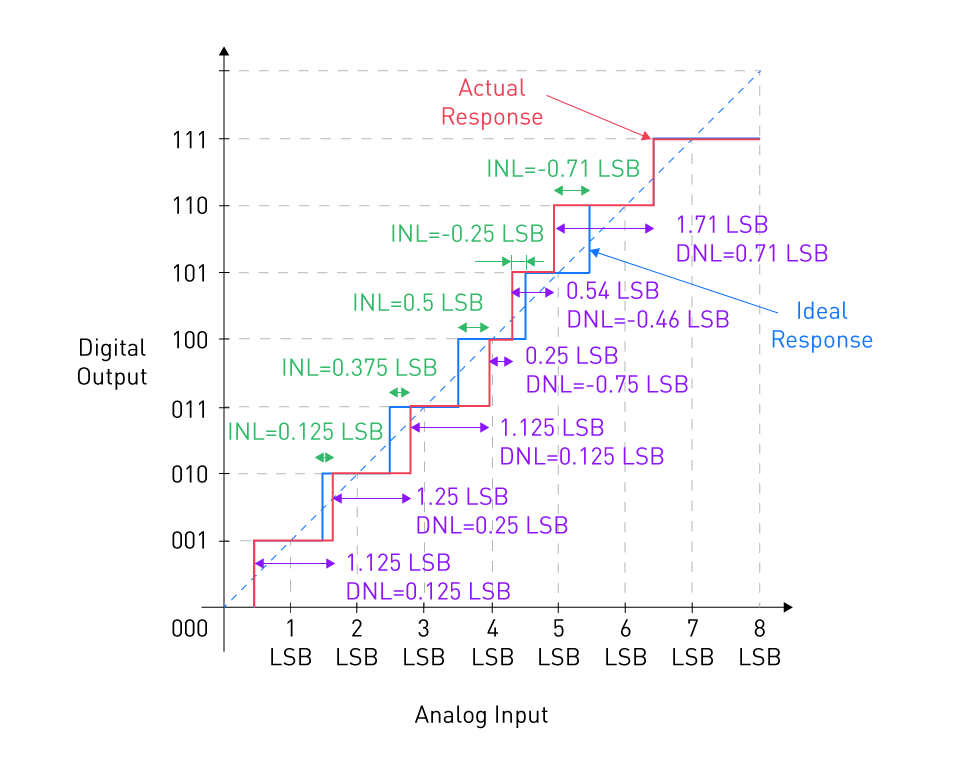

積分非線形性 (Integral Non-Linearity) ADCの伝達関数が線からどれだけ離れているかを定量化します。伝達関数のエンドポイント間に引かれた線、またはベストフィットの直線がこの線の境界になります。INLは、実際の伝達関数とADCの望ましい線形応答との間の偏差を表します。図7の伝達曲線を例として考えます。

図7 : INL誤差の概念を示すグラフ

微分非線形性 (DNL) 仕様は理想値からのステップ幅の逸脱を記述します。しかし、得られる答えは異なるコード間で正と負のDNL誤差がどのように分布するかに依存するため、DNL誤差は理想応答からの伝達関数の逸脱を十分に特徴付けることができません。INL仕様を用いて、コード遷移の理想値からの逸脱を記述することができます。次の式を用いて、コードkのINLを決定することができます。

コードのINLの特徴は次のとおりです。

$$INL(n)=\frac {T_a(n)-T_{ideal}(n)}{1LSB}$$ここでTa(n)とTideal (n)はそれぞれコードn-1からnへの最適および理想的な遷移を示します。

前述の例では、コード1 (001) からコード2 (010) への実際のシフトは理想的な遷移レベルより0.125 LSB上で起こります。したがって、コード2の積分非線形性 (INL) は、INL(2)=+0.125 LSBとして計算されます。

INLは累積の不一致を包含し、n番目のコードまでのDNLエラーの集計を反映します。詳しく言うと、コード3のINLは、コード1とコード2のDNLの和に対応します。

$$INL(3)=DNL(1)+DNL(2)=0.125LSB+0.25LSB=0.375LSB$$INLの概念は、予想されるシナリオがADCの出力コードと入力電圧の間の線形対応を含む場合に特に重要です。

線形誤差の原因と影響

原因:

部品の不一致: DNLとINLの誤りは、抵抗ラダーの抵抗値またはコンデンサアレイのコンデンサの値の不一致によって発生する可能性があります。

アナログ部品の非線形性: 線形性の誤りは、アンプやADCの他のアナログ部分のようなアナログ部品の非線形性の影響を受けることがあります。

温度と電源電圧の変化: 温度と供給電圧の変化は、部品の値がドリフトする原因となり、線形性の問題の一因となります。

クロックジッタ: クロック信号が変動すると、サンプリングインスタンスも変動し、特に高周波では線形性の問題を引き起こす可能性があります。

影響:

高調波歪み: デジタル化された信号は、ADCの非直線性の結果として高調波歪みを経験する可能性があります。

ダイナミックレンジの減少: 直線性フォルトはADCのダイナミックレンジを大幅に低下させる可能性があります。

分解能の低下: 有効ビット数 (ENOB) はADCのビット数で定義される分解能よりも小さいですが、線形性の問題の結果として減少する可能性があります。

ADCの線形性を保証するには、特に医療機器、オーディオ処理、通信などの高精度アプリケーションでは、DNLおよびINL誤差を特性化し、最小化することが不可欠です。ADCの線形性の欠陥の影響を軽減するために使用される方法には、較正技術、ディザリング、およびオーバーサンプリング技術の適用があります。

量子化誤差

A/Dコンバータ (ADC) 固有の制限は量子化誤差として知られています。これはアナログ信号がデジタル的に表現されるかどうかに大きな影響を与えます。

定義

ADCの有限の分解能は量子化誤差を引き起こし、量子化ノイズとしても知られます。ADCは限られたビット数のアナログ信号を表すため、離散的な範囲の値のみを出力することができます。これには、アナログ入力信号の連続範囲を大まかに表すために一連の離散レベルを使用する必要があります。量子化誤差は、実際のアナログ値と最も近い表現可能なデジタル値との差です。

ADCがビット分解能を持つ場合、量子化誤差Qは数学的に次のように表現できます。

$$Q=\frac {V_{max}-V_{min}}{2^n}$$ここで、VmaxとVminは、それぞれアナログ入力範囲の最大値と最小値です。

信号品質への影響

ノイズフロア: アナログ・デジタル変換プロセス中、量子化の不正確さは量子化ノイズを引き起こします。効果的にノイズフロアを上げ、ADCのダイナミックレンジを低減します。

信号対雑音比 (SNR): 量子化ノイズは信号強度の尺度である信号対雑音比 (SNR) を下げます。nビットADCの量子化ノイズのみによる最大SNRは、次の式を用いて推定できます。

$$SNR_{max}[dB]\approx 6.02 \cdot n+1.76$$この式によると、ADCのビット深度に1ビットを加えると、SNRは約6dB増加します。

高調波歪み: 量子化誤差は、信号にノイズが加わるだけでなく、非線形高調波歪みも引き起こす可能性があります。これは信号の振幅が量子化ステップサイズと比較して小さい場合に特に当てはまります。この非線形歪みによって生成される高調波成分は、元の信号には存在しなかった可能性があります。

実効分解能の低下: ADCの分解能の尺度である有効ビット数 (ENOB) は、量子化ノイズが存在すると効果的に減少します。量子化誤差によって生じるノイズの結果として、ENOBはADCの実際の分解能よりも低くなります。

量子化誤差の影響を軽減するために使用できる方法として、オーバーサンプリング、ディザリング、ADCの分解能の向上などがあります。これらの方法はデジタル化された信号の品質を向上させ、アナログ信号の元の形に近づけることができます。量子化誤差は完全に取り除くことはできませんが、ADCを設計し使用する際にその影響を理解することが重要です。

ノイズ

ADCのノイズの必然性は、変換プロセスの精度と信頼性を低下させる可能性があります。ノイズ源を理解し、それらがADC性能にどのように影響するかを理解することが重要です。

熱雑音

熱運動は伝導体中の電子をランダムに移動させ、熱雑音 (ジョンソン・ナイキストノイズとも呼ばれる) を発生させます。ADCに信号が供給されない場合でも、このノイズはまだ存在します。ノイズの根本的な原因であるため、完全に根絶することはできませんが、効果的な設計方法の助けを借りてその影響を減らすことができます。熱雑音のパワースペクトル密度は以下で提供されます。

$$S=4 \cdot k \cdot T \cdot R$$ここで、Rは抵抗 (オーム)、Tはケルビン (ケルビン)、Sはパワースペクトル密度 (ワット/ヘルツ)、kはボルツマン定数です。

特定の帯域幅 (BW) に対する全体的なノイズ電圧を決定するには、次を使用します。

$$V_{noise}=\sqrt{4 \cdot k \cdot T \cdot R \cdot BW}$$量子化ノイズ

ADCの有限分解能は、前述したように、量子化ノイズを引き起こします。実際のアナログ入力と最も近いデジタル近似の間にノイズが発生します。その結果、デジタル値が不明確になり、不正確になります。熱雑音とは対照的に量子化雑音はランダムではなく、多くの変数に依存し、その一つがADC分解能です。

ADCパフォーマンスへの影響

信号対雑音比 (SNR): ADCのノイズフロアは熱ノイズと量子化ノイズの両方の影響を受け、SNRに影響を与えます。SNRが低いと、ノイズレベルが信号よりも高くなり、特に振幅が小さい信号では情報損失を引き起こす可能性があります。

有効ビット数 (ENOB): ノイズは、有効ビット数 (ENOB) の観点からADCの有効分解能に影響を与えます。ノイズは、ADCが高分解能であっても、正確と見なされるビット数を効果的に低減します。ENOBは熱雑音と量子化雑音などの他の雑音源の両方を考慮した測定です。

ダイナミックレンジ: ADCのダイナミックレンジは、正確に測定できる最大信号と最小信号の比であり、ノイズによって制約されます。ノイズフロアより上で検出できる最小の信号は、ノイズによって決まる下限を持っています。

直線性: 非直線性は、ノイズ、特に量子化ノイズによって変換過程に導入される場合があります。これは入力信号の正確な表現、特に低振幅に影響を与えます。

ノイズの影響の軽減

オーバーサンプリング: ノイズはナイキストレートよりもかなり大きいレートでサンプリングすることでより広い帯域に分散され、フィルタリングを使用して目的の帯域外のノイズを除去することができます。

平均化: 複数のサンプルの平均を取ることはランダムノイズの影響を最小化するのに役立ちます。

高分解能ADCの使用: 分解能が高いADCは量子化ステップサイズが小さくなり、量子化ノイズが減少します。

温度制御: 動作温度を制御することで、熱ノイズは温度に依存するため、熱ノイズを低減することができます。

入力信号の調整: ASフィルタリングのような信号調整技術は、入力でADCに到達するノイズの量を減らすのに役立ちます。

ジッタ

ジッタは、アナログ・デジタルコンバータ(ADC)のサンプリング時に発生する、小さな意図しないタイミングの不一致に関連します。これらの不一致は、偶然の産物でも予測可能なものでもあり、特に高周波信号を扱う場合には、アナログ信号のデジタルレンダリングの精度と健全性に大きな影響を与える可能性があります。本セクションでは、ジッタの説明と原因、およびサンプリング精度への影響について掘り下げます。

定義と原因

ジッタはサンプリングの理想的な点からの偏差として記述されます。理想的なADC設定では、サンプリング・インスタンスは正確な間隔で行われます。しかし、これらのインスタンスは様々な要因のためにわずかな偏差を示す場合があります。連続したサンプリングの間の時間スパンの変動はジッタとして示されます。

ジッタは、いくつかの根本的な原因から発生する可能性があります。

ノイズ: 回路内の乱れは、サーマルノイズ、ショットノイズ、フリッカーノイズのいずれに起因するものであっても、クロック信号のタイミングに変動をもたらし、結果としてジッタを引き起こす可能性があります。

電源の変動: 電源内の振動はデジタル回路の遅延を変化させ、それによってクロック信号のタイミングに影響を与える可能性があります。

クロストーク: プリント回路基板 (PCB) 上のトレース間の意図しない電磁的相互作用は、クロック信号に干渉し、ジッタを引き起こす可能性があります。

位相ロックループ (PLL) の不安定性: ADCがクロック生成または同期のために位相ロックループ (PLL) を組み込んでいる場合、PLLメカニズム内の不安定性がジッタの原因となる可能性があります。

温度変化: 温度の変動はADC内の材料の特性に影響を及ぼし、最終的にクロック信号のタイミングの変化を引き起こします。

サンプリング精度への影響

高調波歪み: ジッタはサンプリングのタイミングに不確実性をもたらし、その結果デジタル化された信号内に高調波歪みを生じさせる可能性があります。この現象は、高周波を特徴とする部品の表現を扱うときに特に顕著になります。

信号対雑音比 (SNR): ジッタの導入は、デジタル化された信号の信号対雑音比 (SNR) に直接影響を与え、それがノイズに寄与し、SNRの減少をもたらします。SNRのこの劣化は、高周波を示す信号を扱うときに特に顕著です。

有効ビット数 (ENOB): ジッタが存在すると、ADCの有効ビット数 (ENOB) が減少します。ジッタが補足的なノイズと歪みを導入すると、ADCが情報を解決できる精度が低下し、ENOBが低くなります。

時間領域測定の誤差: デジタルオシロスコープのような時間領域信号を含む状況では、ジッタは時間間隔と位相相関の測定において不正確さをもたらす可能性があります。これにより、信号のこれらの側面を定量化しようとすると誤差が発生する可能性があります。

ジッタの影響の緩和

低ジッタクロックソースの使用: 水晶発振器のような低レベルのジッタを持つクロックソースを利用することで、ADC内に存在する固有のジッタを効果的に抑制することができます。

適切なPCB設計: 十分な遮蔽や慎重なトレース間隔などの要因を含む綿密なPCB設計手法を採用することで、クロストークと電磁干渉の両方を著しく減少させることができます。これら2つの要因は、システム全体のジッタに大きく寄与します。

サプライフィルタリング: 電源ラインに沿ってフィルタを採用することは、電源電圧の温度変動に有効なアプローチであり、ジッタの低減につながります。

温度の安定化: 制御された温度環境でADCを動作させて温度安定性を確立することは、温度変動に起因するジッタを低減するのに役立つことが証明されています。

アカウントにログイン

新しいアカウントを作成