ADC入門

パイプラインアナログ・デジタルコンバータ (ADC) は、高分解能で高速かつ正確なデータ変換を優先するデジタル信号処理システムにおいて極めて重要な役割を果たします。この準備部分では、パイプラインADCを支える概念と基本原則の基本的な概要を説明します。

パイプラインADCは、代替ADCアーキテクチャでは頻繁にトレードオフになる、優れた速度と分解能のデータ変換を提供する能力で際立っています。この独自性は、変換プロセスを離散的な段階に分割するパイプラインアーキテクチャの採用によって生まれます。これらの各段は、デジタル出力の指定されたセグメントを処理する責任を負います。他のADCに見られる逐次処理とは異なり、パイプラインADCの変換段は並列に動作し、高い変換レートを実現します。

基本的に、パイプラインADCの機能は製造施設内の組立ラインに似ています。製造の様々な段階が組立ラインの異なる部分で同時に起こるように、パイプラインADCは変換手順の異なる部分を同時に処理する個別の段階で構成されます。この並列動作により、パイプラインADCの迅速な変換速度が可能になり、総変換時間は全段階の累積合計ではなく、主に最長段によって影響を受けます。

パイプラインADCのもう一つの特筆すべき特徴は、変換速度に大きな影響を与えずに分解能を調整できることです。この適応性はパイプラインに追加の段を組み込むことで達成され、それによって最終出力への追加ビットに貢献します。変換速度と分解能のデカップリングは、他のADCカテゴリと比較してパイプラインADCの注目すべき利点です。

結論として、パイプラインADCは並列化された処理段階と分解能の拡張性を通じて、高速で高分解能のアナログ・デジタル変換を必要とするシナリオに適した強力なソリューションを提供します。以降のセクションでは、パイプラインADCのアーキテクチャ、機能、メリット、デメリットをより深く掘り下げ、この極めて重要なADCフレームワークを包括的に理解します。

パイプラインADCのアーキテクチャ

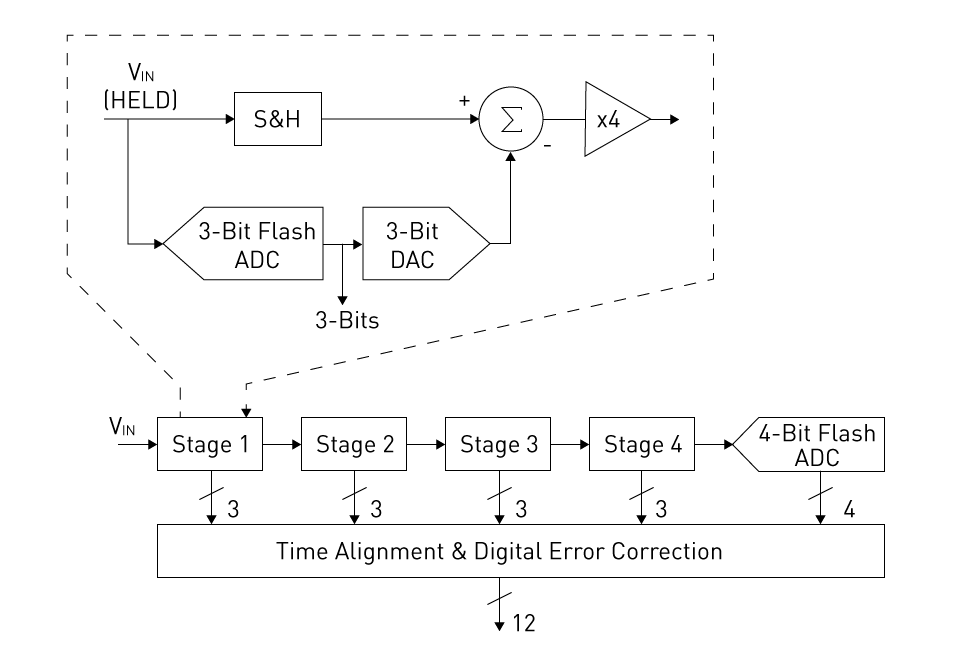

図4 : 12ビットパイプラインADC

段階

パイプラインADCは相互接続された一連の段階として構造化され、カスケード配列を形成します。パイプラインの各段階は、変換プロセスに関係する全体のビットカウントの特定の部分を解決するタスクを引き受けます。最終段階を除いて、各段はサンプルおよびホールド回路、サブADC、残差アンプ、デジタル誤り訂正回路などの部品を含みます。各段からの出力は次の段階に供給され、それによって後続のビットセットの処理を管理します。変換プロセスをより管理しやすいセグメントに分割し、それらを同時に処理することで、パイプラインADCは他のADCアーキテクチャと比較して高いデータスループットを達成することができます。

サンプルおよびホールド回路

パイプラインADC内の各段には、サンプルおよびホールド回路が組み込まれています。この重要な回路は、アナログ入力信号の値を瞬時に捕捉し、変換手順中にその定数を維持する責任を負います。パイプラインADCの動作速度が加速されているため、変換の軌跡全体を通して入力信号の忠実度を維持しながら正確にサンプリングすることが不可欠になります。サンプルおよびホールド回路は、入力が各段で変更されないことを保証し、それによって後続の部品が細心の注意を払って正確な変換を実行することを可能にします。

サブADCおよび残差アンプ

サンプルおよびホールド回路の後、アナログ信号はサブADCに進みます。この低分解能のアナログ・デジタルコンバータ (ADC) は、サンプリングされたアナログ入力をデジタル結果に変換し、同時に数ビットを解読します。得られたデジタル出力は入力のアナログ近似を生成するための基盤として機能します。サンプリングされた元の信号はこのアナログ推定値と対比され、デジタル化を待っている情報をカプセル化した残差を生成します。残差アンプは、この残差を次の段階に通す前に拡大する作業を行います。残差アンプは、次の段階のフルスケール幅を最適に利用するための残差の増幅と、負の負荷衝撃を防ぐための段階の隔離という、2つの主要な役割を果たします。

デジタル誤り訂正

パイプラインADCアーキテクチャの際立った特徴は、変換プロセス中に発生する誤りを修正する能力です。この機能はデジタル誤り訂正回路にあります。残差がパイプラインを通過するにつれて、初期段階からの不一致が伝播する傾向があります。デジタル誤り訂正回路は各段からのデジタル出力を利用して先行段の出力を補正することにより、これらの不一致を打ち消します。この修正には、誤りを測定し、デジタル出力に補償調整を適用することが含まれます。この誤り訂正機構は、特に多数の段階を有するADCにおいて、高分解能の結果を達成するための極めて重要な要素となっています。

パイプラインADCの動作

パイプラインの概念

パイプラインADCは、パイプラインと呼ばれる戦略を巧みに採用し、迅速なアナログ・デジタル変換を可能にします。パイプラインの概念は、多様な段階が同時に変換プロセスの異なる側面に取り組む組立ラインに例えることができます。パイプラインADCでは、アナログ入力信号はより管理しやすいセグメントに分割され、各パイプライン段に変換ビット全体の一部を解読する責任が割り当てられます。各段は自律的かつ同時並行で機能します。変換タスクが完了すると、段は出力を次の段に送信し、入力信号の新しいセグメントの処理を速やかに開始します。このように複数段にまたがる操作の同期化は、多数の変換が適切に並行して管理されるため、スループットと効率が向上します。

変換プロセス

パイプラインADCの変換プロセスをステップごとに掘り下げてみましょう。

サンプリング: サンプルおよびホールド回路は、アナログ入力信号の瞬間値を最初の段でキャッチして保持します。

粗い変換: 初期段階では、サブADCは予備的なアナログ・デジタル変換を実行し、一握りの最上位ビットのみを識別します。

残差の生成と増幅: 第1段の残差アンプは、最初にサンプリングされた信号からアナログに変換されたデジタル出力を差し引くことによって残差信号の生成を取りまとめます。この残差は、未成のままのデータを含みます。その後、この残差は増幅過程を経ます。

残差の通過: 拡大された残差は、さらなる処理が開始されることを意味する次のパイプライン段階へと進みます。 次の各段階: 残差がパイプラインの各段階を通過すると、ステップ2から4の反復的なシーケンスが展開されます。各段階では、変換の付加ビットを徐々に分解し、最終的に残差の精緻化を行います。 デジタル誤り訂正: 同時に、デジタル誤り訂正回路はアナログ段階で発生したかもしれない誤りを訂正する役割を担います。各段から供給されるデジタル出力を利用して、この回路は細心の注意を払って誤りを測定し、整流します。 デジタル出力アセンブリ: 最終的には、すべてのパイプライン段階からのデジタル出力が調和的に収束し、最終的な高分解能デジタル出力を生成します。この結合は、各段階で解読されたビットを正確な位置に整列させ、最終的なデジタル表現を生み出します。 パイプライン遅延: 各サンプルがすべてのパイプライン段を通過する必要があるため、段階数に相当する固有の遅延が存在することを認識することが重要です。この遅延は、特定のサンプルの決定的な出力が利用可能になるまで続きます。 パイプラインADCは、迅速なアナログ-デジタル変換を実現するという領域で卓越した利点を提供します。この能力は主に、変換プロセスを離散化する独創的なパイプライン技術に由来します。各段は対応する段と一体となって動作し、同時に複数のサンプルを扱います。このような並列動作は、パイプラインが適切に準備された後にデジタル出力ワードの一定かつ高速な流れを保証します。デジタル通信や画像処理など、堅牢なデータスループットの必要性が最も重要であるアプリケーションでは、パイプラインADCが好ましい最適な選択肢として浮上することがよくあります。 さらに、アナログ入力信号をより小さなセグメントに分割することと、各段階が選択された数ビットのみを解決するということを義務づけることで、セグメント処理に必要な時間を大幅に短縮することができます。このように、全てのビットが同時に処理される従来の手法と異なり、これは処理時間の短縮につながります。事実上、この部分分割によりクロック速度を速くすることができ、それによってサンプリングレートが向上し、ADCの全体的な効率が向上します。 パイプラインADCが提供するもう一つの注目すべき利点は、分解能に関する固有の拡張性です。この特性は、パイプラインADCの全体の分解能が本質的に各段階で達成された分解能の累積和であるという事実に起因します。その結果、高分解能の追求は、各個別の段階における大幅な複雑さの増大の必要性を回避しながら、段数を増やすことによって達成することができます。 説明のために、各段階で3ビットを上手に解決する、8つの異なる段階からなるパイプラインADCを考えましょう。この構成により、賞賛に値する24ビット分解能が効果的に達成されます。分解能をシームレスに調節するこの能力は、多様なレベルの精度が要求される状況で特に有利です。適切な段数を戦略的に決定することにより、設計者は、手元のアプリケーションによって決定される特定の分解能要件に完璧に一致するようにパイプラインADCを調整することができます。 パイプラインADCに関連する顕著な欠点はレイテンシの概念であり、パイプライン遅延またはレイテンシ遅延としても知られています。このレイテンシは、アナログサンプルの導入と対応するデジタル出力の利用可能性との間に存在する時間的ギャップを具現化しています。この遅延の起源は、入力信号が最終的なデジタル出力に到達する前に一連の段階を通過する固有のパイプラインアーキテクチャまでさかのぼることができます。各段がアナログ入力の指定された部分の処理を行うので、同時に単一クロックサイクルに相当する遅延が発生します。結果として、n段パイプラインADCの場合には、レイテンシはnクロックサイクルによって消えることなく示されます。 リアルタイム処理を特徴とする領域や、迅速な応答を必要とする制御システム内では、レイテンシの影響が極めて重要な役割を担います。フィードバック制御システムでは、レイテンシの上昇がシステムの安定性の低下を引き起こしたり、急速に変動する入力を適切に追跡することの有効性を損なったりする可能性があります。 パイプラインADCに関連する独特の欠点は、固有の複雑さにあり、特に逐次近似レジスタ (SAR) ADCのような単純なADCアーキテクチャと比べられた場合に顕著です。パイプラインアーキテクチャでは、複数段を設置し、それぞれに専用のサブADC、サンプルおよびホールド回路、残差アンプ、そしてしばしばデジタル誤り訂正モジュールを収容することが要求されます。この組み合わせは部品の数を増やし、レイアウトの複雑さを大幅に高めます。 さらに、各段にわたり細心の較正と誤り修正が必要なことは、設計の複雑さを増大させます。パイプラインADCの性能は、各段内に存在する部品に固有の格差や非線形性の影響を強く受けやすくなります。その結果、精密な設計上の考慮と較正の努力が不可欠であり、精度を高めるために最重要な前提条件になります。 さらに、複雑さの増大は消費電力に影響を及ぼし、高分解能の実装においては重要性が高まる面もあります。結果として、パイプラインADCは特定のアプリケーションにおいて代替ADCアーキテクチャと比較してエネルギー効率が低くなる可能性があり、それによって複雑さと省エネの間の微妙なトレードオフが明確になります。 パイプラインADCは、デジタル通信システムの領域において極めて重要な特定分野を占めています。デジタル通信の分野では、デジタル回路による操作が可能なアナログ信号をデジタルデータに変換することが不可欠です。パイプラインADCの持つ固有の高速変換能力は、広帯域信号の広がりに対応するための優れた能力を示しています。 ソフトウェア無線 (SDR): SDRは無線通信機能をソフトウェアに実装しており、それによって多数の通信規格を実現しています。パイプラインADCは、広帯域無線信号を迅速にデジタルに変換し、リアルタイム処理を可能にするため、SDRアプリケーションにおいて重要です。 ワイヤレス通信: LTE、5G、さらにはその先の領域では、データレートの向上が必須となっており、高速動作と優れた分解能のデュアル機能を備えたADCの導入が必要とされます。このような状況の中で、中〜高分解能と組み合わせて高いサンプリングレートを促進するパイプラインADCの能力は、このようなアプリケーションの緊急性を満たすための最適な候補として位置付けられています。 デジタル画像処理の領域では、高いフレームレートでの高解像度画像のキャプチャが最も重要な状況が生まれます。その中で、パイプラインADCは、現代の画像処理システムに不可欠な高速・高解像度データ変換の厳しい要求を管理することに巧みに対応した、精巧にカスタマイズされたツールとして出現しました。 デジタルカメラ: デジタルカメラの分野では、センサが入射光をアナログ信号に変換することを取りまとめるため、パイプラインADCの役割が重要になります。それらの機能は、高解像度とフレームレートによって特徴付けられる、このアナログ情報からデジタル構造への変化を含みます。この能力は、視覚情報の細心な表現が本質である高精細 (HD) および超高精細 (UHD) システムにおいて特に重要です。 医療用画像処理: MRIやCTスキャナなどの医療用画像機器では、高速かつ高解像度な画像を撮影することが求められています。パイプラインADCにより、これらのシステムはイメージセンサによって生成される広帯域アナログ信号を必要な速度と解像度でデジタル形式に変換することができます。 マシンビジョン: マシンビジョンシステムは、品質管理、仕分け、自動化のための産業用アプリケーションに利用されています。これらのシステムには、正確な評価と選択を行うための適切な解像度を維持しながら、高速で画像を撮影できるADCが必要です。パイプラインADCの特性は、これらのニーズとよく一致しています。 必要な性能特性を達成するために、パイプラインADCの設計はいくつかの側面を考慮しなければならなりません。このセクションでは、重要な設計上の問題とトレードオフについて説明します。 段階数: パイプラインADCの段階数は、分解能、速度、複雑さ、および消費電力に影響を与えます。ステップ数を増やすと分解能は向上しますが、レイテンシと複雑さは増大します。フェーズの数を選択するには、アプリケーションの要件に従ってこれらの側面のバランスをとる必要があります。 段階の分解能: パイプラインADCの精度と分解能は、個々の段階の分解能によって決定されます。各段での分解能が高いため、回路の高度化と高い消費電力が必要になります。分解能と電力効率は相反するものです。 サンプリングレート: サンプリングレートの選択は、エイリアシングアーチファクトを防ぐためにナイキスト基準に準拠する必要があります。それにもかかわらず、より高いサンプリングレートを選択すると、電力使用量と設計の複雑さが増大する可能性があります。この重要な決定を下すためには、必要な帯域幅と特定のアプリケーションの要件を慎重に精査することが重要です。 デジタル誤り訂正: デジタル誤り訂正メカニズムの組み込みは、アナログ段階で生じる不正確さを修正することによって精度を高める可能性を秘めています。それにもかかわらず、この増強は、複雑さと電力消費の増大を犠牲にしています。結果として、設計者は費用と誤り修正の利点のバランスを取らなければなりません。 消費電力: 消費電力の低減の追求は、特にバッテリー駆動デバイスの分野では、依然として賞賛に値する希望です。しかし、低電力化の追求は、ADCの速度と精度に影響を及ぼす可能性があります。設計者は、電力消費と性能最適化の間の均衡を打ち破るという複雑な地形を舵取りすることになります。 レイテンシ: パイプラインADCに固有のレイテンシは、パイプライン構造に起因します。リアルタイムアプリケーションではレイテンシを抑制することが最重要課題ですが、これを達成するには分解能の妥協が必要になる場合があります。 面積とコスト: ADCの物理的なフットプリントは、特に緊密に統合されたセットアップにおいて制限を課す場合があります。より多くの段階や複雑な部品を導入すると、コストが上昇する可能性があります。その結果、綿密な最適化が、空間的制約および財政的考慮と設計を調和させるために極めて重要です。 ノイズと歪み: 設計者はADC性能に対するノイズと歪みの影響を考慮に入れる必要があります。ディザリングのような技術はノイズを管理するために利用できますが、そのようなアプローチは電力使用量と複雑さの点でトレードオフを引き起こす可能性があります。 テクノロジーの選択: CMOS、BiCMOSなどの技術の選択と製造プロセスも非常に重要です。独自のテクノロジーにより、電力効率、速度、統合に明確なメリットがもたらされます。設計者は性能の目的および制限に完全に一致する技術を選ばなければなりません。パイプラインADCの利点

高速変換

分解能の拡張性

パイプラインADCの欠点

レイテンシ

複雑さ

パイプラインADCに適したアプリケーション

デジタル通信

デジタル画像処理

設計上の考慮事項とトレードオフ

アカウントにログイン

新しいアカウントを作成