ADC出力インタフェース入門

アナログ・デジタルコンバータ (ADC) の出力インタフェースは、変換されたデジタルデータをメモリ、マイクロコントローラ (MCU)、デジタル信号プロセッサなどの他のシステム部品に送信するためのチャネルとして機能するため、変換プロセス全体にとって極めて重要です。このセクションでは、出力インタフェースの重要性とインタフェースタイプの選択に影響を与える変数について検討します。

出力インタフェースの重要性

ADCからシステムの後続段への効率的で信頼できるデータ転送は、出力インタフェースに大きく依存します。これは以下の点で非常に重要です。

データインテグリティ: これにより、デジタルデータが間違いや損失なしに送信されることが保証されます。データの破損は、不適切に設計された、または不適切に選択されたインタフェースの結果として発生する可能性があります。

システムの同期: データのサンプリングと送信は、多くのアプリケーションにおいて他のシステム要素と連携することが重要です。多くの場合、この同期に必要なクロック信号やタイミング信号は出力インタフェースから供給されます。

スループットとレイテンシ: ADCの最大サンプリングレート、つまり確実にデジタル化される信号の帯域幅は、出力インタフェースを介してデータが転送される速度に影響されます。インタフェースはデータ可用性レイテンシにも影響します。

消費電力: 出力インタフェースはシステム全体の電力使用量、特にバッテリー駆動アプリケーションに大きな影響を与えます。

拡張性と互換性: 出力インタフェースは、システムが他の部品やシステムとインタフェースしたり拡張したりできるかどうかに影響を与えるかもしれません。規格が変わると、システムの寿命に影響を与える可能性があります。

インタフェースの選択に影響する要因

ADC出力インタフェースの選択は、次のような多数の変数の影響を受けます。

データレートの要件: 低速のアプリケーションはより単純で安価なインタフェースを選択するかもしれませんが、高速のアプリケーションは大きなデータレートを処理できるインタフェースを必要とするかもしれません。

複雑さとコスト: パラレルインタフェースはシリアルインタフェースよりも多くのピンと複雑な配線を必要とする可能性があり、価格と必要なボードスペースに影響を与える可能性があります。

ケーブルの長さと環境: そのノイズ耐性により、ADCと受信部品が遠く離れているか、電気的に騒々しい環境にあるシステムでは、低電圧差動信号 (LVDS) のような差動インタフェースが好まれます。

消費電力: 主電源で動作するシステムではより高い電力消費が許容できますが、バッテリー動作するシステムでは低電力インタフェースを頻繁に必要とします。

標準化と互換性: 使用するインタフェースは、業界によって設定されたいくつかの規格によって、または既にインストールされているハードウェアやソフトウェアとの互換性の必要性によって決定される場合があります。

処理経費: 一部のインタフェースを介した通信の管理には、より大きな処理の諸経費が必要になり、システムパフォーマンスに影響を与える可能性があります。

柔軟性と将来性: 潜在的なシステム拡張やアップグレードがインタフェースの要件をどのように変えるかを考慮することが重要です。

パラレルインタフェース

ADCをマイクロプロセッサやFPGAのような他のデバイスに接続する最も一般的な方法の1つは、パラレル接続です。シリアルインタフェースが単一のデータラインを介してビット単位でデータを送信するのに対し、パラレル接続は多数のデータラインを介して同時に多くのデータビットを送信します。

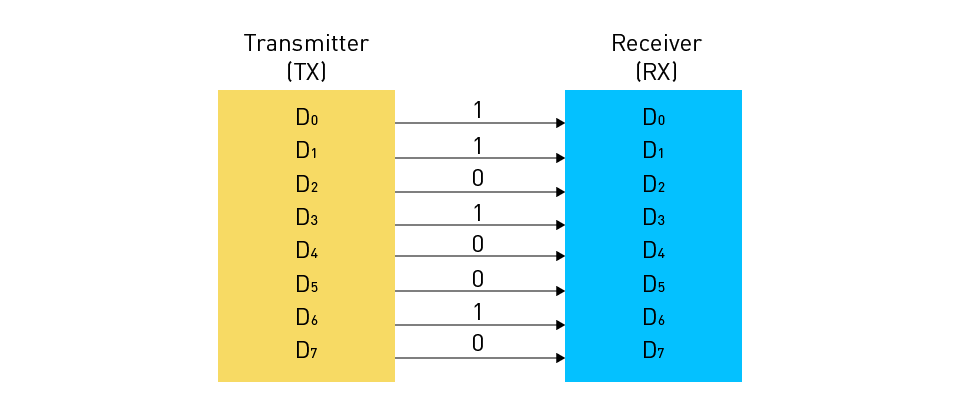

図1 : パラレルインターフェース

基本動作

ADC出力ワードのビットは、パラレルインタフェースを介してそれぞれのデータラインに接続されます。例えば、8ビットADCは8本の異なるデータラインを持ち、それぞれが1ビットの情報を伝達します。変換が完了した後、ADCはこれらのラインを介してすべてのビットを接続されたデバイスに同時に送信します。パラレルインタフェースは一般に、データラインに加えて、データフローのタイミングと方向を調整する「READ」「WRITE」「ENABLE」などの制御ラインをもっています。データの読み込み準備ができたときにデータ準備行が表示されることもあります。

タイミングに関する考慮事項

パラレルインタフェースではタイミングが重要です。データは複数の行をまたがって伝送されるため、全てのビットが同時に宛先に到達しなければなりません。これはデータアライメントとして知られます。データ破損はタイミングエラーの結果として発生する可能性があります。制御信号もデータ信号に対して正しいタイミングでなければなりません。

また、データがADCから受信デバイスに移動するのにかかる時間である伝搬遅延も考慮する必要があります。ケーブル長、キャパシタンス、および部品の電気的特性はすべて、伝播遅延に影響を与えます。

ADCの出力も受信デバイスが読み出すのに十分な時間安定していなければなりません。パラレルインタフェースのタイミングダイアグラムには、どのようにデータと制御信号のタイミングを適切にとるかに関する重要な詳細が含まれています。

長所と短所

利点

- 高スループット: パラレルインタフェースは、複数のビットを同時に送信するため、高いデータ転送速度を実現することができます。

- シンプルなデータ処理: データワード全体を受信装置が一度に受信するため、データ処理がよりシンプルになります。

短所

- ピン数と複雑さ: 追加の制御ラインに加えて、パラレルインタフェースに多くのピン (データの各部分に1つずつ) が必要です。これにより、コネクタの物理サイズが大きくなり、配線が複雑になる可能性があります。

- シグナルインテグリティ: データレートが上昇すると、すべてのラインでシグナルインテグリティを維持することがより困難になります。タイミング・スキューが配線の電気的特性の不一致によって引き起こされる可能性があります。

- 消費電力: より多くのラインで信号を駆動するとき、特に高いデータレートでは、消費電力はしばしばより高くなります。

- 制限されたケーブル長: 長距離信号は時間の経過とともに劣化するため、パラレル接続は短距離で頻繁に使用されます。

結論として、高スループットが不可欠であり、システム設計がピン数、消費電力、ケーブル長に制約されないアプリケーションは、パラレルインタフェースに最適です。しかし、現代のアプリケーションで要求されるデータレートの上昇と前述の欠点により、シリアルインタフェースが新しい設計に頻繁に使用されます。

シリアルインタフェース

ADCは最新システムではシリアルインタフェースを介してマイクロコントローラ、マイクロプロセッサ、または他のデジタルシステムに接続されています。シリアルインタフェースは単一または少数のデータ線を介してビットごとに順次データを送信します。対照的に、パラレルインタフェースは複数のビットを異なる線で同時に転送します。

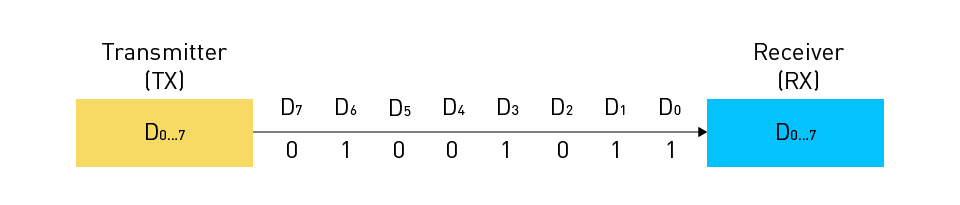

図2 : シリアルインタフェース

基本動作

データはシリアルインタフェースを使用して通信チャネルを介して一度に1ビットずつ送信されます。非同期シリアル通信では独立したクロックラインの代わりに開始ビットと停止ビットを使用しますが、同期シリアル通信ではデータ配信の制御にクロック信号を使用します。

同期シリアル通信では、バイナリデータ伝送用のデータラインと、デバイス間で交換されるデータビットのタイミングを同期するためのクロックラインの2本のラインが使用されます。受信デバイスはクロック信号を使用して適切なタイミングでデータラインをサンプリングします。

一般的なシリアルプロトコル : SPIおよびI2C

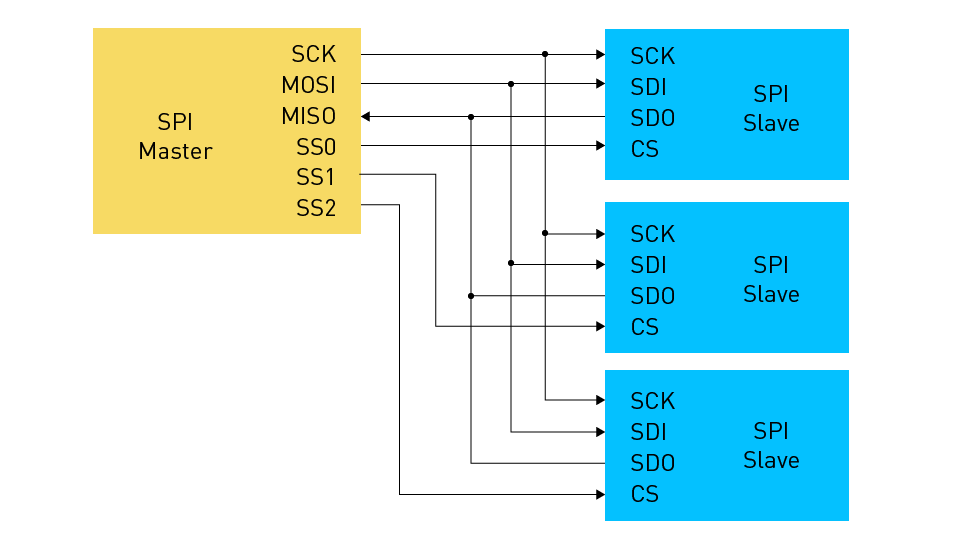

ADCでは、多数のシリアル通信プロトコルが頻繁に使用されます。SPI (シリアル・ペリフェラル・インタフェース) : このマスタースレーブプロトコルは、通常次のものを使用します: MISO (Master In Slave Out)、MOSI (Master Out Slave In)、SCLK (Serial Clock)、および各スレーブデバイスのチップセレクトライン。データは全二重であるため、両方の方法で同時に転送できます。

図3 : 複数のスレーブを使用した4線式SPIバス構成

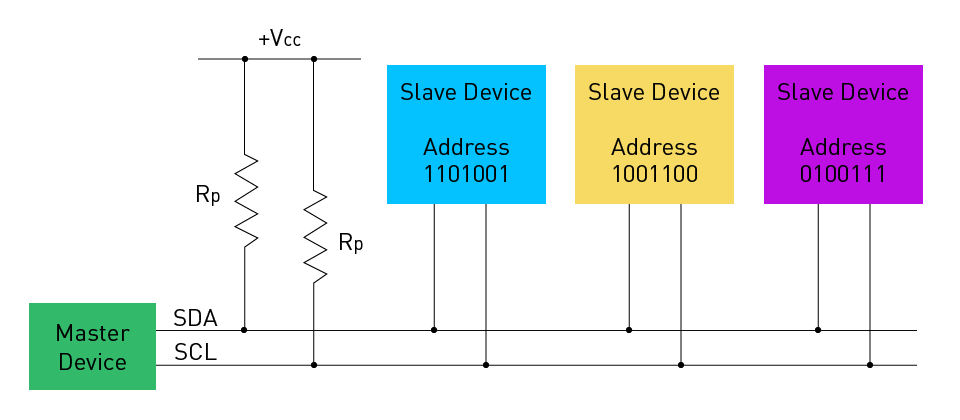

I2C (Inter-Integrated Circuit): これは、2本の配線を介したマルチマスタ、マルチスレーブプロトコルです : シリアルデータ用のSDAとシリアルクロック用のSCL。I2Cバスはデバイスに固有のアドレスを割り当て、複数のデバイスが同じ通信チャネルを共有できるようにします。

図4 : I2Cバス

タイミングに関する考慮事項

タイミングはシリアル通信の効率的な動作にとって重要です。同期通信ではクロック信号が時間を制御するため、クロック周波数はADCと受信デバイスに適していなければなりません。非同期通信では、デバイス間でボーレートとデータフォーマット (スタートビット、ストップビット、パリティ) が一致する必要があります。

さらに、シリアルインタフェースの伝送速度は、データがビット単位で送信されるため重要です。シリアルインタフェースは、高速アプリケーションに必要なデータレートを処理できる必要があります。

長所と短所

- 利点は次のとおりです。

- ピン数の削減: パラレルインタフェースよりもピン数が少ないため、ボード設計が簡単になり、消費電力とコストが削減されます。

- 長い通信距離: 一般的にはノイズ耐性が高く、より長い距離にわたって高品質の信号を送信できます。

- 柔軟性: いくつかのシリアルプロトコルは、同じバスに複数のデバイスを同時に接続することを可能にします。

欠点は次のとおりです。

- 高いレイテンシ: データは逐次的に送信されるため、特にビッグデータワードを使用したり、より遅いクロック速度で転送中にレイテンシが発生したりする可能性があります。

- プロトコルの複雑さの増大: シリアルプロトコル、特にソフトウェアでは、実装がより難しいかもしれません。

少ないピンが必要なアプリケーション、通信範囲が広いアプリケーション、または同じバスに接続されたデバイスの数が多いアプリケーションでは、シリアルインタフェースの恩恵を受けます。アプリケーションの特定のニーズによって、最終的にシリアルインタフェースとパラレルインタフェースのどちらを使うかが決まります。

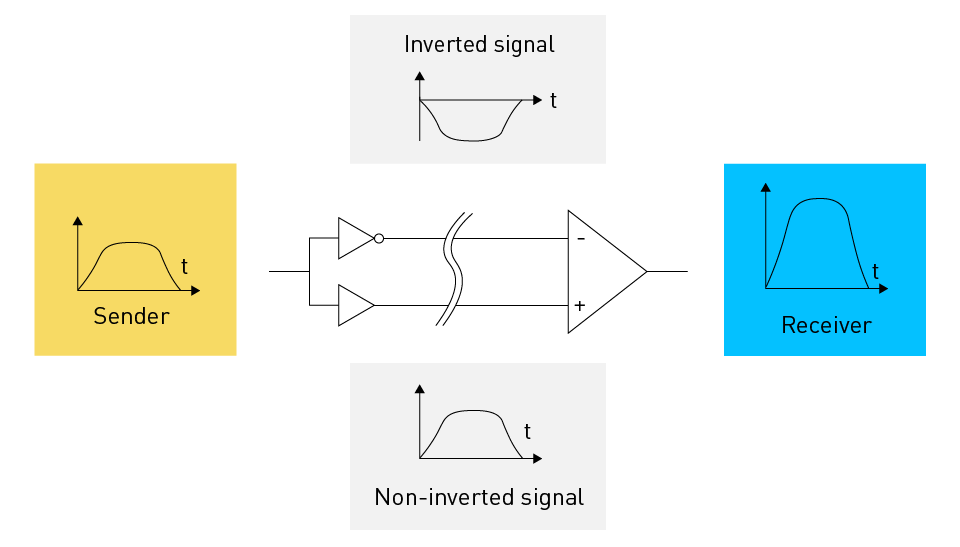

差動および低電圧差動信号 (LVDS) インタフェース

差動信号は、別々のワイヤで送信される2つの相補信号を利用して電気的に情報を送信するために使用される技術です。これはシングルエンド信号とは対照的であり、データは単一のワイヤを介して送信され、一定電圧 (多くの場合グランド) を参照します。よく好まれる差動信号標準はLVDSまたは低電圧差動信号です。

基本動作

情報は、差動信号でペアの配線を介して送信されます。互いの電圧信号の逆方向は、これら2本の線によって伝送されます。一方の配線の電圧は、他方のワイヤの電圧が上昇すると同じ量だけ低下します。逆も同様です。

図5 : 差動信号伝達

インタフェースの受信側は、2つの信号の絶対レベルではなく電圧差を計算します。コモンモードノイズは両方のケーブルに等しく影響し、信号差には影響しないため、これは便利です。この技術は、ノイズや干渉を効率的に除去できるため、電磁干渉 (EMI) が高い領域で使用すると有利です。

LVDSが動作するためには通常数百ミリボルトの非常に低い電圧が必要です。その結果、LVDSは比較的少ない電力で高速なデータ速度で動作することができます。ノイズの多い環境で高速データ転送を必要とするアプリケーションでは、この規格がよく使用されます。

アプリケーション

高速データ通信: 低消費電力と強いノイズ耐性のため、差動信号、特にLVDSは電子機器内と電子機器間の高速データ転送に頻繁に利用されます。

ノイズの多い環境でのADC: LVDSインタフェースは、ADCからのデジタル出力が電気的に大きな状況や長距離で使用されるときに、その完全性を維持するために使用されます。

ビデオ送信: LVDSは特に大型フラットパネルディスプレイや高精細テレビにおいて、グラフィックス処理ユニットからディスプレイパネルへのビデオデータの転送に広く使われています。LVDSの重要性は、表示される画像の品質を維持するために重要な高速データ伝送を保証する能力にあります。

ネットワーク機器: 差動信号伝達は、ツイストペア接続でシグナルインテグリティを確保することが不可欠であるため、ネットワークルータやスイッチで広く使用されています。 産業用制御システム: 電磁干渉 (EMI) レベルが重要な産業環境では、センサ、アクチュエータ、制御ユニット間の信頼性の高いデータ伝送を保証するために、LVDSのような差動信号の利用が一般的です。このアプローチは、EMIの影響を軽減し、産業用制御システムのデータの完全性を維持するのに役立ちます。 システム出力インタフェースは、ADCの出力インタフェースを選択する際に重要です。この決定は、特定のアプリケーションのニーズやシステム設計の制限など、いくつかの変数に基づいて行う必要があります。賢明な選択は、性能、信頼性、および手頃な価格、信頼性、およびコストを最大化するのに役立ちます。 データレートとストレージ: デジタル信号処理や高精細ビデオなどの高速アプリケーションを扱う場合、高いデータレートを効果的に処理できるため、パラレルインタフェースが好まれることがよくあります。一方、センサデータロギングのような低速アプリケーションには、シリアルインタフェースの方が適しています。 伝送距離: データを長距離で伝送する必要がある状況では、LVDSのような差動インタフェースによって提供されるノイズ耐性が好ましい選択になります。シリアルインタフェースは適度に長距離の場合にも実行可能なオプションですが、パラレルインタフェースは一般的に短距離に制限されます。 騒音の多い環境: ノイズ耐性が重要な電気的ノイズの多い環境では、LVDSのような差動信号の実装が非常に効果的です。ノイズの少ない環境では、シリアルまたはパラレルインタフェースを使用できます。

消費電力: 電力効率を優先するアプリケーションは、I2Cのようなシリアルインタフェースを使用することで、パラレルインタフェースに比べて消費電力が少なくなる傾向があるため、メリットが得られます。 同期とタイミング: 正確な同期とタイミングを必要とするアプリケーションでは、優れた同期機能によりパラレルインタフェースが好まれることが多くあります。 ボードスペースと複雑さ: パラレル接続には複数のデータラインが必要となり、ボードの複雑さとスペース要件が増大します。シリアルインタフェースはデータ配線が少ないので、コンパクトで、PCB上で配線するのが簡単です。

コスト: シリアルインタフェースと比較して、パラレルインタフェースは多くの場合、より多くの部品を必要とし、より多くの費用がかかります。価格が重要な考慮事項である場合、シリアルインタフェースはより手頃なオプションかもしれません。 他の部品との互換性: 選択したADCインタフェースが、システムのCPUやマイクコントローラ、その他の部品での使用に適していることを確認することが重要です。これは頻繁にインタフェースの選択に大きな影響を与えます。 拡張性と将来性: システムの拡張とアップグレードの容易さを考慮する必要があります。1つのバス上でより多くのデバイスに対応するために、I2Cのようなシリアルインタフェースの方が拡張性があるかもしれません。 開発およびデバッグツール: 特に複雑なシステムでは、開発ツールの可用性とデバッグのシンプルさが考慮すべき重要な要素です。 結論として、最適なADC出力インタフェースを選択するには、アプリケーションのニーズとシステム設計の限界を注意深く調べる必要があります。要求される性能とコストの基準を達成するシステムは、これらの要素のバランスをとることにより、より信頼性が高く効果的になります。適切なインタフェースの選択

アプリケーション要件

システム設計の制約

アカウントにログイン

新しいアカウントを作成