積分ADC入門

アナログ-デジタルコンバータ (ADC) の基本的な機能は、連続的に変動するアナログ信号を離散またはバイナリデジタル信号に変換することです。さまざまな性能特性を持つ広範なADCの必要性により、多数のアーキテクチャが開発されており、その1つが積分ADCです。

積分ADCは、充電ADCまたはランプADCと呼ばれることもありますが、積分器が上昇したり下降したりするのにかかる時間のタイミングによって信号を変化させるADCの一種です。「積分」という言葉は入力信号を足し合わせることを意味します。設定された時間に入力信号を加算または結合して、入力に一致する値を作成します。そして、この加算値をデジタル版に変換します。

積分ADCの重要な特徴は、時間の経過とともに信号を滑らかにしたり結合したりする機能が組み込まれていることです。これは不必要なノイズを取り払うまたはフィルタリングを助けます。この品質は、例えば、高精度の測定や計測など、信号強度とノイズのバランスが非常に重要であるアプリケーションに適しています。

次のセクションでは、積分ADCの構造について詳しく説明します。それらがどのように機能するか、長所と短所、およびそれらが一般的に使用されている場所を見てみます。まず、積分ADCの3つの主なタイプ、シングルスロープ、デュアルスロープ、およびマルチスロープADCについて説明します。

積分ADCのアーキテクチャ

シングルスロープADC

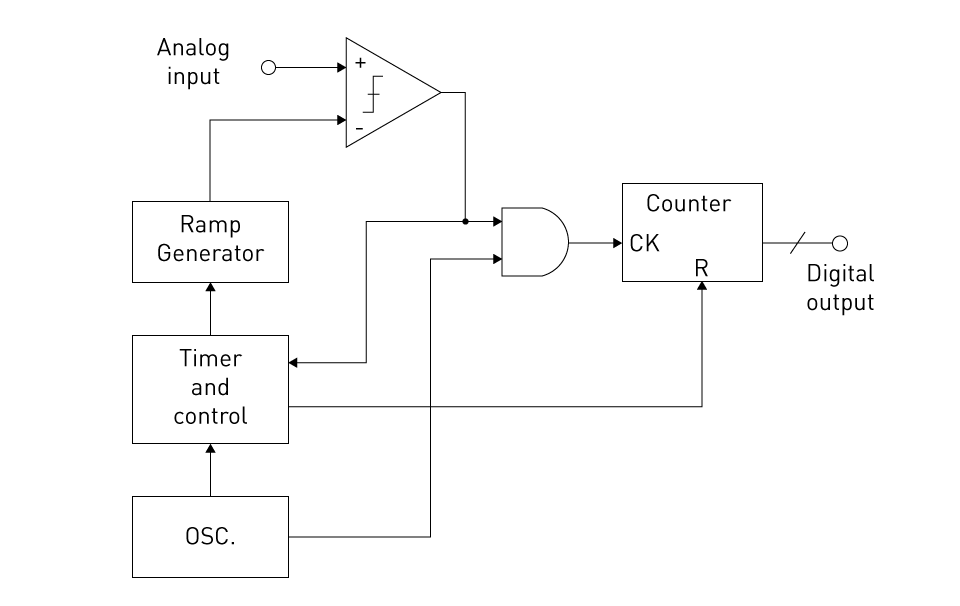

図7 : シングルスロープADC

シングルスロープADCは積分ADCの最も基本的なタイプです。非常に単純な概念に基づいて動作します。インテグレータ、コンパレータ、デジタルカウンタはアーキテクチャの一部です。積分器の出力は、入力電圧が与えられた時間間隔で積分されるため、時間とともに直線的に増加します。積分フェーズの後、カウンタがアクティブになり、積分器はゼロに達するまで一定の速度で放電を開始します。このとき、カウンタの値は入力電圧の大きさと一致します。このADCタイプは基本的なものではありますが、変換のために単一のランプまたはスロープに依存するため、少し遅くなります。

デュアルスロープADC

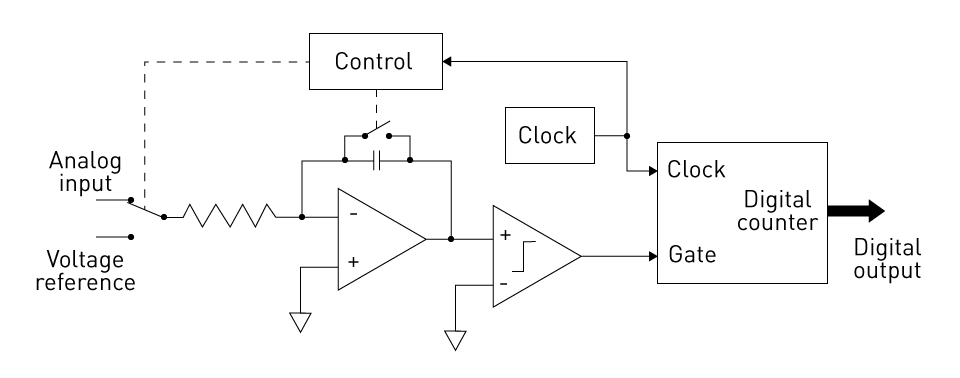

図8 : デュアルスロープADC

デュアルスロープADCは、精度とノイズ耐性の点でシングルスロープADCの強化版です。しかし、アーキテクチャはランアップとランダウンという2つの異なる変換フェーズを持つため、若干複雑です。入力電圧はランアップフェーズ中に一定の期間積分され、積分器出力は上昇します。ランダウンフェーズでは、逆極性の既知の基準電圧が印加され、積分器の出力が減少し始めます。積分器の出力がゼロに戻るのにかかる時間を測定し、入力電圧を計算するために使用します。デュアルスロープADCは、コンパレータとインテグレータのオフセット電圧によって引き起こされるミスを大幅に低減します。

マルチスロープADC

マルチスロープADCは精度を失うことなく速度を向上させる改良です。このADCはデュアルスロープADCと同様に動作しますが、ランダウン段階では複数のスロープまたはランプレートが導入されます。ランプレートが異なるため、粗い調整フェーズと細かい調整フェーズが可能になり、変換時間が短縮されます。粗い調整では、ゼロへのアプローチが速くなるために高速なランプレートを使用し、微調整ではより正確な測定のために低速なレートを使用します。その結果、マルチスロープADCは、シングルスロープADCやデュアルスロープADCよりも高速な変換時間を提供しながら、より高い分解能と精度を提供します。

積分デュアルスロープADCの動作

積分デュアルスロープADCの機能は、ランアップとランダウンの2つの段階に分けられます。各フェーズはADCの動作に不可欠であり、その精度と分解能に影響を与えます。

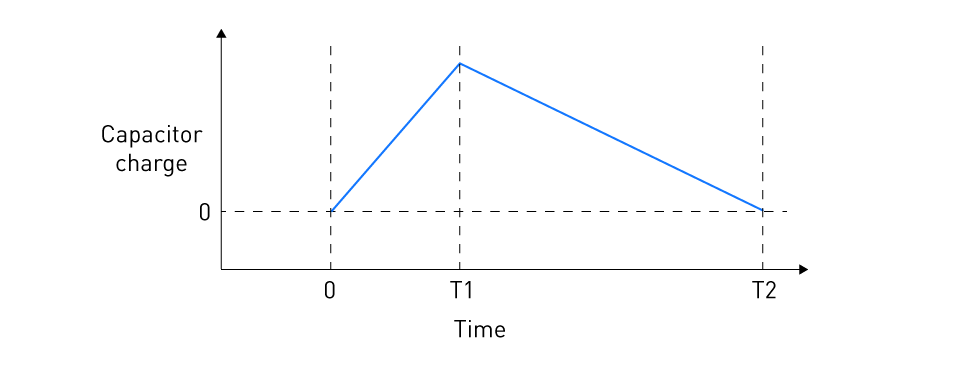

図9 : ランアップおよびランダウンフェーズ

ランアップフェーズ: この段階は入力信号が積分器に設定された時間、導入された時に始まり、通常は正確なタイマで制御されます。積分器の出力は時間の経過とともに着実に増加し、入力信号の大きさに対応するランプを形成します。本質的には、このステップは指定された時間枠で入力信号を足し合わせることであり、積分プロセスのようになります。

ランダウンフェーズ: ランアップフェーズが終了した後、逆極性のリファレンス電圧が積分器に印加されます。その結果、積分器の出力は直線的に減少し始め、ゼロに到達しようとします。この段階では、時刻を記録するカウンタが採用されます。積分器の出力がゼロレベルを横切るとカウントが停止し、ゼロクロッシング検出器によって検出されます。このフェーズの間にカウンタによって測定される時間は直接入力電圧を表します。

変換プロセスの長所は、デュアルスロープ技術を介してコモンモードノイズとオフセットを除去する能力です。ランダウン時の正確なタイミング測定は高分解能につながるため、デジタルマルチメータや精密測定機器など、高精度を必要とする作業に適しています。

積分ADCの利点

積分ADC、特にデュアルスロープADCでは、いくつかの利点が得られ、さまざまな精密測定アプリケーションでの有用性が向上します。

高分解能: ADCを組み込むことの最も重要な利点の1つは、その本質的な高分解能です。変換技術は、卓越した精度で時間を測定することに基づいており、正確できめ細かい測定を可能にします。この高分解能は、入力信号の微細な変化を正確に捉える必要があるアプリケーションで特に役に立ちます。

ノイズと干渉の除去: 積分ADCはノイズ除去に優れており、特にノイズ周波数が積分時間の逆の整数倍に一致する場合に顕著です。この効果的なノイズ低減は、積分中にノイズが平滑化され、測定への影響が著しく減少するデュアルスロープ技術に由来します。

高線形性: 変換が線形ランプと時間測定で構成され、どちらも正確に制御できるため、積分ADCの直線性は並外れています。ADCの直線性が大きいため、出力は入力に直接比例し、多くのアプリケーションで非常に望ましい品質です。

要約すると、積分ADCは、高精度と低速を必要とするタスクに強力なソリューションを提供します。それらは重要な要因である線形性、分解能、ノイズ除去を維持することに優れています。その有用性を十分に活用するためには、その動作とアプリケーションを認識することが不可欠です。

積分ADCの欠点

積分ADCには多くの利点がありますが、その限界も認識することが重要です。この認識は、異なるアプリケーションでそれらを使用するかどうかを決定するときに、十分な情報に基づいた選択を行うのに役立ちます。

低い変換率

積分ADCの大きな欠点は、変換速度が比較的遅いことです。これはそれらの操作の結果であり、積分に続いて逆積分を伴います。この逐次処理は本質的に変換速度を制限します。積分時間が長いと高分解能と優れたノイズ除去が得られますが、変換速度が犠牲になります。このため、ADCの搭載は高速変換アプリケーションには適していません。

変換速度が遅いため、高速の状況やリアルタイムデータ処理が必要な場合にADCを搭載することができない可能性があります。したがって、特定のアプリケーション用のADCアーキテクチャを選択するときは、必要な分解能と変換速度を考慮して、選択したADCが必要なすべての性能要件に一致することを確認することが重要です。

積分ADCは変換率が低いですが、その高分解能、ノイズ除去、および直線性により、速度がそれほど重要ではない低周波数、高精度アプリケーションに適していることがい頻繁にあります。このようなトレードオフを理解することで、より正確で効率的な設計上の決定を行うことができます。

積分ADCのアプリケーション

積分ADCの明確な特徴は、高分解能、堅牢なノイズ、干渉除去、および高い線形性であり、これらの機能を必要とする特定のアプリケーションにとって魅力的な代替となります。

デジタルマルチメータおよび測定機器

ディジタルマルチメータ (DMM) は電圧、電流、抵抗を測定するために使用される柔軟なデバイスです。これらは積分ADCの最も一般的なアプリケーションの1つです。積分ADCの高分解能と高精度は、正しい読み取り値が重要なDMMにとって不可欠です。

デュアルスロープADCは、その有効性により一般的にデジタルマルチメータ (DMM) で採用されています。この方法は、電圧をデジタルデータに変換する簡単で効率的な手段を提供します。測定中のノイズスパイクを無視する機能が組み込まれているため、DMM に適しており、精度が向上します。

積分ADCは、インピーダンスアナライザやLCRメータなどの他の精密測定ツールで広く使用されており、インダクタンス (L)、キャパシタンス (C)、および抵抗 (R) を評価します。これらの装置は、ADCを搭載することによって提供される卓越した線形性と高分解能機能を必要とします。

これらの例では、積分ADCが、正確で信頼性の高い測定を必要とするタスクにどのように適合しているかを浮き彫りにしています。変換速度が速いわけではないにもかかわらず、その精度、ノイズ除去、線形性により、DMMや測定ツールのようなデバイスに適しています。これは、ADCアーキテクチャの選択がアプリケーションの特定のニーズに大きく依存するという考えを明確にしています。

設計上の考慮事項とトレードオフ

ADCを含むシステムを構築する際には、様々な要因や妥協点を考慮する必要があります。

最も考慮すべきことは、アプリケーション固有の要求に合わせることです。例えば、高速変換よりも精度とノイズに対する抵抗が重要である場合、変換速度が遅くなる傾向があるとしても、積分ADCを選択することが最良の決定かもしれません。これは特にデジタルマルチメータや精密測定機器のようなデバイスに当てはまります。

ADCの物理的特性 (消費電力やサイズなど) は極めて重要です。システムを設計する際には、選択したADCが電力の制約と物理的なサイズの制限に適合していることを確認することが重要です。これらの考慮事項は、電池で動作する携帯機器にとって特に重要です。

入力信号の性質も考慮する必要があります。入力信号の変化がゆっくりであるか、ほとんど一定 (DC) である場合、積分ADCの変換速度が比較的遅いことは欠点ではありません。しかし、急速に変化する入力信号を扱う場合、積分ADCの変換速度が遅いことが顕著な制限になります。このような場合、逐次近似やフラッシュADCのような他のADCアーキテクチャの方が適切な選択かもしれません。

もう一つの考慮事項は、予想される周囲条件です。積分ADCは温度変化に対して比較的耐性があり、高い環境ストレスが予想されるアプリケーションに適しています。

コストの面では、積分ADCは一般的に手頃な価格であり、したがってコスト重視のアプリケーションに適しています。しかし、変換速度が遅く、消費電力が高くなる可能性があるため、特定のアプリケーションで他のADCタイプのコストが高くなることを正当化するトレードオフがあるかどうかを評価することが重要です。

アカウントにログイン

新しいアカウントを作成