高速ADC入門

高速ADCの定義

高速ADCは、高速アナログ・デジタルコンバータとも呼ばれ、非常に高速なサンプリングレートで機能するように設計された専用ADCです。「高速」の概念は相対的であり、時間の経過とともに変化する可能性がありますが、現在のところ、サンプリングレートが数百メガサンプル毎秒 (MSPS) から数ギガサンプル毎秒 (GSP) のADCに関係します。

高速ADCは、広帯域幅信号を正確なディテールでデジタル形式に変換する必要がある状況で重要な役割を果たします。これらのADCは、パイプライン、フラッシュ、または時間インターリーブADCなどの異なる構造を使用して、迅速な変換プロセスを実現します。

ブロードバンド通信およびソフトウェア無線における重要性

通信の分野では、「ブロードバンド」という用語は、情報を送信するために使用される広い信号帯域幅を意味します。通信システム内のデータレートの増加に伴い、このデータを表す信号は現在、より広い帯域幅を占有しています。これらのシステムでは、高速ADCが重要な役割を果たし、これらの拡張信号をデジタル形式に変換することで、多様なデジタル処理手法が可能になります。

高速ADCアプリケーションの重要な領域は、ソフトウェア無線 (SDR) にあります。変調やフィルタリングのような特定のタスクをハードウェアに依存する従来の無線とは異なり、SDRはこれらの無線機能にソフトウェアを利用するため、SDRはハードウェアを変更することなく動作を変更することができ、その結果、優れた柔軟性と新しい通信標準への適応性をもたらします。

SDRの分野では、広い周波数にまたがる信号を処理する能力が非常に重要です。高速ADCは広帯域幅信号をデジタル形式に変換し、ソフトウェアがそれらを操作できるようにすることでこれを容易にします。これは、通信技術の急速な進化を考えると特に重要で、ハードウェアの調整なしに新しい標準をシームレスに採用できる能力は非常に有利です。

さらに、SDRは複数の規格や周波数帯域に対応するシステムのアプリケーションが多くあります。そこでは、高速ADCによる広帯域処理が不可欠となり、単一のSDRプラットフォームで様々な規格や周波数幅での通信が可能になります。

主なパラメータと課題

ソフトウェア無線 (SDR) やブロードバンド通信に不可欠な高速ADCには、特別な要件と困難があります。システム性能の最適化の鍵は、これらの要因を理解することです。

サンプリングレート

サンプリングレートは高速ADCの重要な要素の1つです。これは毎秒収集されるサンプル数を指定します。通常、MSPS (メガサンプル/秒) またはGSP (ギガサンプル/秒) で定量化されます。ナイキストシャノン標本化定理は、信号を忠実に再構築するためには、サンプリングレートが少なくともバンドパス信号の2倍の帯域幅か、ベースバンド入力信号の最高周波数部分の2倍である必要があることを定めています。ブロードバンド通信のような高速要件を持つ場合には、サンプリングレートを著しく上げて、広い帯域幅に対応する必要があります。

分解能

分解能は、各サンプルをデジタル的に表現するのに必要なビット数です。高速ADCの代表的な課題は、分解能とサンプリングレートの間の許容可能なバランスをとることです。分解能が高いほど入力信号をより正確に表現できますが、変換プロセスはより複雑であるため、可能な最大サンプリングレートが低くなる傾向があります。いくつかの無線規格で信号品質を維持するためには、SDRのようなアプリケーションである程度高い分解能が必要です。

スプリアスフリーダイナミックレンジ (SFDR)

SFDRは、高速ADCの性能を測定するための重要な基準です。ノイズと不要な信号の中で希望の信号を区別するためのADCの適性を測定します。

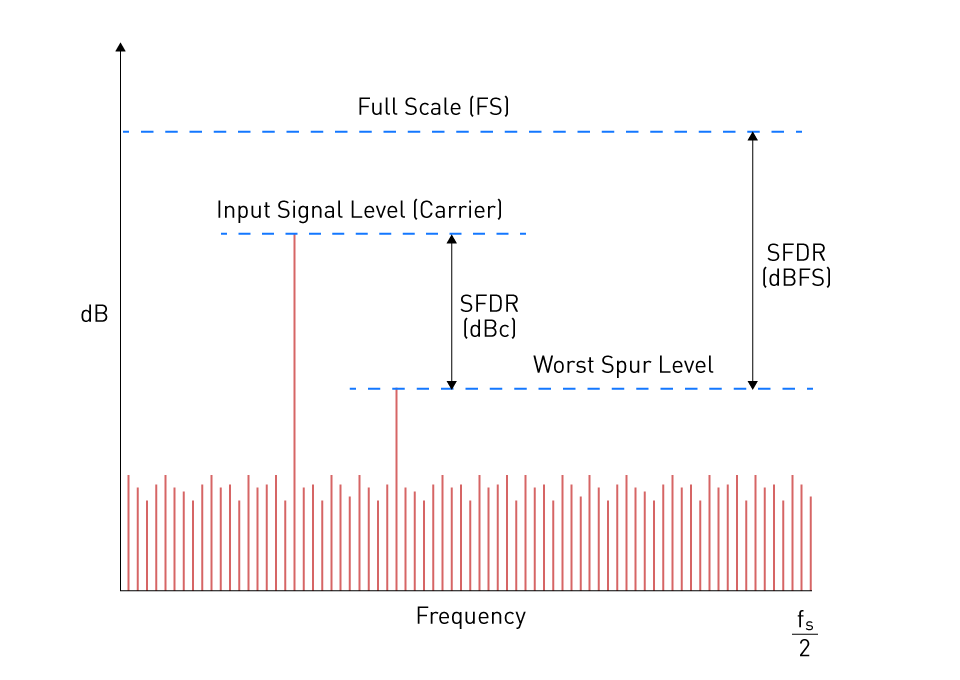

図1 : スプリアスフリーダイナミックレンジ

SFDRは、基本信号の二乗平均平方根 (RMS) 振幅と、周波数領域で次に顕著な意図しない内容物のRMS値を比較することによって決定されます。一般にdBc (搬送波信号振幅に関するデシベル) またはdBFS (ADCのフルスケール範囲に関するデシベル) で表されます。SFDRの重要性は、高速ADC内の非線形性が高調波歪みとスプリアス周波数を誘発できるという事実に起因します。SFDR値の上昇は、望ましくない成分が所望の信号よりも著しく低いことを示しており、これは明確なスペクトルを維持することが重要である広帯域通信システムにおいて非常に重要です。

消費電力

ADCアーキテクチャの複雑さは、サンプルレートと分解能とともに増大し、消費電力の増大につながります。電力効率は多くのアプリケーション、特に携帯機器やバッテリー駆動機器において重要です。高速ADCは、消費電力を最小限に抑えつつ、性能要件を満たすように設計する必要があります。この問題は電力スケーリング、ADCアーキテクチャの最適化、現代の低消費電力半導体プロセスの使用などの方法を利用して解決することができます。

ブロードバンド通信におけるADC

高速ADCは信号をデジタル形式に変換し、効率的に処理して送信することができ、広帯域通信において重要な役割を果たします。

変調および復調における役割

広帯域通信システムは、広い帯域幅でデータを伝送するために多様な変調技術に大きく依存しています。デジタル変調手順の中で、ADCはベースバンド信号をデジタルフォーマットに変換し、伝送用のキャリア信号に変調できるようにします。同様に、受信側では、ADCは復調において極めて重要な役割を果たします。受信した信号をデジタル形式に変換し、その後の処理で初期情報を回復できるようにします。ADCがなければ、広帯域通信システムを介して伝送される膨大なデータ量を変換して処理する作業は、ほぼ克服できないでしょう。

データレートが高い場合の設計上の考慮事項

ADCを実装する場合、ブロードバンド通信システムに共通する高いデータレートを管理するために、いくつかの設計上の考慮事項を考慮する必要があります。

サンプリングレート: 信号を忠実に表現するためには、ADCのサンプリングレートは適切に高くなければならず、通常はベースバンド信号のピーク周波数またはバンドパス信号の帯域幅の2倍です。

分解能: 高速データレートのためには、複雑さと電力使用量を過度に増加させることなくADCが意図した信号品質を確実に管理できるように、分解能を慎重に選択する必要があります。

帯域幅: ADCの帯域幅は、広帯域信号に存在する周波数の配列を処理するのに十分でなければなりません。

線形性: ADCの有効な直線性は、受信信号の品質を低下させる可能性のある高調波歪みを最小化するために重要です。

クロックジッタ: 高速ADCの問題であるクロックジッタは、信号対雑音比 (SNR) を損なう可能性があります。クロックソースは安定していなければならず、低い位相ノイズをもっています。

消費電力: 高いデータレートの作成は、消費電力の増加と相関することがよくあります。特に携帯機器では、性能と電力効率のバランスが重要です。

ケーススタディ : ブロードバンドモデムでの実装

ブロードバンドモデム内に高速ADCを統合するケーススタディを掘り下げてみましょう。現代のブロードバンドモデムは、数百MbpsまたはGbpsに達するデータレートに対応することができます。これを実現するには、高速ADCの存在が必要です。

代表的なDOCSIS (Data over Cable Service Interface Specification) 3.1ケーブルモデムを例にとると、ダウンストリームデータは直角位相振幅変調 (QAM) によって変調されます。ここでは、採用されたADCは、入力信号を正確にサンプリングするのに十分な高いサンプリングレートを持っている必要があり、これはGHzの範囲に広がることができます。さらに、ADCのSFDRは歪みを生じさせずに信号の広いダイナミックレンジに対応するために十分である必要があります。

例えば、現代のDOCSIS 3.1モデムでは、サンプリングレートがGSP数個、分解能が12~14ビット、SFDRが60dB以上のADCを使用することがあります。これにより信号の完全性と品質が維持され、モデムがマルチGbpsのトラフィック速度を処理できるようになります。消費電力を大幅に増加させることなく、より有効なサンプリングレートを得るために、ADCはタイム・インターリーブのような技術を採用することもあります。

ソフトウェア無線 (SDR) のADC

無線通信ネットワークのアーキテクチャは、ソフトウェア無線 (SDR) として知られる革新的な技術によって完全に再設計されました。SDRは非常に汎用性が高く、ミキサ、フィルタ、アンプなどの通常のハードウェア要素の代わりにソフトウェアが使用されています。

SDRの概念とその重要性

変調、復調、信号処理にソフトウェアベースの処理を使用することは、SDRに対応する基本的な考え方です。これは、ソフトウェアを変更するだけで、同じハードウェアを様々な通信規格やアプリケーションに利用できることを示唆しています。SDRは、その柔軟性のおかげで、新しい通信プロトコルや標準に非常に適応しやすく、再構成やアップグレードが簡単です。さらに、SDRは、ソフトウェアによって動的に変更できる多くのモード、複数の帯域、および複数の機能を持つワイヤレスデバイスを可能にします。

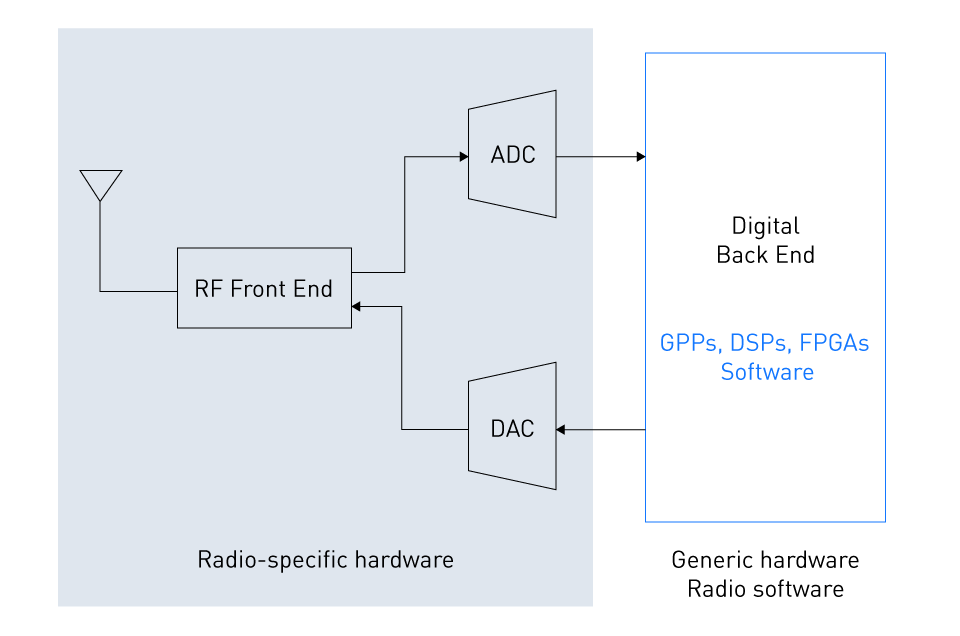

図2 : SDRアーキテクチャ

SDRにおける高速ADCの役割

SDRでADCに供給される前に、アンテナからのアナログ信号は、まずアンプとフィルタを含むフロントエンド部品を通過しなければなりません。これらのアナログ信号はADCによってデジタルに変換され、その後の処理はすべてデジタルで行われます。

高速のADCは、SDRが広い信号帯域幅に対応する能力を保証する上で極めて重要な役割を果たし、さまざまな周波数および規格にわたって効果的に動作することを可能にします。ADCのサンプリングレートは、SDRが扱うべき最高周波数のナイキスト基準を満たさなければなりません。さらに、信号のデジタルレンダリングがその後のデジタル信号処理に十分な精度を保持するためには、高分解能のADCが不可欠です。

SDRに固有の柔軟性は、しばしば広い周波数と変調範囲での動作を必要とします。これにより、高速で高分解能のADCは、精巧なアナログフロントエンド処理を必要とせずにSDRが幅広い信号を管理できるようになるため、ADCの重要性が増加します。

ケーススタディ : 無線通信用のSDRの設計と実装

無線通信用に構築され、Wi-Fi信号とセルラー信号の両方を処理できるSDRについて検討してみましょう。

このアプリケーションのADCは、携帯電話ネットワーク (700 MHzから数GHzまで) とWi-Fi (2.4GHzおよび5GHz) の両方で使用される周波数帯域を処理できる必要があります。この状況では、サンプリングレートが10GSP (ギガサンプル/秒) 以上のADCを使用することができます。

解像度は非常に高速であることに加えて不可欠です。弱い信号に必要なダイナミックレンジと感度を提供するために、14ビットまたは16ビットのADCを選択することができます。

選択されたADCは、より大きなFPGAまたはASICの一部として他のデジタル部品と統合されるかもしれません。SDRで実行されるデジタル処理はFPGAによって処理され、リアルタイムアルゴリズム修正が可能になります。

ADCの目的は、入力信号をアナログからデジタルに継続的に変換することです。FPGAやプロセッサはフィルタリング、復調、デコードなどのプログラムされた機能を実行し、通信規格に従って変更できます。

スマートフォンや異種ネットワークの通信ノードは、このSDRを使用して、Wi-Fiネットワークとセルラーネットワークをオンザフライで切り替えることができます。

アカウントにログイン

新しいアカウントを作成