フラッシュADC

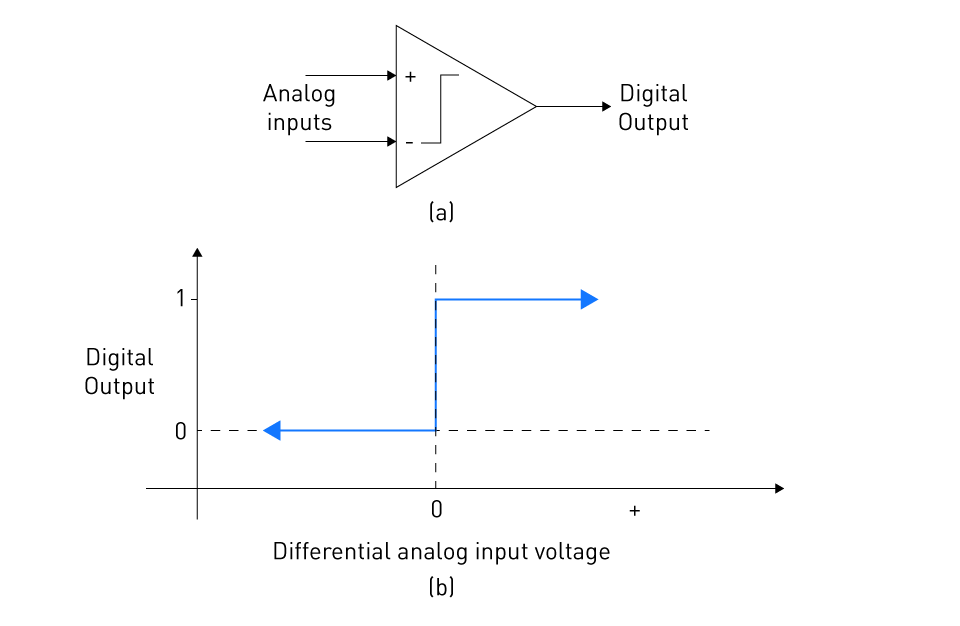

図10 : コンパレータ (a) コンパレータシンボル (b) コンパレータ入出力伝達関数

アーキテクチャ

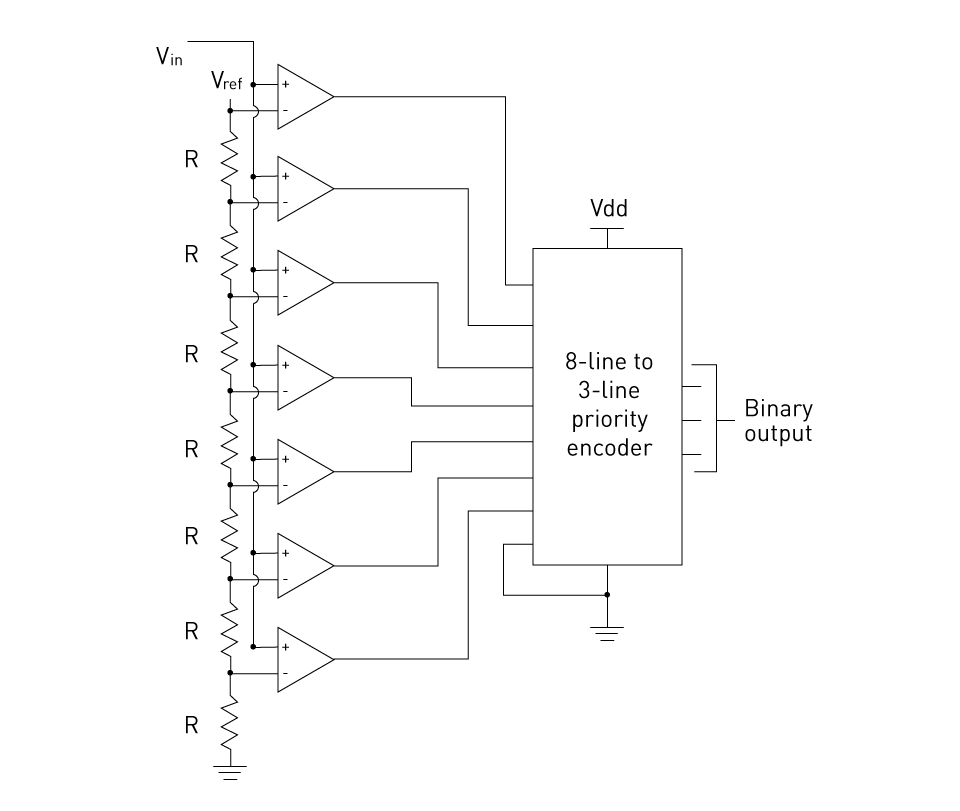

ADCの中でも最も簡単で速いタイプの1つはフラッシュADCであり、一般的にパラレルADCと呼ばれます。エンコーダ回路と複数のコンパレータ回路がアーキテクチャを構成しています。各コンパレータはアナログ電圧入力を基準電圧と比較して評価します。基準電圧は、等しい段階でコンパレータにわたり上昇するようにプログラムされています。その後、エンコーダはコンパレータ出力をアナログ入力のデジタルに対応するバイナリコードに変換します。

図11 : 3ビットフラッシュADC

より具体的には、nビットフラッシュADC用の2n-1コンパレータがあります。抵抗ラダーネットワークを介して、段階的な基準電圧がコンパレータに供給されます。基準電圧は抵抗ラダーによって2nの等間隔ステップに分割されます。

長所と短所

利点:

速度: フラッシュADCは、1ステップで変換を行うことができるため、最も高速なタイプのADCと見なされています。したがって、高周波アプリケーションに最適です。

簡単さ: フラッシュADCのアーキテクチャは非常に単純で、特に低解像度を必要とするアプリケーションではなおさらです。

短所:

拡張性: 必要なコンパレータの量は、ビット数 (分解能) の増加に伴って指数関数的に増加します。例えば、8ビットのフラッシュADCでは255個のコンパレータが必要であるのに対し、12ビットのADCでは4095個のコンパレータが必要です。したがって、高解像度のアプリケーションは実用的ではありません。

消費電力とコスト: コンパレータの数が多いと、費用が増加し、電力使用量が増加します。

サイズ: フラッシュADCは部品の数が膨大であるため、特に高分解能アプリケーションではかなりの量になる可能性があります。

代表的アプリケーション

速度に敏感なアプリケーションでは、フラッシュADCを使用することが多くあります。よく使用されるアプリケーションは次のとおりです。

デジタルオシロスコープ: 高速信号のキャプチャに使用

高周波信号の収集: 例えば、リアルタイムデータ処理が必要なレーダーシステム

ビデオと画像の処理: 大量のデータの並列変換が必要な場合

通信システム: 特にスーパーヘテロダイン受信機がIF (中間周波数) 信号をデジタル形式に変換する場合

SAR ADC

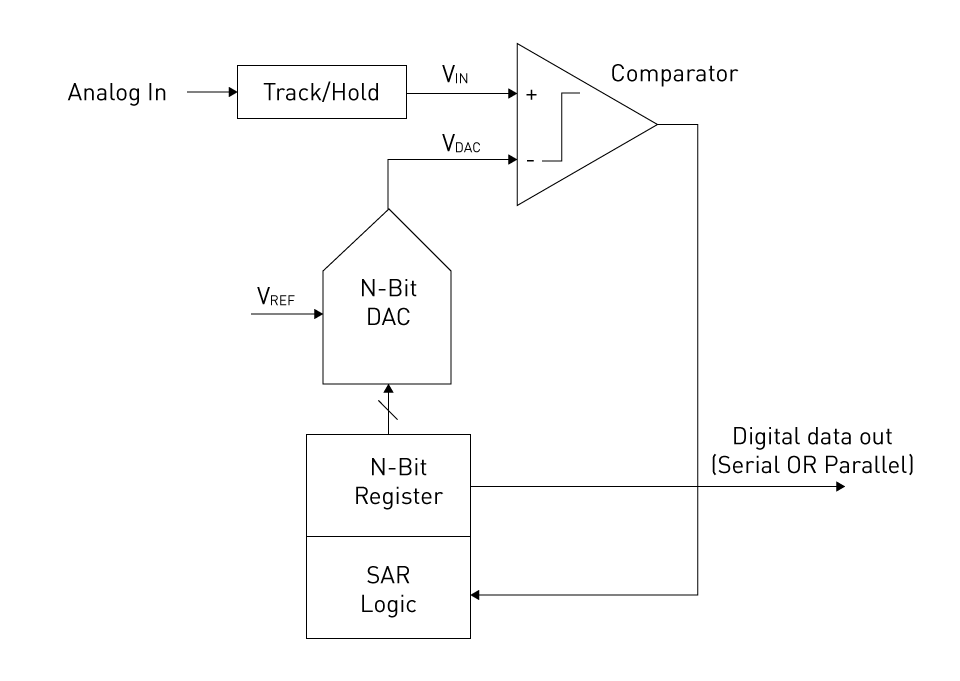

図12: 簡素化されたSAR ADCアーキテクチャ

アーキテクチャ

SARは逐次近似レジスタ (Successive Approximation Register) の略です。ADCとして知られる一般的なADCタイプは、変換速度と複雑さの間で良い妥協点を得ます。サンプル・アンド・ホールド回路、コンパレータ、逐次近似レジスタ、DAC (デジタルアナログコンバータ) が4つの主要な構造要素になっています。

サンプル・アンド・ホールド回路は、変換プロセスの開始時に入力アナログ電圧をキャプチャし、それを保持します。このアナログ電圧に等しいデジタルを見つけるために、次にバイナリサーチが逐次近似レジスタによって開始されます。

まず、レジスタは最上位ビット (MSB) を1に設定し、残りを0に設定し、その値をDACに渡してアナログ電圧にします。コンパレータはこの電圧を入力電圧と比較します。DAC出力が入力電圧よりも小さい場合、ビットはセットされたままになり、それ以外の場合はクリアされます。最下位ビット (LSB) までは、アナログ入力の可能な限り近いデジタルコピーを提供するために、この処理はビットごとに繰り返されます。

長所と短所

利点:

スピードと複雑さのトレードオフ: SAR ADCはフラッシュADCより低速ですが、積分ADCなどの一部のADCより高速です。フラッシュADCよりも必要な部品が少ないため、中~高解像度での使用がより実用的です。

消費電力の削減: SAR ADCはフラッシュADCよりも消費電力が少なく、特にサンプリングレートが遅い場合に使用します。

コンパクトサイズ: SAR ADCは通常、同じ分解のフラッシュADCよりも部品が少なく、物理的に小さくなります。

短所:

超高速に適していない: 逐次近似の手順は数クロックサイクルを必要とするため、本当に高速なアプリケーションには適していません。

変化する変換時間: 一部のシステムでは、変換時間が入力によってわずかに異なるため、タイミングがより困難になる可能性があります。

代表的アプリケーション

データ収集システム: これには、適度な速度と分解能を必要とするセンサインタフェースも含まれます。

マイクロコントローラ: SAR ADCは一般にマイクロコントローラに内蔵され、汎用のアナログからデジタルへの変換が可能です。

オーディオ処理: 高解像度が必要ですが、録音や処理に超高速ではない場合に利用されます。

計測: デジタルマルチメータや各種測定機器で利用されます。

バッテリー駆動機器: SAR ADCは低消費電力要件のため、バッテリー駆動アプリケーションに最適です。

デルタシグマADC

アーキテクチャ

デルタシグマ (ΔΣ) やシグマデルタ (ΣΔ) ADCでは、アナログ・デジタル変換の異なる種類が使われており、オーバーサンプリング、ノイズシェーピング、デジタルフィルタリングなどの手法が追加されています。デシメーションフィルタとデルタシグマ変調器が設計の大部分を占めています。

重要な構成要素はデルタシグマ変調器であり、積分器 (シグマ) と差分動作 (デルタ) を組み合わせたものです。変調器は入力信号を急速にオーバーサンプリングすることで動作し、通常はナイキストレートよりもかなり高いレートで動作します。量子化ノイズはオーバーサンプリングの後に生じるノイズシェーピングによってより高い周波数に押し出されます。

高周波量子化ノイズを除去することにより、デシメーションフィルタはデータレートをより許容可能なレベルに下げます。オーバーサンプリングとノイズシェーピングを組み合わせることで、ADCの分解能とダイナミックレンジを効率的に向上させることができます。

長所と短所

利点:

高解像度と高精度: ノイズシェーピングアプローチを用いて量子化ノイズを広い範囲で成功裏に分散させ、ノイズフロアを大幅に低下させます。このため、デルタシグマADCは高い分解能を達成することができ、精度を必要とするアプリケーションに最適です。

低周波アプリケーションに有効: デルタシグマADCは低周波数でのノイズを大幅に低減する構造であるため、低周波数やDC測定に最適です。

短所:

複雑さの増大: ノイズシェーピングとオーバーサンプリングのアプローチにより、デルタシグマADCはより洗練されたものになっています。コストはこの複雑さの結果として増加する可能性があり、特により高次な変調器の場合に増加します。

レイテンシ: リアルタイム応答を必要とするいくつかのアプリケーションでは、オーバーサンプリング手順とデシメーションフィルタは面倒な遅延を生じさせる可能性があります。

高速アプリケーションに適していない: オーバーサンプリング法は分解能を向上させることができますが、高速信号処理には適していません。

代表的アプリケーション

精密測定機器: これらには、重量計、デジタルマルチメータ、および非常に正確な測定を必要とする他の装置が含まれます。

オーディオアプリケーション: その優れた分解能と低ノイズ特性により、デルタシグマADCは業務用および民生用オーディオアプリケーションの両方でよく使用されます。

産業用プロセス制御: デルタシグマADCは、低周波測定と高精度が不可欠なさまざまな産業用オペレーションに採用されています。

地震および環境モニタリングシステム: デルタシグマADCは分解能が優れているため、環境や地震活動の微小変動のモニタリングに最適です。

パイプラインADC

アーキテクチャ

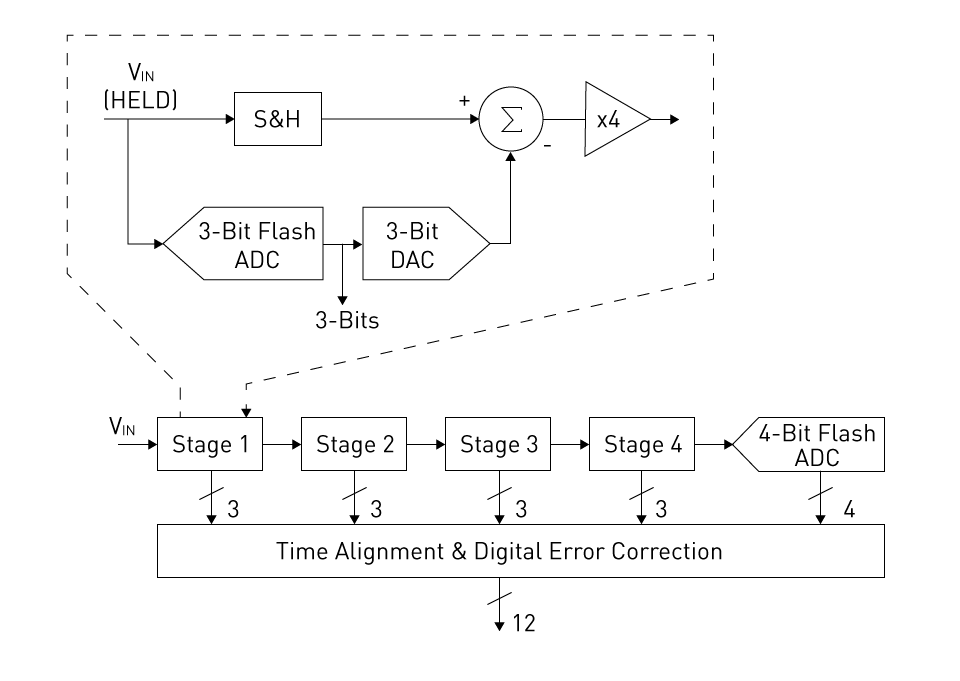

図13 : 12ビットパイプラインADC

アナログ入力をデジタル出力に変換するために、パイプラインアナログ・デジタルコンバータ (ADC) はいくつかの段を持つカスケード構造を採用しています。パイプラインでは、各ステップが入力信号の一部を変換し、残りを次のステージに送ります。パイプラインADCの基本設計はいくつかの段で構成されることが多く、各段には段間利得増幅器、DAC、低分解能ADC (一般にフラッシュADC)、サンプル・アンド・ホールド回路があります。その後、デジタル誤り訂正ブロックが最終段階になります。

第1段は動作中にアナログ入力をサンプリングし、信号の一部をデジタルに変換します。アナログ信号は、段階の変換されたデジタル出力を使用して再作成され、サンプルの元の値から差し引かれ、残渣を残します。この残渣が増幅された後、次の段階でこの手順を繰り返します。パイプラインの各段階からのデジタル出力をすべて組み合わせ、欠陥を補正することで、究極の高解像度デジタル出力が作られます。

長所と短所

利点:

高速変換: パイプラインADCは、パイプラインの各段階での並列処理により高速変換を実現できるため、中~高分解能を高速で必要とするアプリケーションに適しています。

スピードと分解能間でのトレードオフ: 変換速度と分解能のバランスの取れたトレードオフはパイプラインADCによって提供され、多くのアプリケーションに対して有利です。

短所:

レイテンシ: パイプラインADCは、変換手順が多段階であるため、固有の遅延をもっています。変換が完了する前に、サンプルは各段階を通過しなければなりません。

複雑さと消費電力: SAR ADCのような他のADCアーキテクチャと比較して、多段アーキテクチャはより洗練されており、より多くの電力を消費します。

代表的アプリケーション

電気通信: 中間周波数 (IF) 信号をデジタル形式に変換するために、通信システムではパイプラインADCが頻繁に利用されています。

デジタルイメージング: 高速、中解像度から高解像度への変換が必要な場合には、イメージセンサやスキャナなどで使用されます。

高速データ収集システム: オシロスコープのように、分解能をあまり犠牲にすることなくデータを迅速に収集する必要があるアプリケーションで使用されます。

ソフトウェア定義無線: パイプラインADCは、広帯域幅のデジタル化が必要な場合に、ソフトウェア定義無線の重要な部品です。

その他のADCアーキテクチャ - 積分ADC

アーキテクチャ

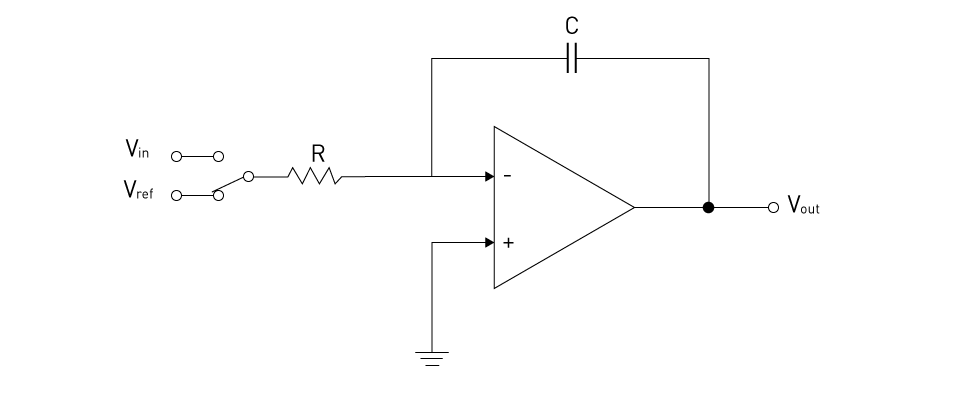

図14 : デュアルスロープ積分ADC

デュアルスロープADC (積分型ADCとも呼ばれる) は、積分器を使用して、あらかじめ設定された時間間隔で入力電圧を平均化します。積分器、基準電圧源、コンパレータ、デジタルカウンタが一般的にアーキテクチャを構成します。既知の基準電圧は、入力電圧が一定時間集積された後、積分器出力がゼロになるまで逆極性で印加されます。入力電圧に比例して、カウンタはゼロを達成するために必要なクロックサイクル数を測定します。

長所と短所

利点:

ノイズリダクション: 積分ADCは、時間をかけて入力を平均化することにより、ノイズと干渉を大幅に最小化します。

高精度: その本質的な直線性のため、正確な測定に適しています。

短所:

変換速度が遅い: その固有の不活発さにより、デュアルスロープ積分は高速アプリケーションには不適切です。

複雑さ: 他の種類のADCと比較して、設計は精密部品の要件により、もっと複雑になるかもしれません。

代表的アプリケーション

デジタルマルチメータ: 速度が高精度電圧の要因ではない場合に使用されます。

重量計: 電子計量計の正確な重量測定に使用されます。

その他のADCアーキテクチャ - タイムインターリーブADC

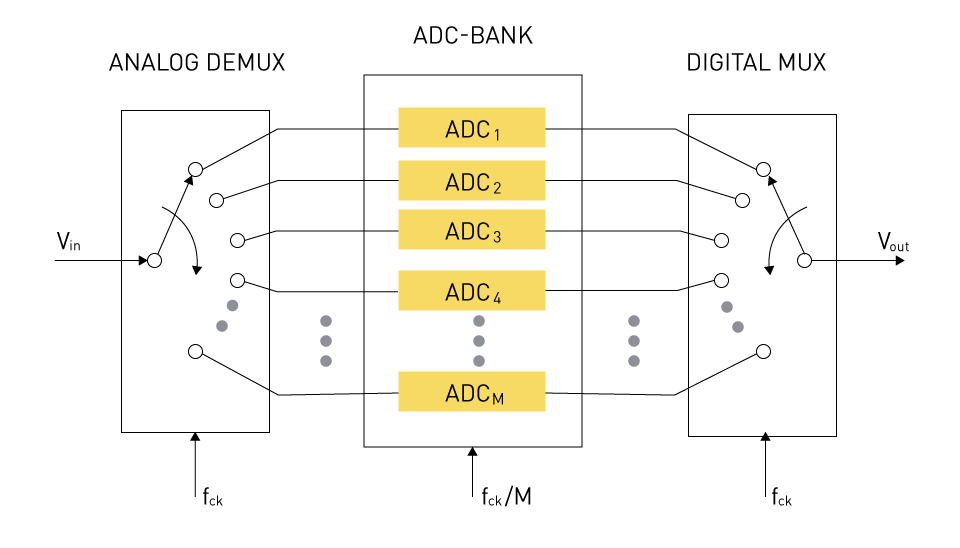

図15 : タイムインターリーブADC

アーキテクチャ

タイムインターリーブADCは多数のADCを同時に動作させ、各ADCサンプリングは少しずつ異なる時間で行われます。この設計では、サンプリングレートはADCの数に比例して効果的に増加します。並列ADCからの出力を組み合わせて、高速で高分解能のデジタル出力を生成します。

長所と短所

利点:

高速変換: タイムインターリーブADCは、複数のADCを同時に使用することで、例外的に高いサンプリングレートに達することができます。

効果的な分解能の向上: アプリケーションによっては、並列設計によって実効分解能を向上させることもできます。

短所:

キャリブレーションの課題: 誤差は並列ADC間の不一致によって生じる可能性がありキャリブレーションが困難になる可能性があります。

複雑さと消費電力の増加: ADCを組み合わせると、回路が複雑になり、エネルギー使用量が増加します。

代表的アプリケーション

高速通信: 高速通信ネットワークに非常に高いデータレートが必要な場合に使用されます。

レーダーシステム: レーダーシステムで信号を迅速に処理するために使用されます。

医療用画像処理: 医療用画像処理システムにおいて、迅速で高品質なデータ収集が不可欠な場合に使用されます。

ADCタイプの比較分析

表1 : ADC比較マトリクス

| フラッシュ (並列) | SAR | デュアルスロープ (ADC) | パイプライン | シグマデルタ | |

| 希望により、この設計を選択: | 消費電力が主な問題ではない場合の超高速 | 中〜高解像度(8~20ビット)、5Msps以下、小型、低消費電力 | DC信号のモニタリング、優れたノイズ性能ICL7106、低消費電力、高分解能 | フラッシュよりも低消費電力、高速、数Msps~100+Msps、8ビット~16ビット | 低〜中速、高精度外付け部品なし、高解像度、同時50Hz / 60Hz除去、デジタルフィルタはアンチエイリアシングの必要性を低減 |

| 変換方法 | N BITS-2N-1コンパレータ、キャップは各ビットごとに2倍上昇する | 二分探索アルゴリズム、内部回路はより高速に動作する | 未知の入力電圧を統合し、既知の基準値と比較する | 小さな並列構造で、各段は1ビットから数ビットで動作する | オーバーサンプリングADC、5Hz〜60Hz除去プログラマブルデータ出力 |

| エンコード方法 | 温度計コードのエンコーディング | 連続近似 | アナログ統合 | デジタル補正ロジック | オーバーサンプリング・モジュレータ、デジタル・デシメーションフィルタ |

| 短所 | スパークルコード / 準安定性、高消費電力、高価、大型 | 速度は5Mspsに制限され、アンチエイリアシングフィルタが必要な場合がある | 変換速度が遅く、精度を達成するために必要な高精度の外付け部品 | 消費電力とレイテンシを犠牲にして並列処理によりスループットが向上 | 高次 (高い4次) - マルチビットADCおよびマルチビットフィードバックDAC |

| 変換時間 | 分解能を上げても変換時間は変わらない | 分解能を上げると直線的に増加する | 変換時間は分解能が1ビット上がるごとに2倍になる | 分解能を上げると直線的に増加する | データ出力レートとノイズフリー分解能間のトレードオフ |

| 分解能 | コンポーネントマッチングでは、分解能は通常8ビットに制限される | コンポーネントマッチングの要件は、分解能が上がるごとに倍増する | 分解能の上昇に伴ってコンポーネントマッチングが増加しない | コンポーネントマッチングの要件は、分解能が上がるごとに倍増する | コンポーネントマッチングの要件は、分解能が上がるごとに倍増する |

| サイズ | 2N-1コンパレータ、ダイサイズ、電力は分解能の上昇とともに指数関数的に増大する | ダイは分解能の上昇に伴って直線的に成長する | 分解能が高くなってもコアダイサイズは大きく変化しない | ダイは分解能の上昇に伴って直線的に成長する | 分解能が高くなってもコアダイサイズは大きく変化しない |

変換速度、分解能、複雑さ、消費電力などのアプリケーションの正確なニーズが、最終的にADC設計の選択を決定づけるものになります。これらの特性に応じて、フラッシュ、SAR、デルタシグマ、パイプライン、積分、タイムインターリーブADCなどのADCの種類を比較します。

変換速度

フラッシュADC: 最も高速な変換速度を提供し、非常に高速なデータ変換を必要とするアプリケーションに適しています。

タイムインターリーブADC: ADCを並列に使用して高い変換速度を実現することができますが、フラッシュADCよりも低速です。

パイプラインADC: 高速なコンバージョンレートを実証しますが、パイプラインの位相によって遅延が発生します。

SAR ADC: 超高速変換を必要とせず、変換速度が適度なアプリケーションに適しています。

デルタシグマADC: オーバーサンプリングとフィルタリングのため、この種の処理は通常より遅くなります。

積分ADC: 2つのスロープで機能するため、このタイプは最も遅くなります。

分解能

デルタシグマADC: デルタシグマADCの優れた分解能により、高精度測定アプリケーションに最適です。

積分ADC: 時間をかけて入力を平均化することで、高い分解能が得られます。

SAR ADC: これらは様々な用途に適応可能であり、良好な分解能を提供します。

パイプラインADC: 設計に応じて、それらは中程度から高解像度を提供します。

タイムインターリーブADC: 分解能は効率的に向上できるが、キャリブレーションの問題が発生する可能性があります。

フラッシュADC: 高分解能には多くのコンパレータが必要とされるため、フラッシュADCの分解能は低いことがよくあります。

複雑さと消費電力

フラッシュADC: 多数のコンパレータによる複雑性が高く、電力使用量が多くなります。

タイムインターリーブADC: 並列ADCが増えるにつれて、複雑さと電力使用量が増加します。

パイプラインADC: 中程度の複雑さ。ステージ数による消費電力のスケーリング。

デルタシグマADC: フィルタリングとデシメーションのため、デルタシグマADCは中程度に複雑であり、消費電力はさまざまです。

SAR ADC: 低消費電力で比較的シンプルな構造。

積分ADC: 低消費電力。比較的単純だが、精密な部品は複雑さを増す可能性があります。

サイズと部品数

フラッシュADC: 考えられる出力値ごとに多数のコンパレータを使用するADCアーキテクチャが一般的に最大です。より大きなビット分解能ではより多くのコンパレータが必要となり、サイズが大きくなります。

タイムインターリーブADC: 複数のADCが並列に動作する場合、サイズもかなり巨大になる可能性があります。ただし、サイズの増加はフラッシュADCのビット分解能の同等の増加よりも小さいかもしれません。なぜなら、個々のADCが単純な形の場合があるからです。

パイプラインADC: 回路はさまざまな段階に分割され、それぞれが変換プロセス全体の異なる側面に寄与するため、パイプラインADCはしばしば中程度のサイズになります。しかし、より高い分解能やより速い性能を達成するためにパイプラインの段階を追加することで、より大きな総サイズが生じる可能性があります。

デルタシグマADC: これらのADCはオーバーサンプリングとフィルタリング技術を使用しているため、サイズは中程度です。大きなオーバーサンプリング比とマルチビット量子化器を使用すると、デジタルフィルタが含まれているときに回路が大きくなる可能性があります。

SAR ADC: SAR ADCは、より少ない部品で動作し、より単純な設計を持つため、一般的に他のタイプよりもアーキテクチャが小さくなります。ただし、より正確なDACとコンパレータに対応するために、SAR ADCのサイズはビット分解能と同じように大きくすることもできます。

積分ADC: 構造が単純なため、これらのADCのサイズが小さくなります。積分器、コンパレータ、カウンタが主要な部品を構成しています。ただし、高精度の抵抗とコンデンサが必要な場合は、サイズが若干大きくなる可能性があります。

表2 : ADCサイズの比較

| フラッシュ | 分解能の向上に伴ってダイのサイズと電力が飛躍的に増加 |

| パイプライン | ダイサイズは解像度に応じて直線的に上昇 |

| シグマデルタ | 分解能が高くなってもコアダイのサイズは大きく変化しない |

| 逐次近似 (SAR) | 分解能が向上しても、コアダイのサイズに大きな違いはありません |

| タイムインターリーブ | 分解能が向上するにつれてダイサイズは半指数関数的に増加する |

| 積分ADC | シンプルなアーキテクチャによる小型のダイサイズ |

代表的アプリケーション

フラッシュADC: オシロスコープと高周波システムはフラッシュADCを使用

SAR ADC: 柔軟、データ収集システムおよびマイクロコントローラで使用

デルタシグマADC: 精密測定とオーディオ処理

パイプラインADC: 無線通信およびビデオ処理用

積分ADC: デジタルマルチメータと重量計量での精密測定

タイムインターリーブADC: レーダーシステムと高速通信

アカウントにログイン

新しいアカウントを作成