タイム・インターリーブADC入門

タイム・インターリーブADコンバータ (ADC) は、増大するサンプリングレートに対する需要に応えるために現れたADC技術の特別に変異した形です。このようなサンプリングレートの向上は入力帯域幅の拡大に相当し、マルチバンド無線システム、空間分解能の向上を特徴とするレーダーシステム、より広いアナログ入力帯域幅を必要とする測定システムなどのアプリケーションが容易になります。本セクションでは、タイム・インターリーブADCの基本原理と動作を明らかにするとともに、高速データ収集の領域での応用を探ることを目的とします。

コンセプトと基本操作

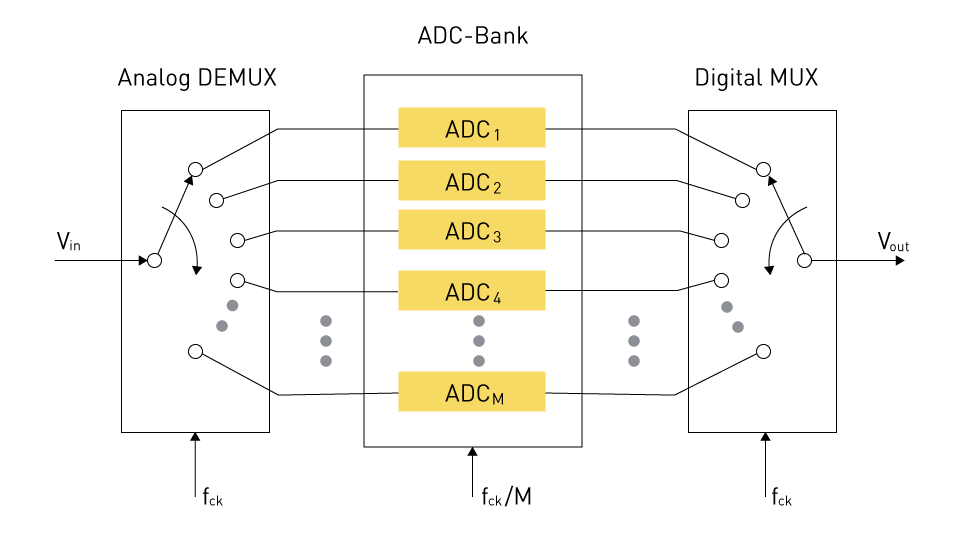

タイム・インターリーブADCを支える前提は、並列に動作するが時間的にずらして動作する多数のADCチャネルの展開です。各チャンネルは、異なる時点で入力信号をサンプリングする役割を担い、それによってサンプリング瞬間を効果的に織り交ぜます。

タイム・インターリーブされたシステムが「M」個のADCチャネルを含む状況を視覚化します。この配置では、最初のADCは信号のサンプルを捕捉します。その後、クロック周期のわずか後に、2番目のADCがサンプルを捕捉し、続いてM番目のADCまで続きます。M番目のADCがサンプリングを完了すると、最初のADCはサンプリングプロセスを再開します。この周期的な配列は持続し、それによって高度にインターリーブされた方法でサンプルを連続的に収集することが可能になります。

図3 : タイム・インターリーブADC

例えば、逐次近似レジスタ (SAR) ADCは、ADCバンク内の個々のADCの1つのタイプになり得ます。

タイム・インターリーブされたADCの有効サンプリングレートは、サンプリングタイミングがインターリーブされているため、各ADCチャネルの有効サンプリングレートよりM倍高くなることがあります。例えば、個々のADCが「f_s」のサンプリングレートで動作する場合、タイム・インターリーブADCシステムの実際のサンプリングレートは「M*f_s」に等しくなります。

高速データ収集でのアプリケーション

タイム・インターリーブADCは、高速データ収集システムの不可欠な構成要素として、特に高いサンプリングレートを必要とする場合に登場します。これらの重要な役割は、さまざまなアプリケーションにまたがっています。

デジタルオシロスコープ: デジタルオシロスコープの領域では、タイム・インターリーブADCを利用して、優れたサンプリングレートを達成することが最も重要な目的です。これらの高速サンプリングレートは、一時的な信号を捕捉するための基本であり、高速で発生する動的プロセスに関する洞察を提供します。

レーダーおよびLIDARシステム: 無線探知測距 (レーダー) システムと光探知測距 (LIDAR) システムの核心は高速データ収集です。このタスクは、物体からの信号のエコーを精査することを含みます。タイム・インターリーブADCは、これらのエコーを鋭い時間精度で捕捉することを容易にし、物体の位置と特性に関する重要な情報を解明します。

通信: ブロードバンド通信システムの領域は、高速データ収集の緊急性が強調されています。これはかなりの帯域幅を持つ信号の受信と操作するために不可欠です。タイム・インターリーブADCは広帯域信号の捕捉への道を開き、その後複雑なデジタル処理を可能にして、さまざまな通信アプリケーションに対応します。

高エネルギー物理実験: 素粒子物理学の実験領域では、センサは非常に高い速度でデータを大量生成できます。ここで、タイム・インターリーブADCは、このような大量のデータを効率的に捕捉するための基盤であり、高速な情報の流れの中で洞察が失われることがないようにします。

アーキテクチャと運用

複数のADCチャネル

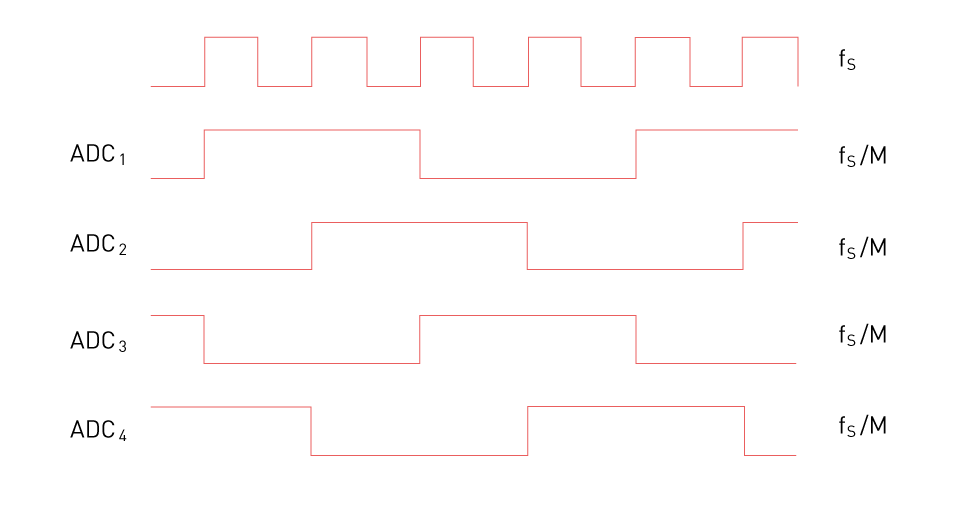

タイム・インターリーブADCの基本アーキテクチャは、複数のADCチャネルの並列動作に基づいています。各チャネルには個別のADCユニットが装備されています。これらのADCユニットは、サンプリングの瞬間をタイム・インターリーブ方式で調整する方法で調整されます。最初のチャネルはt = 0, t = 4T, t = 8Tなどでサンプリングを実行するが、2番目のチャネルはt = T, t = 5T, t = 9Tでサンプリングを実行し、Tは各ADCのサンプリング周期を表します。

図4 : 4チャネルのタイム・インターリーブADCのクロッキング方式の例

この並列構成により、サンプリングレートに総チャネル数を効果的に掛けることができます。例えば、各チャネルがFSのサンプリングレートで動作している場合、Nチャネルを備えたタイムインターリーブADCは、N*FSの実効サンプリングレートになります。

サンプルのタイミングと位相アライメント

しかし、このタイム・インターリーブADCアーキテクチャが最適に動作するためには、すべてのチャネルにわたるサンプリングインスタンスのタイミングを正確に制御することが最も重要です。チャネル間のサンプリングインスタンスのタイミングのずれは、タイミングスキューと呼ばれ、結果として再構成される信号に歪みを引き起こす可能性があります。この歪みはサンプリングインスタンス間の不均一な間隔により生じます。

さらに、タイミングスキューへの対処と併せて、位相の細かなアライメントも同様に重要です。すべてのADC間で正確な位相調整を確保することが重要です。正確な位相アライメントを達成できないと、位相誤差が発生し、信号の忠実度が低下して信号の歪みが生じる可能性があります。

較正技術

較正戦略は、タイム・インターリーブADC内のタイミングスキューと位相誤差の有害な影響を軽減するための重要なツールです。これらの技術は、バックグラウンド較正とフォアグラウンド較正の2つの主要なカテゴリに分類されます。

バックグラウンド較正: この方法は、通常のADC動作中にシームレスに動作します。ADCの性能を永続的にモニタし、タイミングと利得の不一致をリアルタイムで特定して修正します。特に、この較正はリアルタイムで行われるため、通常のADCの動作を中断することはありません。しかし、実装の観点からより高度な複雑さを伴う可能性があります。

フォアグラウンド較正: バックグラウンド較正とは対照的に、フォアグラウンド較正は進行中のプロセスとしてではなく、特定の較正サイクル中にのみ展開されます。その結果、これらの較正フェーズの間、通常のADC動作は瞬間的に中断されます。フォアグラウンド較正は実装が簡単かもしれませんが、ADCの通常動作が定期的に中断されるという犠牲が伴います。

利点と課題

タイム・インターリーブADCは、高いサンプリングレートを達成する能力において大きな利点を提供します。しかし、それらはまた慎重な解決を必要とする特定の課題を提示します。この分節で説明されている2つの基本的な側面は、優れたサンプリングレートを達成することの顕著なメリットと、不一致および較正の複雑さへの対処に伴うハードルです。これらのADCの可能性を最大限に引き出すために、正確さ、精度、高速性能を確保するための要として、効果的な較正技術が用いられています。

高いサンプリングレートの達成

タイム・インターリーブADCを使用することには、通常のADCと比較してはるかに高速なサンプリングレートを達成できるという重要な利点があります。複数のADCチャネルを同時に実行し、サンプリングインスタンスをインターリーブすることにより、全体のサンプリングレートはチャネル数と個々のADCのサンプリングレートを組み合わせた結果になります。例えば、ADCが100メガサンプル/秒 (MS/s)で動作する場合、タイム・インターリーブ設定で10チャネルを使用すると、効果的に1ギガサンプル/秒 (GS/s) のサンプリングレートが得られます。

この高速性能は、デジタルオシロスコープ、高速データ収集システム、ブロードバンド通信セットアップなど、さまざまなアプリケーションで不可欠です。これらの領域では、迅速に変化する信号を最大限の精度で捕捉する必要があります。

不一致と較正の問題への対処

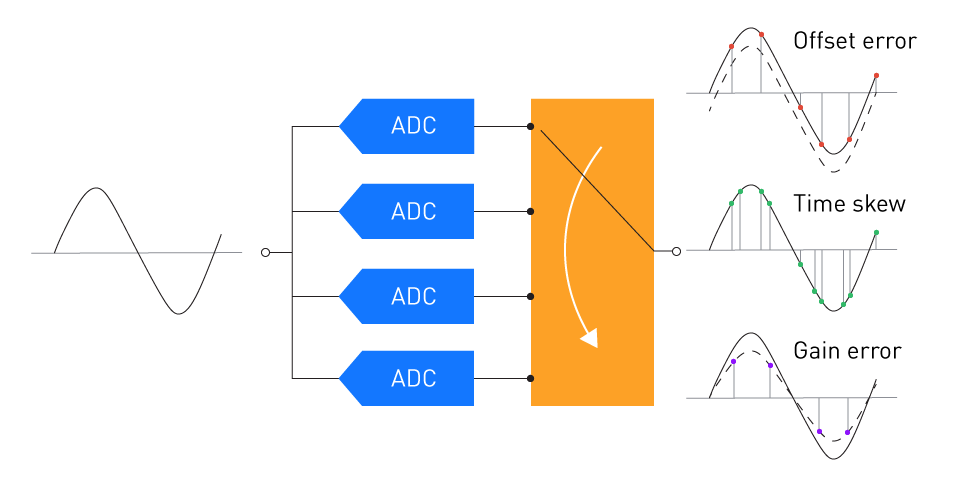

タイム・インターリーブADCのインターリーブ構成は、より高いサンプリングレートを提供する一方で、実際に不一致と較正の必須条件に関連する一連の課題をもたらします。これらの不一致は一般に、ゲインの不一致、オフセットの不一致、タイミングスキューの3つの主要な形で現れます。

ゲインの不一致: 個々のADCチャネルがそれぞれのゲインにばらつきを示す場合、ゲインの不一致が表面化します。この不一致は出力信号内の振幅の不正確さに変換され、捕捉されたデータを歪める可能性があります。

オフセットの不一致: オフセットの不一致は、個々のADCのゼロ点が正確に位置合わせできない場合に発生します。このミスアライメントは出力信号にDCオフセットを導入し、再構成された信号のベースラインシフトに寄与します。

タイミングスキュー: 前述したように、タイミングスキューはADCのサンプリングインスタンスが正確なアライメントから逸脱する状況を表します。この時間的な不一致は、最終的に、結果として再構成された信号内の波形の歪みにつながる可能性があります。

図5 : オフセット誤差、タイムスキュー、ゲイン誤差

前に明らかにした較正技術は、これらの不一致を解決し、それによってタイム・インターリーブADCの完全性と精度を高めるための基軸になります。バックグラウンドとフォアグラウンドの較正方法は、ゲインとオフセットの不一致を補償するために利用できます。しかし、タイミングスキューの課題は、より複雑な介入を必要とします。これには、個々のADCチャネルのサンプリングクロックを細心の注意を払って制御し、タイミングに関して調和されるようにする追加回路が含まれる場合があります。

アプリケーション

タイム・インターリーブADCは、高速データ収集が重要な多くの分野で幅広い用途を提供します。本セクションでは、デジタルオシロスコープ、高速データ収集システム、ブロードバンド通信システムの3つの重要なアプリケーションについて説明します。

デジタルオシロスコープ

タイム・インターリーブADCの顕著なアプリケーションは、デジタルオシロスコープの領域にあります。従来のオシロスコープは帯域幅とサンプリングレートの制約に直面しています。しかし、タイム・インターリーブADCの統合は、変革を起こす変化をもたらします。現在のデジタルオシロスコープは、タイム・インターリーブADCによって支援されており、帯域幅とサンプリングレートを著しく向上することができます。これは、同時に機能する複数のADCチャネルを活用することによって達成され、オシロスコープは定義された時間枠内でより多くのサンプルを蓄積することができます。この機能強化により、急速に進化する信号をより複雑で詳細に描写できるようになります。このレベルの詳細は、信号内の高周波成分を捕捉し、綿密に分析するために不可欠です。さらに、このアプリケーションは、高周波 (RF) 設計、高速デジタルエレクトロニクス、およびシグナルインテグリティの細心の評価などの分野に特別な関連性を持っています。

高速データ収集システム

高速データ収集システムは、航空宇宙、自動車、防衛などの多様な分野で極めて重要な役割を果たしており、一時的な出来事の記録と分析を容易にします。マイクロ秒以下の過渡現象を素早く捉えることの本質は、高速でのデータ取得の重要性を明確に示しています。この場合、タイム・インタリーブADCは高いサンプリングレートのための容量のために主要な選択肢として浮上します。特に、これらのシステムは、一瞬の出来事を注意深く捕捉して解釈する必要があるアプリケーションに最適です。

ブロードバンド通信システム

高速ADCの必要性は、通信システムがより大きなデータレートとより広い帯域幅に移行してていくにつれて増大しています。タイム・インターリーブADCは、将来の5Gやその他のブロードバンド通信システムに不可欠な構成要素です。これらのシステムの広帯域信号は、配信される大量のデータを処理するために、非常に高速な速度でデジタル化されなければなりません。レシーバのタイム・インターリーブADCにより、分解能を犠牲にしたり、レイテンシーを大きくしたりすることなく、広帯域信号をデジタル化することが可能になります。現代のブロードバンド通信ネットワークで必要とされる低遅延、高スループット性能を実現するためには、これが重要です。

ケーススタディ

高速信号解析用のタイム・インターリーブADCの実装

このケーススタディでは、最先端のデジタルストレージオシロスコープ (DSO) の高速信号を解析するために、タイム・インターリーブADCを使用します。タイム・インターリーブADCを備えたDSOは、高速信号解析のアプリケーションに特化して設計されており、広帯域信号を高忠実度かつ高分解能で収集・処理する必要があります。

この実装の目的要件は、帯域幅1GHz、最大サンプリングレート5GS/s、分解能12ビットです。これを達成するために、それぞれ1.25GS/sの最大サンプリングレートを持つ4つのADCをタイムインターリーブされたセットアップで使用しました。

タイム・インターリービングのプロセスを容易にするために、カスタマイズされた集積回路が考案され、次の主要構成要素で構成されています。

- 4つのADCコア、それぞれが1.25 GS/sで動作可能

- サンプルおよびホールド回路 : 専用のサンプル / ホールド回路はADCコアごとにオーケストレーションされる

- クロック配信ネットワーク : これは正確なタイミングを実現するための重要な要素

- 較正回路 : ADCコア全体のタイミングとゲインの不一致を修正するための不可欠なコンポーネント

- マルチプレクサ : 異なるADCコアの出力をまとめ、それらを結合して1つのまとまりのあるデータストリームに統合するコンポーネント

ADCコアの同期は細心の精度で調整されており、各コアは連続するコアから離れて4分の1サイクルでサンプリングを実行します。サンプル・アンド・ホールド回路はアナログ入力信号を捕捉し、その後ADCコアによる量子化のためにチャネル化する作業を任されます。クロック分配ネットワークの重要性は、すべてのADCコアが正確な位相でサンプリングを行うことを保証する役割によって明らかになります。この細心な位相制御は譲れない前提条件であり、これがなければ、結果として得られる出力波形はADCコア全体のタイミングの不一致による歪みが生じます。

タイミングとゲインの不整合を考慮したADCコアの較正は、この設計で遭遇した主要な問題の1つでした。較正が行われていない場合、ADCコア間の不整合により誤ったトーンが生成され、信号対雑音比 (SNR) が低下します。これらの非互換性をリアルタイムで予測し修復するために、デジタル較正回路を設置しました。その結果、部品のばらつきや動作条件の変化に直面しても、出力データストリームは高い忠実度を維持します。

DSOはこの構成を用いて最大1GHzの帯域幅の信号を捕捉し分析することができ、最大5GS/sのリアルタイムサンプリングレートが得られました。このアプリケーションは、時間インターリーブADCが高速で高分解能のデータ解析を提供する能力を実証しました。レーダーシステム、高速データ伝送、科学研究などの重要なアプリケーションにおける広帯域信号表現に最適です。

アカウントにログイン

新しいアカウントを作成