デルタシグマADC入門

デルタシグマ (ΔΣ) ADCは、シグマデルタADCとも呼ばれ、アナログ・デジタルコンバータの範囲において独特の隙間市場を占めています。これらのADCは、その卓越した精度と正確さで広く知られており、オーディオ処理や計装など、精度が最も重要なアプリケーションで注目を集めています。

デルタシグマADCの中核には、ノイズシェーピングとデジタルフィルタリングとの相乗効果があるオーバーサンプリングのパラダイムがあります。オーバーサンプリングの本質は、ナイキストレートよりもはるかに高いレートでアナログ入力をサンプリングすることです。このオーバーサンプリングは信号の精度を向上させることを目的としたものではなく、量子化ノイズをより広い周波数スペクトルに分散させることを目的としています。この拡張されたノイズ分散はその後、重要な部分が関心のある周波数範囲を超えるように形成されます。デジタルフィルタリング (デシメーション) の後、帯域外ノイズを除去しながらサンプルレートを減少させます。

デルタシグマADCは、指定された周波数範囲内の分解能を高めるために、サンプリング周波数を高くすることでバランスをとります。

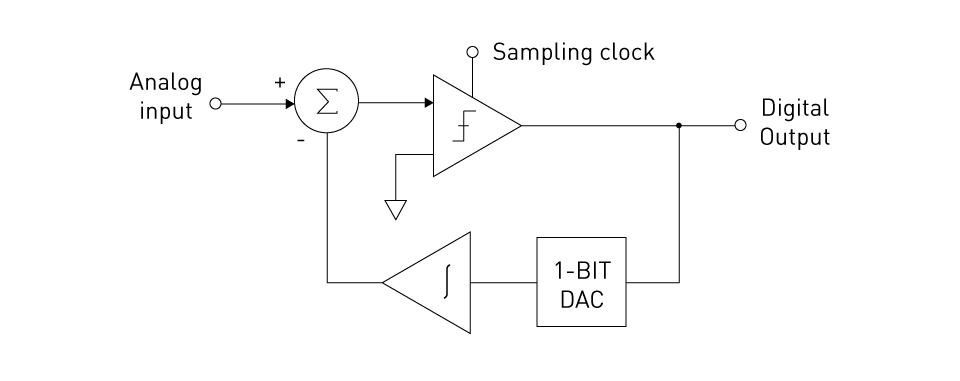

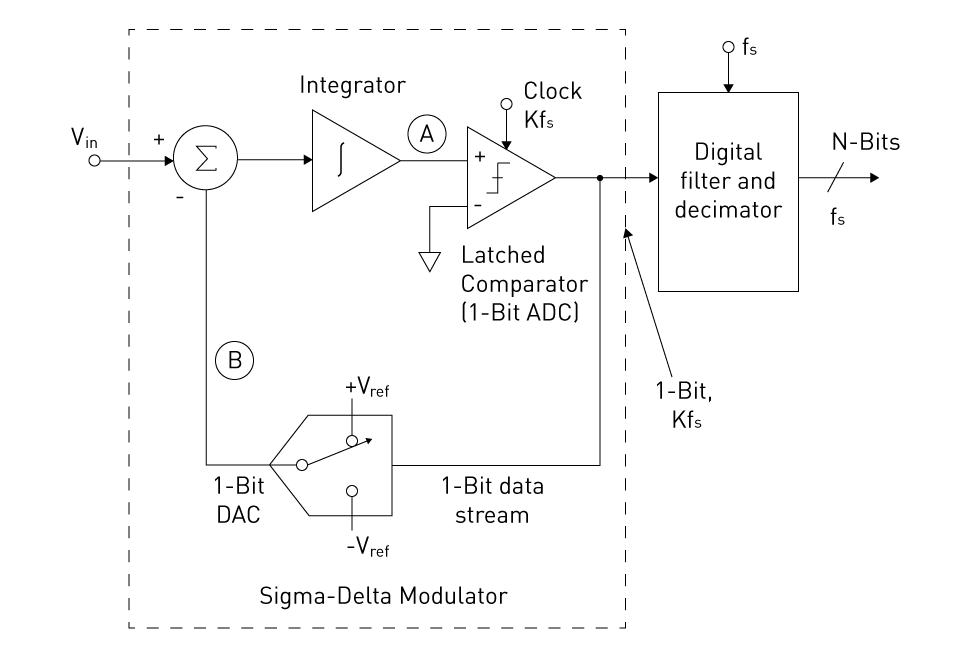

デルタシグマ変調器: デルタシグマADCのアーキテクチャの中心となるのがデルタシグマ変調器です。この変調器は、積分器、コンパレータ、および1ビットのデジタル・アナログコンバータ (DAC) からなる負のフィードバックループに依存しています。積分器は入力信号と1ビットDACの出力の間の不一致を累積します。その後、コンパレータはこの積分出力を基準電圧に対して精査します。結果は1ビットのデータストリームとして生成され、その後1ビットのDACを介してフィードバックされ、反復フィードバックループを編成します。

図5 : デルタ変調器

デシメーションフィルタ: デルタシグマ変調器に続いて、1ビットのデータストリームはデジタルフィルタを介してデシメーションされます。この動作には、データの平均化とサンプルレートの低減を含み、マルチビットデジタル出力が得られます。デシメーションのプロセスは、信号の関連情報をより狭い帯域幅に集中させるのに役立ち、それによって分解能を高め、関心のある指定された帯域内の量子化ノイズを和らげます。

基本的に、デルタシグマADCは、アナログとデジタルの融合を具現化したものです。迅速さと精度の複雑なバランスを巧みに操るオーバーサンプリング、ノイズシェーピング、デシメーションのオーケストレーションによって高分解能変換の熟練技術を実現します。

デルタシグマADCのアーキテクチャ

積分器、1ビットDAC、コンパレータ、デシメーションフィルタは調べるべき4つの主要な部品です。

図6 : 一次シグマデルタ

インテグレータ

デルタシグマADCの第1段階として機能し、積分器は基本的な役割を担います。入力されたアナログ信号を1ビットDACから出力される出力と一緒に取り込み、これら2つの信号間の格差の積分を慎重に計算します。この極めて重要な動作は、デルタシグマADCの運用フレームワークの不可欠な基礎であるエラーフィードバックメカニズムの基礎を築きます。さらに、積分器は信号の変化率に意図的な減衰を導入し、結果として低周波数の場合のコンバータの分解能が増加します。

1ビットDAC

フィードバックループの中心にあるのは、1ビットのD/Aコンバータ (DAC) です。コンパレータによって生成されたデジタル出力を受信し、アナログ波形に変換します。この再構成された信号はその後、積分器内の元の入力と比べられ、それによって量子化誤差の負のフィードバックの形への変換を編成します。デルタシグマADCは、このメカニズムによって誤差を永久に修正することで、高分解能性能の軌跡を描きます。コンパレータ1ビット量子化器として用いられ、コンパレータは積分器の出力から導出されるバイナリ表現を生成する役割を果たします。これは積分器の出力をあらかじめ決められた基準電圧 (1ビットのコンパレータではしばしば0に設定される) と並べることで達成されます。結果として生じる格差のサインを測定することによって、コンパレータは観測された差を示すデジタル出力を発行します。

コンパレータ

1ビット量子化器として用いられ、コンパレータは積分器の出力から導出されるバイナリ表現を生成する役割を果たします。これは積分器の出力をあらかじめ決められた基準電圧 (1ビットのコンパレータではしばしば0に設定される) と並べることで達成されます。結果として生じる格差のサインを測定することによって、コンパレータは観測された差を示すデジタル出力を発行します。

デシメーションフィルタ

デルタシグマADCの動作の最終段階として、デシメーションフィルタが中心となります。このデジタルローパスフィルタは、ノイズシェーピングとレート削減を含む二重の目的を果たします。ADCの最終アービタとして動作し、このフィルタは2つの重要な課題に対処します。デルタシグマ変調器に起因する帯域外量子化ノイズを抑制し、高周波数を強調しながら減衰を調整します。さらに、デシメーションフィルタはオーバーサンプリングされたデータレートを軽減し、より管理しやすいペースに変換します。このプロセスはデシメーションと呼ばれ、精査される周波数帯域の範囲内で信号分解能を向上します。

最後に、デルタシグマADCのアーキテクチャは、インテグレータ、1ビットDAC、コンパレータ、デシメーションフィルタのスマートな組み合わせを介して、アナログ入力信号を高分解能デジタル出力に変換します。各コンポーネントは、特に低周波数および高分解能アプリケーションにおいて、デルタシグマADCが卓越した精度を提供するために極めて重要です。

デルタシグマADCの動作

デルタシグマADCは、オーバーサンプリング、ノイズシェーピング、デシメーションという3つの基本的な技術を組み合わせることで動作します。これらの戦略により、ADCは高分解能、低ノイズのアナログ入力信号をデジタル出力信号に変換することができます。

オーバーサンプリング

オーバーサンプリングとは、入力信号をナイキストレート (信号帯域幅の正確な2倍またはベースバンド信号の最高周波数) よりも著しく高い周波数でサンプリングすることです。オーバーサンプリングは、アナログアンチエイリアシングフィルタに対する要求を単純化することで大きな利点をもたらします。この戦略は、厳密な必要性を超えて、特定の時間に余分なサンプルを収集することを含みます。その結果、ADCは増大したデータセットを取得し、最終的なデジタル出力の平均化と分解能の強化を通じてノイズの軽減を支援します。

ノイズシェーピング

オーバーサンプリングのプロセスに続いて、ノイズシェーピングが行われます。このフェーズでは量子化ノイズ分布の明確な変調が編成されます。周波数スペクトルにわたる量子化ノイズの均一な散乱とは異なり、ノイズシェーピングはこのノイズをより高い周波数にシフトさせようとします。この変更は、積分器、1ビットDAC、コンパレータを含むデルタシグマ変調器の複雑な構成によって容易になります。独創的なフィードバック機構を通じて、量子化誤差は積分器を介して入力にループバックされます。この機構はノイズスペクトルを進化させ、目的の周波数帯域内のノイズ電力を減少させると同時に、高い周波数でのノイズ電力を増大させます。

デシメーション

デルタシグマADCの動作における最終段階であるデシメーションはノイズシェーピングの後に続き、過剰な高周波量子化ノイズの除去を目標とします。デジタルローパスフィルタを介して実行されるデシメーションはノイズレベルを大幅に低減し、信号対雑音比 (SNR) と全体的な性能を向上します。SNR改善の程度は110log10(K)に相当します。Kはオーバーサンプリング比 (K) です。同時に、デシメーションは、全てのn番目のサンプル選択を通じた、より適切なレベルにインテリジェントにダウンサンプリングすることによって、以前のオーバーサンプリングから生じる余剰データレートに対処します。これは、動作上のニーズに合致するだけでなく、関連する周波数範囲内の分解能を高めます。

デルタシグマADCの利点

デルタシグマADCは、特有のアーキテクチャと動作原理により、他のADCと比較して様々な利点があります。最も注目すべき利点は、優れた分解能とノイズ低減であり、精度と正確さを必要とするアプリケーションに特に適しています。

高分解能

デルタシグマADCの特筆すべき利点の一つは、高分解能を達成できることです。分解能は入力の変化に基づいて出力の最小の識別可能な変化を指し、通常はビット単位で測定されます。デルタシグマADCはオーバーサンプリングを採用し、アナログ入力信号からより多くのデータポイントを収集します。前述したように、これはナイキストレートよりもかなり高いレートでサンプリングを行うことを含みます。量子化ノイズを再編成するノイズシェーピングと共に、この高いサンプリングレートにより、有効ビット数 (ENOB) が従来のサンプリングプロセスで達成できる値を超えることができます。その結果、デルタシグマADCは入力信号の非常に微妙な変化を検出することに長けています。この特性は、高精度が要求されるオーディオ処理や計測などのアプリケーションに非常に適しています。

ノイズリダクション

ノイズ軽減は、デルタシグマADCが提供するもう1つの顕著な利点です。アナログ信号をデジタルに変換する過程で、デジタルフォーマットの精度が限られているために量子化ノイズが発生します。デルタシグマADCは、このノイズを自然に形成するために変調器のフィードバックループを利用して、希望の周波数幅を超えた高い周波数に押し上げることによってこれに対処します。その後、デシメーションフィルタはこれらの高周波ノイズ成分を効果的に除去します。この技術はノイズシェーピングとして知られており、デルタシグマADCの動作の基本的な面を構成します。デルタシグマADCは、意図した周波数範囲内のノイズを抑制することで、信号対雑音比 (SNR) を著しく向上させ、それによって元の入力信号のより洗練された正確なレンダリングを実現します。

デルタシグマADCの欠点

デルタシグマADCは、高分解能とノイズ低減能力で高い評価を得ていますが、アプリケーションによってはいくつかの欠点を考慮する必要があります。速度制限と複雑さは二つの大きな欠点です。

速度制限

デルタシグマADCはオーバーサンプリング、ノイズシェーピング、デシメーションを含む洗練された一連の動作を行います。これらの動作は計算量が多く、逐次近似レジスタ (SAR) やパイプラインADCのような代替ADCのプロセスと比較すると本質的に遅くなります。具体的には、オーバーサンプリングレートが上昇すると必要最小限を超えた余剰サンプルが必要となり、逆にかなりの処理が必要になります。その結果、この固有の複雑さは変換手続きに遅延を生じさせ、迅速なアプリケーションやリアルタイムアプリケーションには適しません。さらにデシメーションプロセスは、関連するフィルタリングおよびダウンサンプリング段による追加レイテンシに寄与します。したがって、迅速なデータ収集が必要なシナリオでは、デルタシグマADCは一般的に好まれません。

複雑さ

デルタシグマADCは、他のADCと比較してアーキテクチャが著しく複雑です。変調器内にフィードバックループを組み込むことは、デシメーションフィルタリングの本質的な包含とともに、これらのコンバータの設計と実現の複雑さを高めます。このような複雑さは製造コストの上昇に寄与し、設計段階やより広いシステムへの統合段階においてもハードルをもたらす可能性があります。最適な性能を達成するためには、細心の較正とチューニングの手順が必要であるため、さらに複雑さが増加します。さらに、ノイズシェーピングとフィルタリング技術を最適化するための数学的原理を包括的に把握するには、多大な時間と労力が必要です。

デルタシグマADCに適したアプリケーション

これらの欠点にもかかわらず、デルタシグマADCは、高分解能とノイズ低減機能を活用できるアプリケーションに特に適しています。このセクションでは、デルタシグマADCが特に有用である2つの重要な状況、すなわちオーディオ処理と精密測定について説明します。

オーディオ処理

音声信号は、マイクによって収集されても、楽器によって作成されても、本質的にアナログです。オーディオシステムにおいて基本的に必要なことは、忠実度の損失を最小限に抑えて、処理、保存、または伝送のためにアナログ信号をデジタル形式に変換することです。さまざまな理由から、デルタシグマADCはこのアプリケーションに最適な選択肢です。

まず、デルタシグマADCの優れた分解能は、オーディオ信号の微妙なニュアンスを記録するのに適しています。これらのADCはオーバーサンプリングを行うため、単位時間当たりの情報を必要以上に収集し、ノイズシェーピングは量子化ノイズを広いスペクトルに分散させ、オーディオ帯域でより大きな信号対雑音比 (SNR) を可能にします。

さらに、ノイズシェーピングは、音質と完全性を維持するためのオーディオアプリケーションで重要なインバンドノイズを大幅に低減します。

最後に、音声処理における一般的な帯域幅はかなり控えめ (20Hz〜20kHz) であり、デルタシグマADCの速度制限はこの状況では重要ではないことを示唆しています。

精密測定

センサデータ収集、計装、工業プロセス制御などの精密測定アプリケーションでは、高精度とノイズ耐性が要求されます。デルタシグマADCは特にこのような作業に適しています。

デルタシグマADCの優れた分解能により、入力信号のごくわずかな変化を正確に捕捉できます。これは、わずかな信号変動でも大きな影響を与える精密測定アプリケーションにおいては非常に重要です。

さらに、デルタシグマADCは量子化ノイズを関連周波数帯域から遠ざけるノイズシェーピング技術を使用します。これは、ノイズレベルが高いと関心のある信号が隠れてしまう可能性があるため、低レベル信号を持つ測定システムでは特に重要です。多くの精密測定アプリケーション (温度ロギングや歪みゲージ測定など) は非常に低速であるため、デルタシグマADCの速度制限は性能にほとんど悪影響を与えません。

設計上の考慮事項とトレードオフ

デルタシグマADCを使用するシステムを開発する際には、いくつかの重要な考慮事項とトレードオフを考慮する必要があります。これは、ADCがアプリケーションのニーズに十分に適合することを保証するためです。これらの要因には、分解能、帯域幅、複雑さ、消費電力、コストが含まれます。このセクションでは、これらの各点について詳細に説明します。

分解能とオーバーサンプリングレート: オーバーサンプリング比 (OSR) はデルタシグマADCの分解能を決定します。OSRが高いほど、帯域幅の減少と計算量の増加とのトレードオフによって高い分解能が得られます。その結果、帯域幅を不必要に下げたり、処理のオーバーヘッドを増加したりすることなく、分解能の要件を満たす理想的なOSRを決定することが重要です。

帯域幅: デルタシグマADCの帯域幅はOSRに反比例します。高分解能のアプリケーションでは高いOSRが必要になる場合があり、帯域幅は自然に制限されます。高分解能と広帯域幅の両方を必要とするアプリケーションでは、このトレードオフは大きな制約となる可能性があります。その結果、アプリケーションの個々の要件に基づいてOSRとADCの帯域幅のバランスを適切にとることが極めて重要です。

複雑さとフィルタ設計: ノイズシェーピングとデシメーションフィルタにより、デルタシグマADCは他のADCよりも洗練されたアーキテクチャをもっています。フィルタ設計の複雑さ、特にデシメーションフィルタはADCの性能に大きな影響を与える可能性があるため、考慮する必要があります。デルタシグマADCの複雑さは、シンプルさと低レイテンシが重要なアプリケーションでは不利になる場合があります。

消費電力: オーバーサンプリングとノイズシェーピングはより多くの計算を必要とするため、消費電力が大きくなる可能性があります。デルタシグマADCの消費電力は、バッテリー駆動アプリケーションや電力効率が重要な状況での個々のアプリケーションに合わせて検証および最適化されなければなりません。

コスト: デルタ・シグマADCは複雑であるため、単純なADCアーキテクチャよりも高価であることが頻繁にあります。しかし、高分解能と低ノイズを必要とするアプリケーションではコストの増加が正当化される場合があります。予算の制限を調べ、アプリケーションのパフォーマンスのニーズとのバランスを取ることが重要です。

実装の選択肢: アプリケーションに応じて、設計者は個別のデルタシグマADC部品またはADCと他の機能 (マイクロコントローラなど) を組み合わせた統合ソリューションを選択することができます。これらのソリューションの決定は、利用可能なスペース、経済的な懸念、他のシステム部品との統合の必要性などの要因に影響されます。

アカウントにログイン

新しいアカウントを作成