SAR ADC入門

基本的な概念と概要

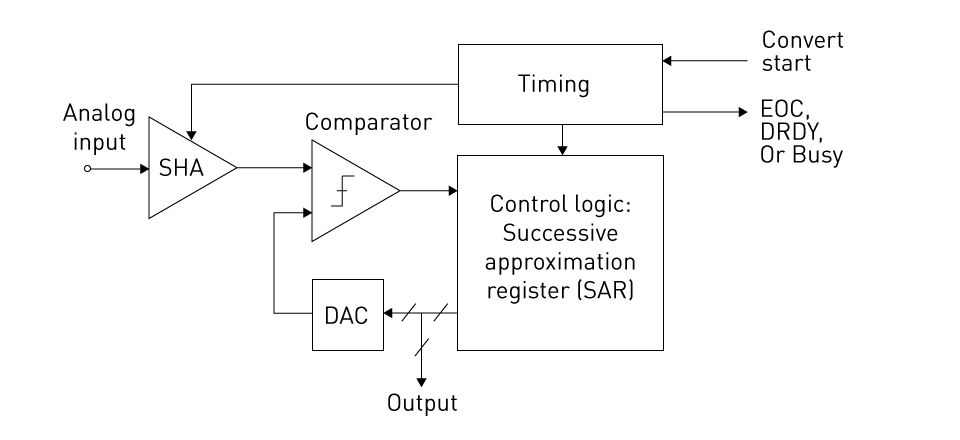

図3 : SARアーキテクチャ

逐次近似レジスタ (SAR) アナログ・デジタルコンバータ (ADC) は、広く採用されているADCの変種として重要な位置を占めており、特に変換速度、電力効率、分解能の調和を必要とするアプリケーションに適しています。SAR ADCの動作基盤は、入力アナログ電圧の収束近似にADCを導くための二分探索アルゴリズムの利用に基づいています。「逐次近似」という用語は、ADCがアナログ入力電圧を推定するために使用する反復法を指します。これは近似値をステップごとに徐々に微調整し、その都度実際の入力電圧に近づけていくことで動作します。

逐次近似レジスタは、SAR ADCの中心的な部品です。このレジスタ内では、バイナリ値は入力電圧の現在の近似値を表しています。変換プロセスの各段階で、SAR制御ロジックはこの近似の1ビットを系統的に調整し、最上位ビット (MSB) から始まり最下位ビット (LSB) へと進みます。

SAR ADC構成に不可欠な構成要素は、デジタル・アナログコンバータ (DAC) です。SAR制御論理と調和して機能するのがDACであり、SARレジスタに保存されている継続的な近似値をアナログ電圧に変換する作業を行います。その後、このアナログ電圧は入力電圧とマッチングされます。DACの出力が入力電圧に達しない場合、精査される特定のビットは設定状態を維持し、逆に入力電圧を超えた場合はリセットされます。この反復的手順は、最下位ビット (LSB) に達するまで進行し続けます。

標準的なSAR ADCの動作シーケンスでは、次のステップが実行されます。

- 入力アナログ電圧は一定の値に保たれます。

- 初期化はSARレジスタの最上位ビット (MSB) を設定することから始まり、DACに対応するアナログ電圧出力を生成させます。

- コンパレータは入力電圧に対するDAC出力を評価し、この結果は更新プロセスを通じてSARレジスタに影響を与えます。

- 比較後、SARレジスタ内の次のビットがテストされ、最下位ビット (LSB) が検査を受けるまでサイクルが続きます。

- テスト反復が完了すると、SARレジスタに存在する最終値は入力アナログ電圧のデジタル表現を示します。

SAR ADCは、中程度の速度で効率的な機能を発揮することで差別化されます。高い分解能を得るために多数のコンパレータを必要とするフラッシュADCとは対照的に、SAR ADCは単独のコンパレータに依存し、反復近似によって徐々に分解能を達成します。この特徴的な特性により、SAR ADCは消費電力と部品点数に関して特に中~高分解能の領域で効率的です。

SAR ADCのアーキテクチャ

サンプルおよびホールド回路

サンプルおよホールド回路は、SAR ADCのフレームワーク内の基本的な部品を構成します。これはADCシステムへのアナログ信号の最初のエントリポイントとして動作します。基本的に、サンプルおよびホールド回路は入力されたアナログ電圧をサンプリングし、変換プロセス全体を通して一貫したレベルに維持するという二重のタスクを実行します。この回路の重要性は、アナログ信号の潜在的な時間的変動から生まれ、正確なADC変換のために安定した電圧レベルを必要とします。

コンパレータ

コンパレータはSARアーキテクチャ固有のもう一つの重要な側面です。サンプルおよびホールド回路によるアナログ入力電圧の収集と安定化に続いて、コンパレータはこの保持電圧を評価する責任を負います。その際、内蔵のデジタル・アナログコンバータ (DAC) によって生成される基準電圧との比較を行います。この比較を通して、コンパレータはサンプリングされた入力電圧が基準電圧を超えるか下回るかを示すバイナリ出力を生成します。この比較の結果は、逐次近似レジスタの動作を導く上で重要な役割を担い、ADCの入力電圧の近似の反復的な精錬に影響を与えます。

デジタル・アナログコンバータ (DAC)

SAR ADCに採用されているデジタル・アナログコンバータは独特の役割を担っています。オーディオのようなデジタル信号をアナログ形式に主に変換するスタンドアロンDACとは対照的に、SAR ADCに内蔵されたDACは基準電圧を生成する内部機能を担います。これらの基準電圧は、比較のためにサンプリングされた入力電圧と比較されます。逐次近似レジスタに格納されている一般的なバイナリパターンによって駆動され、DACの動作は近似の反復プロセスに寄与します。SARが徐々にその推定値を向上させるにつれて、DACはますます正確な基準電圧を生成するように適応します。

連続した近似レジスタ

SAR ADCの中核には、重要な逐次近似レジスタ (SAR) があります。この部品は、逐次近似アルゴリズムの本質を具現化し、SAR ADCの動作の本質として機能します。SARは初期近似からその操作を開始し、続いて一連の連続した比較を通してその微調整を進めます。nビットADCの場合、これはn個の比較に等しく、最上位ビット (MSB) から始まり、最下位ビット (LSB) で終わります。それぞれの比較を行い、SARは現在精査中のビットを修正します。DACからの出力が入力電圧より低い値を記録した場合、調べているビットは1に設定され、逆の場合、0に設定されます。この反復的なプロセスは、変換手順の全体が完了するまで続きます。

SAR ADCの動作

二分探索アルゴリズム

SAR (逐次近似レジスタ) ADCの基本的な動作原理は、アナログ入力値が存在する実行可能性な範囲を徐々に狭めるために使用される反復技法である二分探索アルゴリズムに依存しています。このアルゴリズムは各ビットを精査し、最上位ビット (MSB) から開始して最下位ビット (LSB) で終わる実際のアナログ入力に最も近いものを識別することで機能します。

二分探索を開始するには、MSBを1に設定し、他のビットはすべて0にしておく必要があります。その後、このバイナリパターンはDACを使用してアナログ基準電圧に変換されます。この結果得られた基準電圧は次にサンプリングされた入力電圧に対して並べて比較されます。比較の結果、基準電圧が入力電圧より低いことが判明した場合、MSBは設定値1を保持し、逆に基準電圧が入力電圧を超えた場合、MSBはゼロに設定されます。このプロセスは、ビットシーケンス全体が評価を受けるまで、先行するビット評価の結果を現在検討中のビット評価とマージして、後続のビットについて反復的に繰り返されます。例えば、3ビットADCを含むシナリオがあります。初期近似値は100 (二進法) であり、10進値で4に相当します。この初期近似が不十分であることが証明された場合、その後の近似値は10進数の値で6に対応するなど、(二進法で) 110に進化し、最終的な近似値が確定するまで続きます。

変換サイクル

SAR ADC変換サイクルは、アナログ入力を対応するデジタル出力に変換するプロセスをカプセル化します。このサイクルはサンプリングの開始とともに展開し、その間に入力電圧がサンプリングおよびホールド回路によって捕捉され、安定化されます。この段階に続いて、二分探索アルゴリズムが動き始め、サンプリングされた電圧のデジタル表現を近似します。二分探索の各反復は、ADCのクロッキング機構と相関する単一のクロックサイクルに合致します。nビットADCの場合では、サイクルは、正確には処理されるビットごとに1クロックサイクルである、nクロックサイクルで構成されます。

SAR ADC変換サイクルは、アナログ入力を対応するデジタル出力に変換するプロセスをカプセル化します。このサイクルはサンプリングの開始とともに展開し、その間に入力電圧がサンプリングおよびホールド回路によって捕捉され、安定化されます。この段階に続いて、二分探索アルゴリズムが動き始め、サンプリングされた電圧のデジタル表現を近似します。二分探索の各反復は、ADCのクロッキング機構と相関する単一のクロックサイクルに合致します。nビットADCの場合では、サイクルは、正確には処理されるビットごとに1クロックサイクルである、nクロックサイクルで構成されます。

変換を実行するために必要な時間の長さは、使用されるビット数に対応するADCの分解能に直接リンクしていることは注目に値します。したがって、一貫したクロックレートの下では、分解能の増加は対応する変換時間の上昇を引き起こします。この分解能と速度の間の相互作用は、SAR ADCを組み込んだシステムを組織化する際には、設計段階で重要なトレードオフを明確にするため、慎重な考慮が必要です。

SAR ADCの利点

中程度の速度での効率性

SAR ADCは、特に中程度の速度で動作する場合に、アナログ信号を効率的にデジタル形式に変換することに優れているため、高い評価を得ています。この効率性は主に二分探索アルゴリズムの採用に起因しており、これは各ビットの反復評価を通じてアナログ値の精度を高くする機能です。この方法は、積分ADCでよく見られる特徴である、すべての実行可能な値の評価を必要とするアルゴリズムとは全く対照的です。

センサデータの取得からオーディオ処理に至るまで、多くのアプリケーションでは、超高速変換が必要とされないことがよくあります。このような状況において、SAR ADCは模範的なソリューションとして現れ、変換のペースとプロセスの固有の複雑さの間の調和した均衡を適切に打ち立てています。この属性は、それぞれ高速または低速になる傾向があるデルタシグマADCやフラッシュADCで使用されるアルゴリズムと並べ比べると特に有利です。SAR ADCの中間速度プロファイルは、消費電力や部品コストなどの基本的な考慮事項を無視せずに、効率的なデータスループットに重点を置くさまざまな状況に適した候補です。

低消費電力

SAR ADCの最大の利点の一つは、その優れた電力効率です。多数のコンパレータを並列に動作させる必要があるフラッシュADCとは対照的に、SAR ADCは単独のコンパレータの能力を利用して、少しずつ段階的に意思決定を行います。この設計上の特徴により、特に動作していない期間において、ADCの消費電力を大幅に削減することができます。

フラッシュADCのような並列アーキテクチャに比べて、より少ないトランジスタで変換を行うことができるSAR ADCの容量は、消費電力を削減する上で極めて重要です。この特性は、エネルギー効率の最適化が重要な優先事項となっているバッテリー電力に依存するアプリケーションで特に有利になります。

さらに、一部のSAR ADCはパワーダウンモードを提供しており、ADCが変換プロセスに積極的に関与していない場合に、消費電力をさらに削減する機能を備えています。この機能は、定期的な測定が必要条件であり、測定間の賢明な電源管理が最も重要であるセンサノードのような場合に特に重要です。

SAR ADCの欠点

逐次近似レジスタ (SAR) ADCは大きな利点をもたらしますが、十分な情報に基づいて設計を決定するためには、その限界と欠点を理解することが重要です。このセクションでは、SAR ADCの主な欠点について説明します。

分解能の制限: SAR ADCの分解能は基本的に制限されています。中間的な分解能を必要とする作業では効果的に機能しますが、高分解能ニーズに直面した場合は不十分です。基本的に、分解能の要求が大きくなるにつれて、SAR ADC固有の設計限界がより明確になります。

高分解能での変換速度の低下: SAR ADCの基本的な属性は、分解能の増大に伴い、正確な近似に必要なビット数が比例して増加することであり、その結果、より多くの変換ステップが必要になることです。この増加したステップ数は、結果として変換プロセスで減速をもたらします。そのため、SAR ADCは低分解能で中速を効率的に管理できますが、高分解能の必要性が生じると動作ペースが低下します。

クロックジッタに対する感度: クロックジッタは、逐次近似段を編成するためにクロック信号に依存しているため、SAR ADCの性能に顕著な影響を及ぼします。クロック信号のタイミングのわずかなズレは不正確さをもたらす可能性があり、サンプリングレートが高くなると特に懸念されます。このクロックジッタに対する感受性は、特に高周波アプリケーションの領域において、SAR ADCの実効分解能と動的性能を低下させる可能性があります。

線形誤差: アナログ信号の正確な表現を保証するには、線形性を維持することが重要です。SAR ADCで、線形性は内蔵のデジタル-アナログコンバータ (DAC) の性能に基本的に関連しています。DACに存在する任意の程度の非線形性は、変換プロセス中にエラーを引き起こす可能性があります。高性能DACの採用はこの懸念を軽減することがでますが、ADCシステム内のコストと複雑さの両方を高めることになることがよくあります。

ノイズ感受性: SAR ADCは、デルタシグマADCのような他のADCタイプと並べて比べると、ノイズに対する脆弱性が高くなります。この感受性は、ノイズ低減戦略で一般的に使用されているオーバーサンプリング技術やノイズシェーピング技術がないことが大きな原因です。したがって、SAR ADCはノイズ性能が最も重要な状況では最適な選択肢ではないかもしれません。

グリッチインパルス: 二分探索アルゴリズムのDACセトリング時間内には、グリッチとして知られる過渡的な電圧スパイクの可能性が存在します。このようなグリッチが発生すると、ADC変換プロセスに誤ってエラーをもたらす可能性があり、特に急速な変化が一般的な高周波アプリケーションではそうです。この現象は、特に高周波を特徴とする状況でSAR ADCを利用する場合に、グリッチ関連の課題に対処することの重要性を明確に示しています。

SAR ADCに適したアプリケーション

逐次近似レジスタ (SAR) ADCは、低消費電力と中程度の速度により、さまざまなアプリケーションで使用されています。このセクションでは、SAR ADCの2つの主要なアプリケーション、すなわちデータロギングとセンサインタフェースについて説明します。

データロギング

SAR ADCが注目されるアプリケーションの一つは、データロギングの分野です。データロギングは、頻繁に一貫したサンプリングレートに従い、時間間隔にわたってデータを蓄積します。このデータ編集には、温度、湿度、圧力などの環境面と、電圧、電流、消費電力などのシステム関連変数を含む、さまざまなパラメータ配列を含みます。

データロギングの場合、SAR ADCはいくつかの理由で有利な適合性を示します。

電力効率: データロギングのアプリケーションは、ほとんどの場合、長時間の継続的な動作を要求し、時にはバッテリー電源に依存します。低消費電力を特徴とするSAR ADCの基本的な特性は、これらの特定の状況に対して最適です。

中程度の速度: データロギング操作には通常、高速な変換は必要ありません。SAR ADCが示す中程度の速度は、しばしばデータロギングアプリケーションの要求に十分適していることを証明します。SAR ADCがこの中速範囲内で効果的に機能する能力は、データロギングの時間的要件によく合致しています。

分解能の柔軟性: SAR ADCは分解能に関して適応性という価値のある属性を拡張して、特定のアプリケーションの固有の要件に合わせた分解能の選択を可能にします。中程度の分解能が求められるデータロギングの分野では、SAR ADCは必要な精度を効率的に実現することに優れています。

センサインタフェース

SAR ADCはセンサインタフェースに広範な有用性を見出しており、アプリケーションのもう一つの重要な領域を構成しています。センサは、さまざまな物理量を測定し、機器やプロセッサが解釈できる識別可能な信号に変換するのに役立ちます。温度センサ、圧力センサ、加速度センサ、光センサなどの幅広いセンサは、正確かつ精密なデータ変換を容易にするために、SAR ADCとシームレスにインタフェースすることができます。

センサインタフェースにSAR ADCが適している理由は次のとおりです。

精度: 多くのセンサが要求する精度は、正確なアナログ・デジタル変換を必要とします。特に、SAR ADCは、過度の消費電力を伴わずに必要な精度を提供する能力を持っています。

高速セトリング時間: SAR ADCにおけるセトリング時間の概念は、入力信号の変更後にコンバータが安定した出力を確立するのにかかる時間に関係します。より速いセトリング時間は、センサ出力の変動に対するより速いADC応答性に対応します。SAR ADCは、その非常に便利なセトリング時間で知られており、センサ信号の急激な変化に迅速に適応することが必要とされる状況では非常に有用です。

低レイテンシ: 制御システムの領域では、センサの読み取り値とシステムのその後の応答の間の遅延を最小化することが極めて重要です。SAR ADCがデジタル出力を迅速に供給する能力は、遅延を最小限に抑え、迅速かつ正確なシステム反応を保証することに依存する状況で非常に有利であることが証明されています。

統合: SAR ADCは、コンパクトなフォームファクタと優れた統合能力を提供し、センサインタフェース内での有用性を向上する側面があります。SAR ADCはシステムの全体的な合理化された設計と統合に寄与するため、この属性は、コンパクトまたは携帯機器を考案する際の重要性を高めます。

設計上の考慮事項とトレードオフ

逐次近似レジスタ (SAR) ADCを搭載するシステムを構築する際には、性能、費用、エネルギー使用量の理想的な均衡を達成するために多様な要因を評価することが重要になります。このセグメントでは、SAR ADCを使用する際に考慮すべき基本的な側面と、舵取りすべき妥協点について掘り下げていきます。

分解能と変換速度: 分解能と変換ペースの間には決定的な妥協点があります。一般に、ADCの分解能が上昇するにつれて、高い精度を得るために必要なクロックサイクル数が増加するため、変換時間も長くなります。妥当な変換速度を維持しながら、アプリケーションの要件に合った適切な分解能を選択することは、依然として重要な考慮事項です。

消費電力とパフォーマンス: SAR ADCは、他のADCアーキテクチャと比較して消費電力が小さいことで有名であるにもかかわらず、分解能と変換レートを向上させることで消費電力が増加する可能性もあります。アプリケーション内の電力割り当てを綿密に精査し、動作性能の要件を評価することが最も重要です。これには、節電と最適な性能の間の微妙な均衡を巧みに舵取りするADC構成を選択する必要があります。

入力インピーダンス・マッチング: SAR ADC内にサンプルおよびホールド回路が存在すると、発信元の信号源に容量性負荷をもたらす可能性があります。このような現象は、特に高インピーダンス源の場合に、潜在的に有害な影響を与える可能性があります。したがって、ADCの信号サンプリングの揺るぎない精度を保証するために、インピーダンス整合プロトコルを実行する際には相当な注意が不可欠です。

基準電圧の安定性: 基準電圧の精度と安定性は、SAR ADC変換の精度に大きな影響を与えます。基準電圧源の一貫性と信頼性は、特に顕著な精度レベルを達成することに重点を置くアプリケーションにおいて極めて重要です。基準電圧の安定性と最小ノイズを確認し、高精度な動作が可能な環境を整えるための効果的な対策が必要です。

ノイズに関する考慮事項: ノイズの存在は、ADC内のアナログ-デジタル変換の精度に大きな影響を与える可能性があります。アプリケーションの要件に沿ったノイズ仕様を備えた適切なSAR ADCを選択することは、フィルタリングや信号平均化などのノイズ軽減技術の実装と組み合わせることで、忠実な信号デジタル化を確保するために最も重要です。

コストと複雑さ: SAR ADCに関連する費用は、希望の分解能、速度、および内蔵された機能によってかなり変動します。さらに、高分解能SAR ADCの搭載に伴う複雑さは、追加の部品や洗練されたレイアウト戦略を必要とする可能性があります。したがって、プロジェクトの予算と目的の包括的な枠組みの中で、コストと複雑さを慎重に評価することが不可欠です。

ADCドライバ回路: オペアンプとアンチエイリアシングフィルタを含む、ADCドライバ回路の選択で細心の注意を払うことは、SAR ADCの性能の要になります。選択されたドライバ回路は、適切な帯域幅、最小のノイズ、無視できる歪みを提供し、意図したアプリケーションの必要条件に細心の注意を払って整合し、従ってSAR ADCの動作の全体的な有効性を支えるものでなければなりません。

アカウントにログイン

新しいアカウントを作成