アプリケーション要件

アプリケーションのニーズに基づいて、ADCの種類とその設計の選択が行われます。

一般的なアプリケーション要件

アプリケーションの一般的な要件には、次のものが含まれます。

データレートの要件: アプリケーションが必要とするデータレートがADCでサポートされている必要があります。デジタル通信のような高速アプリケーションには高速データレートが必要です。

正確さと精度: 高分解能ADCは、高い精度を必要とするため、一部のアプリケーションで必要とされます。例えば、高分解能のADCは、医療用イメージングにおいて正確なデータを記録するために重要です。

消費電力: アプリケーションの電力制限は、ADCの電力要件と一致する必要があります。例えば、低電力ADCはバッテリー駆動アプリケーションに必要とされます。

ダイナミックレンジ: 入力信号の振幅が大きく変動する可能性がある状況では、ADCが変換できる最小信号レベルと最大信号レベルの間の広い幅が非常に重要です。

レイテンシ: 入力信号の変化に迅速に対応するためには、クローズドループ制御システムなどの一部のアプリケーションで低レイテンシのADCが必要です。

環境条件: アプリケーションに応じて、ADCは振動や極端な温度などの特定の要件を持つ環境で機能する必要がある場合があります。

既存のシステムとの統合: 現在の技術スタックやシステムとのADCの互換性も決定要因となります。

デジタル通信のアプリケーション要件

例えば、アプリケーションがデジタル通信の場合、次の仕様が必要になります。

高いデータレート: デジタル通信は、特に5G以降の到来で、非常に高いデータレートを必要とします。その結果、ADCは大きな帯域幅とスループットを可能にし、アナログ信号をデジタル領域に迅速に変換する必要があります。

ダイナミックレンジと感度: 異なる振幅の信号は、通信システムによって頻繁に扱われます。これらの変更を効果的に管理するには、良好なダイナミックレンジを持つADCを使用する必要があります。

デジタル・シグナル・プロセッサ (DSP) との統合: ADCとDSPは、信号を調整し変調するために通信システムと頻繁に協力します。その結果、DSPとの効率的なリアルタイム処理ADCの統合が実現可能です。

拡張性と将来への対応: 通信システムにおけるデータレートの増加に対する絶え間ない要求を考えると、スケーラビリティ要件を満たし、ある程度将来性のある高速ADCを構築することが重要です。

市場の需要と影響: デジタルコミュニケーションは巨大な市場を持ち、多くのビジネスや日常生活に大きな影響を与えます。ADC設計の成功によりこの分野に貢献することは、業界全体に大きな影響を与える可能性があります。

ADCの選択

特定のシステム要件に応じて、多くのADCタイプをデジタル通信アプリケーションに使用することができます。ADCの選択は、速度、分解能、消費電力、コストなどの要素に依存し、それぞれにメリットと限界があります。

デジタル通信のための潜在的なADC

デジタル通信のアプリケーションでよく使用されるADCには、次のものがあります。

逐次近似レジスタ (SAR) ADC: 高速平均速度、優れた分解能、低消費電力のため、SAR ADCは様々なアプリケーションでよく利用されています。中程度から高精度を必要とするデータ収集システム、センサー、通信インタフェースなどのアプリケーションが理想的です。

デルタ・シグマADC: デルタ・シグマADCの特長は、高分解能と低ノイズ性能です。精度とシグナルインテグリティが不可欠なオーディオや通信アプリケーションでは、これらが頻繁に使用されます。

パイプラインADC: 高速アプリケーションはパイプラインADC設計の焦点です。それらには多くの段階があり、高い変換率を達成しながら、立派な分解能を維持することができます。有線および無線の高速通信システムでは、パイプラインADCがしばしば使用されます。

フラッシュADC: フラッシュADCは現在市場で最も高速なADCの1つですが、その速度はコストと消費電力の高さによって制約されています。高周波通信システムを含む、非常に高速な変換を必要とする用途に適しています。

デジタル通信アプリケーション用のADCを選択する際には、必要なデータレート、精度、分解能、利用可能な電力予算など、システムの特定のニーズを考慮します。理想的な選択肢は、ADCの各形式には独自のトレードオフがあるため、アプリケーションの特定の要件に依存します。

デジタル通信アプリケーション用のパイプラインADCの選択

そのようなシステムのニーズによく適合する独自の利点により、パイプラインADCはデジタル通信アプリケーションにとって良い選択肢となるかもしれません。デジタル通信アプリケーションでパイプラインADCを使用するかどうかの決定に影響を与える要因は次のとおりです。

高速変換: パイプラインADCの高速性能はよく知られています。多数のステップを持つパイプライン構造を採用しており、高いコンバージョン率を実現しています。パイプラインADCの高速変換は、リアルタイムのデータ処理と迅速な信号キャプチャが必要なデジタル通信システムで役に立ちます。パイプラインADCの標準的なサンプリングレートは、数Mspsから100Msps+までです。

中分解能から高分解能: パイプラインADCは低分解能から高分解能を提供できます。パイプラインADCは、多くの分解能 (各ステージ) をカスケード接続することにより、単一ステージのADCよりも大きな全体分解能を得ることができます。デジタル通信アプリケーションにおけるアナログ信号の適切な表現と再構成が重要です。高いサンプリングレートでは8ビット、低いサンプリングレートでは16ビットの間で、パイプラインADCは様々な分解能を扱うことができます。

高速インタフェースとの互換性: パイプラインADCは、高速シリアルインタフェース (USB 3.0など) や光通信システム、さらにはギガビットイーサネットなどの高速デジタル通信プロトコルとの相互作用に特に適しています。これらの通信インタフェースの高いデータレートにも対応できるのは、変換速度が速いためです。

フラッシュADCよりも低消費電力: パイプラインADCは、しばしば逐次近似レジスタ (SAR) ADCよりも高速であるにもかかわらず、電力制約のあるデジタル通信デバイス、特にバッテリー駆動アプリケーションに最適です。

汎用性: パイプラインADCは幅広い入力信号レベルを処理できるため、さまざまなデジタル通信インタフェースや可変信号振幅のプロトコルに適しています。

システムの複雑さの軽減: パイプラインADCをフラッシュADCのような他の高速ADCと比較すると、単純なトポロジーが頻繁に存在します。これにより、システム全体の設計が簡素化され、クロッキングと同期の難易度を下げ、ADCを通信システムに統合することが容易になります。

正確なタイミングと同期: ADCとデジタル通信システムの他の部分との間の正確なタイミングと同期を必要とするアプリケーションでは、パイプライン遅延が明確に定義されたパイプラインADCが役に立ちます。

ソフトウェア無線 (SDR)、デジタル受信機、無線通信システム、高速データ転送、通信テスト機器は、パイプラインADCを頻繁に使用するデジタル通信アプリケーションのほんの一例です。パイプラインADCが特定のユースケースに最適な選択肢かどうかを判断するには、デジタル通信アプリケーション固有のニーズと消費電力やコストなどのトレードオフを考慮することが重要です。さらに、ADCを選択する際には、必要な分解能、速度、精度、電力予算などのシステム全体のニーズと要因を考慮する必要があります。

パイプラインADCの概要

パイプラインADCアーキテクチャの要約

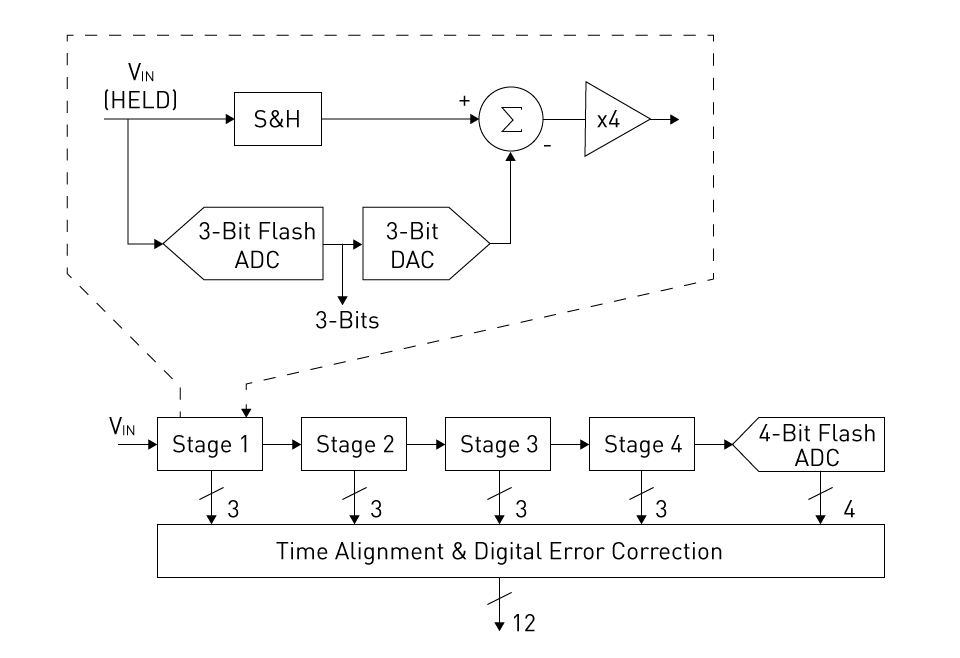

ADC (アナログ・デジタルコンバータ) パイプラインは、高速な変換レートを実現するために、アナログ・デジタル変換プロセスを多くのステージまたはパイプラインセグメントに分割する高速ADCです。最終的なデジタル出力が生成されるまで、各ステップは入力信号の一部を処理し、結果は次の段階に渡されます。パイプライン設計によりアナログ入力の並列処理が可能となり、十分な精度を保ちながら高速変換が可能になります。

図1 : 12ビットパイプラインADC

パイプラインADCの基本的な考え方は次のとおりです。

段階: ADCパイプラインを構成するために、通常は4つ以上の複数のステージが順番に積み重ねられています。アナログ入力信号は各段で部分的にデジタル形式に変換されます。

パイプライン化: パイプライン構造は、各ステップの出力を処理してからステージに渡すことで作成されます。アナログ信号が通るパイプラインの各ステップは、入力のデジタル表現を改善するのに役立ちます。

タイム・インターリーブ: 一部のパイプラインADCは、変換レートをさらに向上させるためにタイム・インターリーブ方式を採用しています。入力信号を様々な間隔でサンプリングする多数の並列パイプラインを採用することで、実効サンプリングレートと変換速度をさらに向上させます。

多重化と逆多重化: 通常、受信信号はより小さなチャンクに多重化され、各チャンクは並列処理のために異なるステージに送信されます。ADCの最終的なデジタル出力は、各ステップからのデジタル出力を逆多重化して結合することによって作成されます。

較正と誤差修正: ステージ間の不一致は、パイプラインADCに追加の誤差をもたらす可能性があります。較正方法と誤り訂正アルゴリズムは、これらの欠陥を減らし、精度と直線性を高めるために頻繁に使用されます。

デジタル処理: 最終出力を作成するには、各ステージからのデジタル出力をデジタル領域で統合して処理する必要があります。アナログ入力信号の適切な表現を保証するために、タイミング、同期、およびデータアライメントはデジタルロジックによって処理されます。

パイプラインADCは、デジタル信号処理、無線通信、光通信、高速変換が必要な高周波データ収集などのシステムによく採用されています。高速かつ正確なアナログ・デジタル変換を必要とするハイスループットアプリケーションに適しており、速度と分解能の良いバランスを提供します。

逐次近似レジスタ (SAR) ADCやシグマデルタADCのような他のADCとは対照的に、それらはより洗練され、より多くの電力を消費します。パイプラインADCの選択は、他のADCオプションと同様に、特定のアプリケーションのニーズと速度、分解能、消費電力、複雑さの間の意図されたトレードオフに基づいて行われる必要があります。

高速データ変換の意義

情報通信、医療用画像、レーダーシステム、高性能コンピュータなど、多くのアプリケーションでリアルタイムまたはほぼリアルタイムのデータ処理が必要とされています。これらのアプリケーションでは、高速データ変換が不可欠です。なぜなら、アナログ信号の迅速なデジタル化が可能であり、その後、効率的に処理、保存、送信ができるからです。

例えば、デジタル通信では、アナログ信号をデジタル形式に迅速に変換できる能力によって、より大きな帯域幅とデータレートのサポートが可能になります。非常に高いデータレートのサポートを要求する新しい通信規格にとって、これは特に重要です。

医療用画像では、迅速に変化する生体信号を高分解能で捕捉するために、高速データ変換が不可欠です。これは、超音波やMRIのような、高品質の画像を提供するために高速なデータ処理が必要なアプリケーションで特に重要です。

パイプラインADCは、SAR設計の効率と精度を高いデータレート能力と組み合わせています。このため、精度と速度の両方が必要な状況では不可欠です。

設計プロセス

仕様

パイプラインADCが目的のアプリケーションのニーズを満たすことを確認するためには、デバイスの開発中に重要なパラメータを正確に記述することが不可欠です。定義する必要のある必須要件は次のとおりです。

分解能: ADCが表現できる離散出力レベルの量は、その分解能に依存します。通常はビット単位で定義されます (例えば12ビットや16ビット)。ADCは、より高い分解能でより正確な読み取り値を提供できます。

サンプリングレート: サンプリングレートは、アナログ入力がデジタル出力に変換される前にADCによってサンプリングされる速度を決定します。サンプル/秒 (SPS) またはメガサンプル/秒 (MSPS) は、通常これを指定するために使用されます。入力信号の最高周波数成分はサンプリングレートによって正確に捕捉される必要があります。

入力幅: ADCが飽和またはクリッピングなしで許容できるアナログ入力電圧範囲は、入力幅によって定義されます。入力幅は、過負荷や歪みの発生なしに予測される入力信号振幅を許容する必要があります。

信号対雑音比 (SNR): SNRは、ADCがノイズと信号をどれだけうまく識別できるかを示す指標です。これは出力の信号電力とノイズ電力の比率を表示します。ノイズ性能が向上し、その結果、より正確な測定値は高いSNRによって示されます。

全高調波歪み (THD): THDは、基本信号に対する高調波成分の合計の比として計算され、ADCによって引き起こされる歪みを定量化します。より良い直線性とより少ない歪みは、低いTHDと相関します。

積分非線形性 (INL) と微分非線形性 (DNL): ADCの線形性はINLとDNLによって測定されます。INLは実際の伝達関数と理想の伝達関数の差を表し、DNLは隣接する出力コード間のステップサイズの差を表します。信号を正しく表現するためには、INLとDNLの両方を小さくする必要があります。

消費電力: ADCの消費電力は、バッテリー駆動アプリケーションにとってバッテリー寿命を最大化するために不可欠です。ADCの電力需要がシステム全体の制限に適合していることを確認するには、最大許容電力使用量を指定します。

レイテンシ: 入力信号とマッチングしたデジタル出力の間の経過時間はレイテンシと呼ばれます。一部のデジタル通信アプリケーションでは遅延を防ぎ、リアルタイムのデータ処理を提供するために低レイテンシが不可欠です。

ダイナミックレンジ: ADCのダイナミックレンジは、それが忠実に表現できる最大入力信号と最小入力信号の間の幅 (ノイズフロアより大きい入力信号) です。弱い入力信号と強力な入力信号の両方を正確に捕捉するためには、大きなダイナミックレンジが必要です。

動作温度範囲: ADCが安全に動作すると予測される動作温度範囲を指定します。深刻な状況や極端な状況で使用する場合、これは特に重要です。

EMI/EMCに関する考慮事項: ADCの動作がシステムまたは周辺部品に望ましくないノイズや干渉を与えないようにするため、電磁障害 (EMI) および電磁両立性 (EMC) に関する規格を考慮します。

設計チームは、これらの基本パラメータを正確に指定することにより、パイプラインADCがデジタル通信アプリケーションの特定の要求と性能基準を満たすことを確認できます。完成品で最高の性能と精度を確保するために、これらの規格は設計段階と部品選択プロセスのガイドとして機能します。

部品の選択

パイプラインADCに投入される部品の選定は次の段階です。これに含まれるオプションは次のとおりです。

サンプル・アンド・ホールド (S/H) 回路: 変換プロセス中、アナログ入力電圧はS/H 回路によって捕捉され、保持されなければなりません。正確で信頼性の高い電圧サンプリングを実現するためには、適切なS/H 回路を使用することが不可欠です。

アナログ入力バッファ: 入力信号のソースインピーダンスからADCを保護し、高い入力インピーダンスを提供するためには、アナログ入力バッファが必要になります。バッファはロードの影響を軽減し、シグナルインテグリティの維持を支援します。

電圧リファレンス: 正確なアナログ・デジタル変換を行うには、正確で安定した電圧リファレンスを使用する必要があります。低ドリフトおよび低ノイズ性能を提供し、ADCに必要な電圧幅に適合する電圧リファレンスを選択します。

クロックソース: 変換プロセスを管理するために、ADCは安定した信頼性の高いクロックソースを必要とします。ADCの速度、タイミング、およびジッタ性能はすべて、使用するクロックソースによって影響されます。信頼性の高い正確なサンプリングを保証するために、高品質のクロックソースを利用することを検討しましょう。

オペアンプとアンプ: シグナルコンディショニングとゲインの変更では、特に入力信号がADCの入力範囲に一致する増幅または減衰を必要とする場合、光アンプや他のアンプが必要になることがあります。

デジタル処理部品: 多くのステージでデータフローとタイミングを管理するために、パイプラインADCはフリップフロップ、論理ゲート、デジタルマルチプレクサなどのデジタル処理部品を必要とします。

コンパレータ: アナログ電圧とリファレンス電圧を比較するために、パイプラインADCの各段でコンパレータが使用されます。コンパレータの性能はADCの速度と精度に影響します。

制御ロジックおよびタイミング回路: ADCは、パイプライン段、タイミング信号、およびステージ同期をレギュレートするための制御ロジックを必要とします。適切なタイミング回路により、ADCが正確に動作することが保証されます。

電源部品: ノイズと干渉を最小限に抑えながら、ADCにクリーンで信頼性の高い電力を供給するための適切な電源部品を選択します。

サポート部品: 抵抗、コンデンサ、インダクタなど、バイアス、フィルタリング、インピーダンスマッチングに必要な追加のサポート部品について検討します。

レイアウトと回路図の設計

回路図の設計: サンプル・アンド・ホールド回路、アナログ入力バッファ、電圧リファレンス、コンパレータ、デジタル処理素子、クロック回路など、すべての必須部品の完全な回路図を作成します。

部品の選択と配置: パイプラインADCの仕様および性能要件を満たす高品質部品を選択します。部品レイアウトを最適化して信号経路を減らし、寄生効果を制限し、ボードスペースを最大化します。

レイアウト設計: シグナルインテグリティ、接地、および配電を考慮した、適切に構造化された順序付けされたレイアウト設計を利用します。クロストークと干渉を低減するには、ノイズの多いデジタルトレースから必須のアナログ信号を遠ざけます。

検証: レイアウトが生産制限に従っており、製造上の問題をなくしていることを確認します。すべての接続が適切で完全であることを確認するには、レイアウトを元の回路図と比較します。可能であれば、レイアウトをシミュレーションして、さまざまな動作シナリオでの性能とシグナルインテグリティを評価します。

設計の検証と試験

デジタル通信アプリケーションにおけるパイプラインADCの設計の検証には、ADCが要求仕様に適合し、正しく機能することを保証する一連のプロセスが関与しています。ADC設計を検証するための重要な段階は次のとおりです。

シミュレーションとモデリング: ADCの機能と性能を検証するには、SPICE、または、その他の関連するシミュレーションツールを使用して広範なシミュレーションを実行します。

機能試験: パイプラインADCのプロトタイプを作成し、実環境設定で機能を確認するための機能テストを実施します。さまざまな入力設定の下で、ADCの直線性、精度、およびノイズ性能を評価します。

タイミングと同期試験: パイプラインADCのさまざまなステージのタイミングと同期を確認します。パイプライン遅延特性とタイミング特性が仕様を満たしていることを確認します。

電力と効率の分析: さまざまな動作状況下でADCの消費電力を測定し、デジタル通信デバイスの電力予算と一致していることを確認します。

線形性と誤差の補正: ADCの直線性と精度を評価するには、較正手順と誤り訂正アルゴリズムを使用する必要があります。

ノイズと歪みの解析: 入力環境とサンプリングレートが異なる場合、信号対雑音比 (SNR) や全高調波歪み (THD) など、ADCのノイズ性能を特性化します。

通信システムとの統合: ADCをデジタル通信システムに統合し、他の部品と比較してその互換性と性能を評価します。

環境試験: 複数の作業状況においてADCの安定性と信頼性を保証するために、さまざまな環境変数 (例えば、温度、湿度) の下で試験を実施します。

技術者は、これらの検証プロセスに従うことにより、パイプラインADCの性能とデジタル通信アプリケーションへの適切さを確実に検証することができます。試験中に発見された設計上の欠陥や改善点に対処し、必要に応じて設計を反復して最高の性能と精度を達成します。

実装と統合

システム設計へのパイプラインADCの組み込み

ターゲットシステムにパイプラインADCを埋め込む際に考慮すべき4つの重要な要素:

電源とデカップリング: ADCに清潔で信頼性の高い電源を供給します。ADCの電源ピンの近くにデカップリングコンデンサを取り付けます。

シグナルインテグリティとレイアウト: 信号障害やクロストークを低減するように、配置を慎重に設計します。ノイズの多いデジタル信号の近くに感度の高いアナログトレースを配線しないようにします。

クロックソースとタイミング: ADCが安定した正確なクロックソースを備えていることを確認します。クロック信号をADCのすべてのステージに正しく分配します。

デジタルインタフェースとデータ処理: ターゲットシステムの通信プロトコルおよびデータ処理ユニットと互換性のあるデジタルインタフェースを作成します。ADCの出力データ型とタイミングがシステム要件と互換性があることを確認します。

エンジニアは、これらのパラメータを注意深く調べ、パイプラインADCをターゲットシステムにスムーズに統合することで、最適な性能と精度を達成することができ、ADCをシステムアーキテクチャ全体の効果的で信頼性の高い要素にすることができます。

システムレベルの検証

パイプラインADCをシステムに統合した後、完全なシステムの状況で意図したとおりに機能することを確認することが重要です。

パフォーマンス試験: さまざまな動作状況下で、ADCの分解能、線形性、精度、およびノイズ性能を評価します。ADCの出力が、指定されたダイナミックレンジ内のアナログ入力信号を適切に表していることを確認します。

速度とタイミングの検証: ADCの変換速度が指定されたサンプルレートとスループットを満たしていることを検証します。ADCおよび他のシステムコンポーネントが正確にタイミング調整されていることを確認します。

インタフェースの互換性: ADCのデジタル出力インタフェースが、システムのデータ処理ユニットおよび通信プロトコルと互換性があることを確認します。ADCの出力データフォーマットとタイミングが、ダウンストリームデジタル部品の要件と互換性があることを確認します。

消費電力と効率: ADCの電力使用量をさまざまな条件で測定し、システムの電力予算と一致していることを確認します。ターゲットシステムへの統合を改善するために、ADCの電力使用量と性能の観点から効率を評価します。

パフォーマンスの最適化

デジタル通信システム用のパイプラインADCの最適化では、アプリケーション固有のニーズに合わせて性能と効率を向上させることが必要です。この最適化を達成するための4つの段階は次のとおりです。

パフォーマンス特性評価と較正: パイプラインADCの長所と限界を理解するために、詳細な性能特性評価を行います。較正手順は、ADCの出力における非線形性やオフセットの問題を調整するために使用されるべきであり、それによってADCの正確さと精度が向上します。

ノイズリダクションと信号調整: ノイズによるADCの性能効果を低減するためのノイズ低減対策を実施します。適切な接地、シールド、フィルタリング手順を使用できます。ADCの入力信号に対するダイナミックレンジと全体的な感度を高めるために、アンプやフィルタなどのシグナルコンディショニングのハードウェア追加について検討します。

タイミングと同期の最適化: パイプラインADCのタイミングと同期を最適化して、デジタル通信システムの他の部品と正確に整合します。クロックジッタを低減し、ADCの全体的なタイミング精度を向上させるために、クロック分配戦略を使用します。

電力管理とスリープモード: 電力管理戦略を使用して、特にバッテリー駆動システムでADCの電力使用量を最適化します。スリープモードまたはパワーダウン機能を使用して、アイドル期間中またはADCがアクティブに変換していないときの消費電力を低減します。

結果と分析

パフォーマンス指標

パイプラインADCの性能は、様々なパラメータを用いて評価することができます。これらの測定はADCの強さと限界を定量化するのに役立ち、特定のアプリケーションへの適用可能性に重要な情報を提供します。以下は重要なパフォーマンスのインジケータです。

分解能: ADCのデジタル出力を表すために使用されるビット数。入力電圧のわずかな変化を正しく記録する能力を示します。

信号対雑音比 (SNR): ADC出力の信号対雑音の電力比。信号と雑音を識別する能力を示します。

全高調波歪み (THD): ADCによって引き起こされ、その直線性と精度に影響を与える高調波歪み。

有効ビット数 (ENOB): ノイズ、歪み、および非線形性を考慮して、実際の設定で達成された有効分解能のビット数。

消費電力: ADCが使用する電力量。効率とバッテリー寿命を最大化するためにバッテリー駆動システムで特に重要です。

改善のための推奨事項

パイプラインADCの性能と設計を改善するために、以下の重要な指標を評価します。

分解能: ADCの分解能を上げると、アナログ入力の微妙な変動を表現する能力が向上し、正確さと精度が向上します。

信号対雑音比 (SNR): ADCのアナログフロントエンドとデジタル処理段のノイズ源を低減することでSNRは向上し、ADCがより弱い信号をより正確に収集できるようになります。

ダイナミックレンジ (DR): ADCのダイナミックレンジを大きくすることで、飽和やクリッピングを伴わずに、より広い範囲の入力信号振幅に耐えることができ、より広い範囲の信号レベルにわたってより高い性能をもたらします。

線形性 (DNLおよびINL): これらの強化には、より良い回路設計、部品の選択、較正手順、レイアウトの考慮事項などが含まれます。

これらの重要な指標に焦点を当てることで、パイプラインADCの性能を向上させるための設計最適化を行うことができ、ターゲットアプリケーションにもっと適しています。これらの改善には、洗練された回路設計、部品の選択、較正技術、レイアウトの考慮事項が含まれる場合があります。

アカウントにログイン

新しいアカウントを作成