高電流アプリケーション向けマルチフェーズコンバータの設計

役立つ情報を毎月お届けします

プライバシーを尊重します

はじめに

ハイエンドのフィールド・プログラマブル・ゲート・アレイ (FPGA) およびアプリケーション特化型集積回路 (ASIC) のコアレールに電力を供給するには、高電流と正確な過渡制御が必要です。近年、FPGA、ASICおよび関連システムの急速な進歩により、複雑性の増大に対処するため、電力供給に関する規制の大幅な見直しが必要になっています。これらの設計では、効率、動的応答、およびMOSFETのサイズと電力損失の間の微妙なバランスが求められます。

これらの要件を満たすために最も一般的に使用される方法は、複数の電源を並列に配置することです。この方法では、これらの電源 (位相とも言う) 間で電流が均等に分配され、必要な電力がより簡単かつ効率的に供給されます。各電源ブランチ間に位相差を設定することでパフォーマンスをさらに向上させ、全体的な電流と電圧リップルを削減できます。ただし、位相を均等に分散し、すべての位相で電流をバランスさせる必要があるため、このプロセスは複雑になる可能性があります。

FPGAおよびASICコアレールの低電圧、高電流の需要を満たし、正確な過渡制御を管理するために、電力システムは現在、マルチフェーズ電力ソリューションを使用してより高い周波数で動作しています。

簡素化のため、 MPM3698とMPM3699は、自動インタリーブやフェーズシェディングなどの高度なマルチフェーズ制御方式を実装しています。本稿では、マルチフェーズコンバータの設計プロセスについて述べ、多相電源設計の重要な側面について説明します。

FPGAおよびASIC設計要件

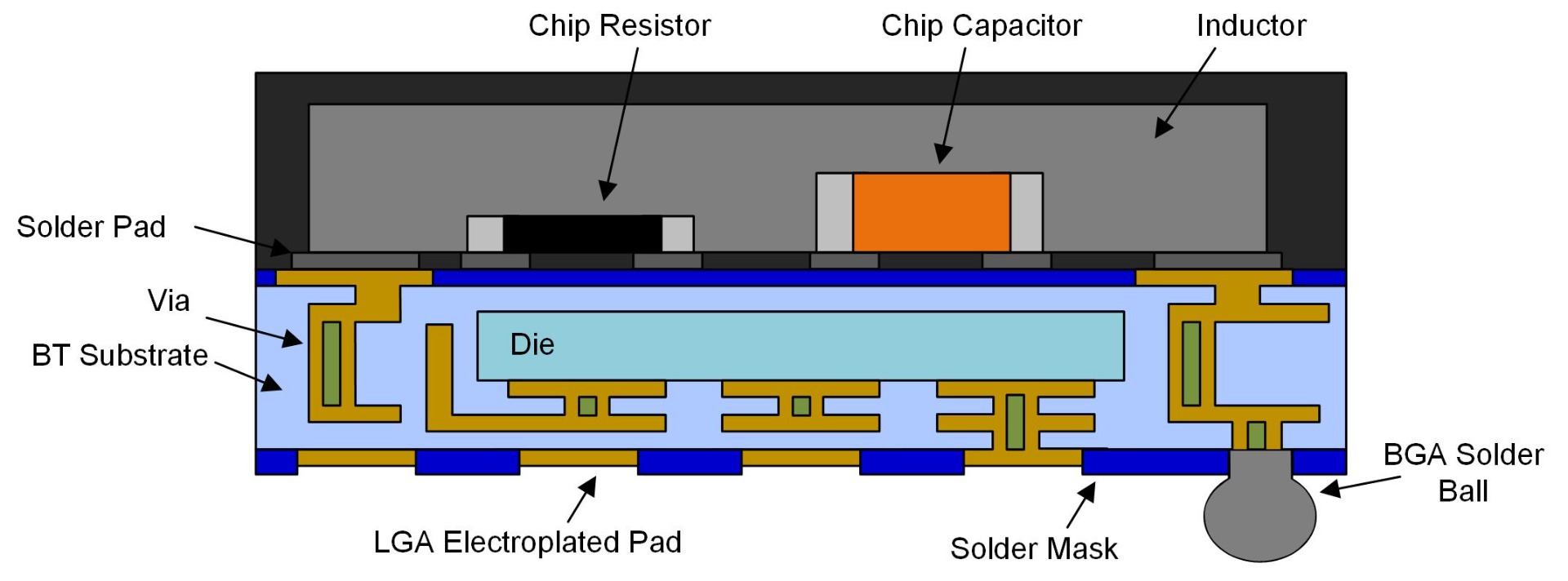

FPGAおよびASIC用の電源を開発する際に考慮すべき最も重要な基準の1つは、さまざまな電源レールの電圧要件です。FPGAやASICの一般的な電圧レールにおいて、入力電圧 (VIN) が12Vの場合、出力電流 (ITDC) は180Aで、出力電圧 (VOUT) は1.2Vです。表1は一般的なFPGAの電圧要件を示しています。このシナリオでは、Spartan 7 FPGAのサンプルが使用されました。

表1: Spartan-7 FPGAの推奨動作条件(1)

| シンボル | 概要 | 最小 | 代表値 | 最大 | 単位 |

|---|---|---|---|---|---|

| FPGAロジック | |||||

| Vccint | 内部電源電圧 | 0.95 | 1 | 1.05 | V |

| オプションの内部電源電圧 | 0.92 | 0.95 | 0.98 | V | |

| Vccaux | 補助電源電圧 | 1.71 | 1.8 | 1.89 | V |

| Vccbram | ブロックRAM電源電圧 | 0.95 | 1 | 1.05 | V |

| オプションのブロックRAM電源電圧 | 0.92 | 0.95 | 0.98 | V | |

| Vcco | HR I/Oバンクの電源電圧 | 1.14 | 3.465 | V | |

| Vin | I/O入力電圧 | -0.2 | - | VCC + 0.2 | V |

| I/O入力電圧 (オプション) | -0.2 | - | +2.625 | V | |

| Iin | 電源投入時または非電源時のピンを流れる最大電流 | - | - | 10 | mA |

| XADC | |||||

| Vccadc | GNDADCに対するXADC電源 | 1.71 | 1.8 | 1.89 | V |

| Vrefp | 外部供給基準電圧 | 1.2 | 1.25 | 1.3 | V |

注意:

1) この表の情報は、Mouserのデータシートに掲載されています。Spartan-7 FPGAデータシート: DCおよびACスイッチング特性

表2は、現在市場で提供されているさまざまなFPGAのコア / 補助電圧と入力 / 出力電圧の情報を示しています。表に記載されているデータは、列1に記載されている特定のFPGAモデルのデータシートから取得されたものです。

表2: 一般的なFPGAの比較(2)

| FPGAモデル | コア電圧幅 (許容値) (V) | 補助電圧幅 (許容値) (V) | 電圧幅 (許容値) (V) |

|---|---|---|---|

| Spartan - 7 | 1.0 (50mV) - 5% | 1.8 (5%) | 1.2~3.3 (5%) |

| Spartan - 7 (-1LI) | 0.95 (30mV) - 3% | 1.8 (5%) | 1.2~3.3 (5%) |

| Artix - 7 | 1.0 (50mV) - 5% | 1.8 (5%) | 1.2~3.3 (5%) |

| Artix - 7 (-2LE) | 0.9 (30mV) - 5% | 1.8 (5%) | 1.2~3.3 (5%) |

| Kintex - 7 (-2LI) | 0.95 (20mV) - 3% | 1.8 (5%) | 1.2~3.3 (5%) |

注意:

2) この表の情報は、Power Electronics NewsのFPGAアプリケーションの強化の記事に掲載されました。

どちらの表も、電圧規制が厳しく、許容誤差が最近のほとんどのケースで±3%近くあるため、設計された電源は正確な電圧特性を提供する必要があることを示しています。これらの規制を達成するための可能な方法の 1つは、マルチフェーズ電源方式を使用することです。

マルチフェーズ電源方式

システムの基本周波数は、使用される位相の数によって実質的に乗算されます。これにより出力のリップル周波数が増加し、基板スペースが小さくなり、出力容量が低くなり、高い電流能力につながります。

ASICおよびFPGAアプリケーションで使用される降圧型コンバータは、高速な過渡応答を備えている必要があります。つまり、入力から出力にエネルギーを素早く転送できる必要があります。並列コンバータを使用して負荷に電力を供給することにより、各ブランチは等しい位相シフトで動作します。これにより、定常電圧リップルと入力および出力 RMS電流が削減されるため、ソリューションに必要な入力と出力の容量が少なくなります。

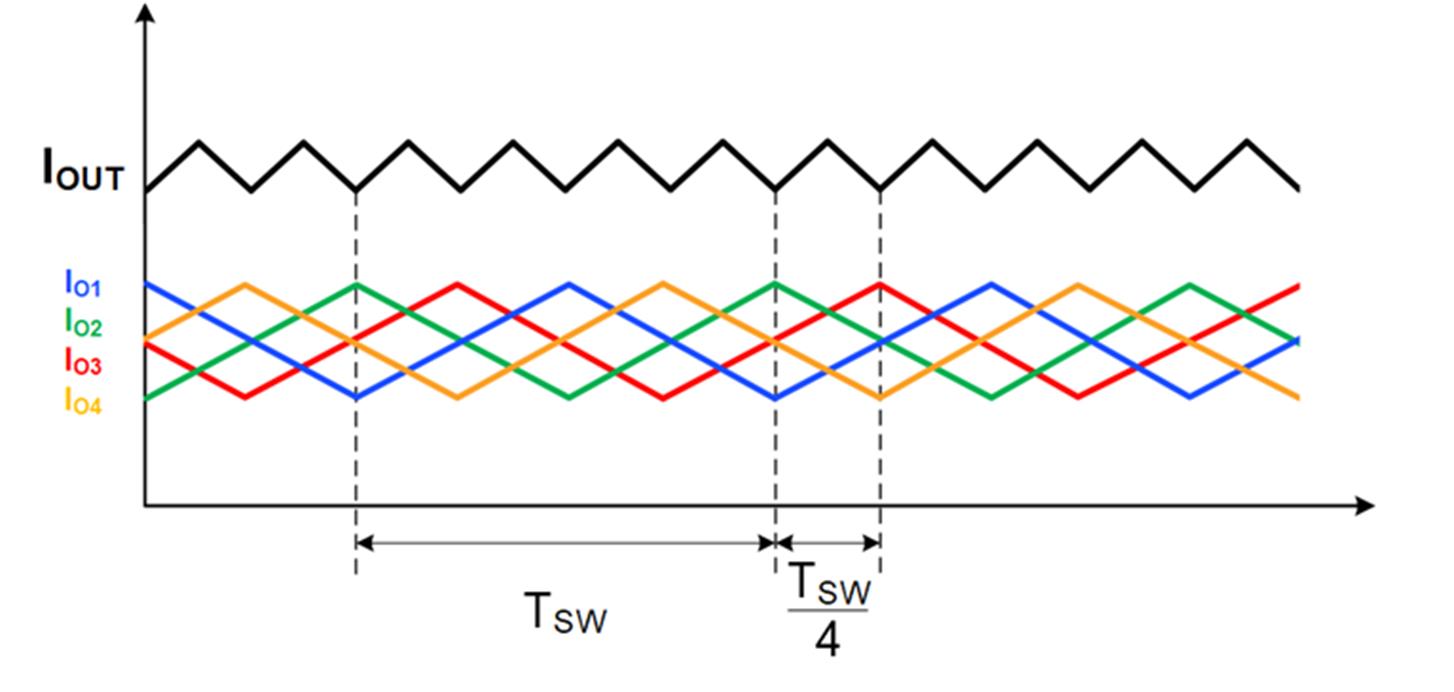

この方法を使用すると、電流リップルを効果的に低減し、より小型のインダクタを使用できるようになり、過渡電圧スパイクも低減されます。周波数乗算効果によると、リップルの振幅はN個の ブランチ (位相) で分割され、その周波数はN倍大きくなります。例えば、4相のアプリケーションでは、合計インダクタ電流リップル (IOUT = IO1 + IO2 + IO3 + IO4) は個々の位相の4分の1の大きさで発生し、リップル周波数は個々の位相の4倍の大きさになります (図1参照)。

図1: 4相アプリケーションの合計電流リップル

マルチフェーズコンバータの課題

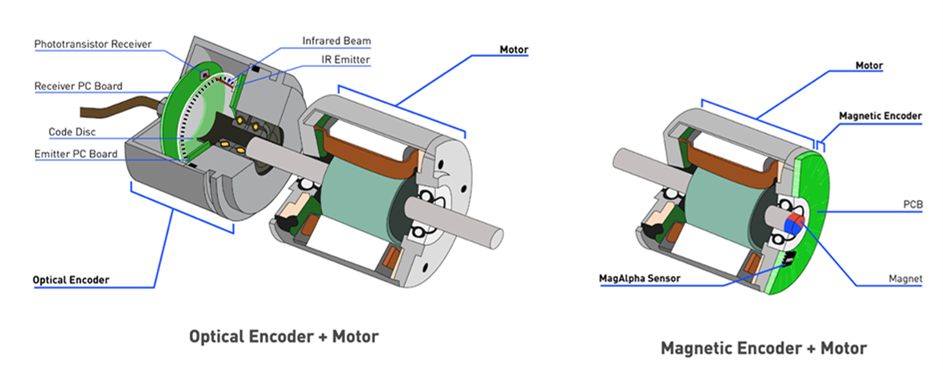

マルチフェーズコンバータは、非常に高速な応答時間で高電力レベルを実現するための鍵です。ただし、FPGAやASICなどのアプリケーションでは、システムに必要な電力は大きく変動します。MPSは、ディスクリートのソリューションとモジュールソリューションの両方の選択肢を提供します。ただし、モジュールは設計が容易で、ボードスペースの消費が少なく、ディスクリートのソリューションと比較すると、モジュールはコントローラと3つのインダクタを備えた3つのDrMosで構成されているため、設計の複雑さが大幅に軽減されます。たとえば、処理負荷がピークになると、出力電流の需要が100Aまで急増する場合があります。逆に、アイドル時または低負荷時には、電流は10Aまで大幅に低下する可能性があります。

さらに、モジュールは、電流シェアリング、位相インタリーブ、電力供ネットワーク (PDN) の導入、入出力容量の最適化など、他の利点ももたらします。

マルチフェーズ構成のセットアップ

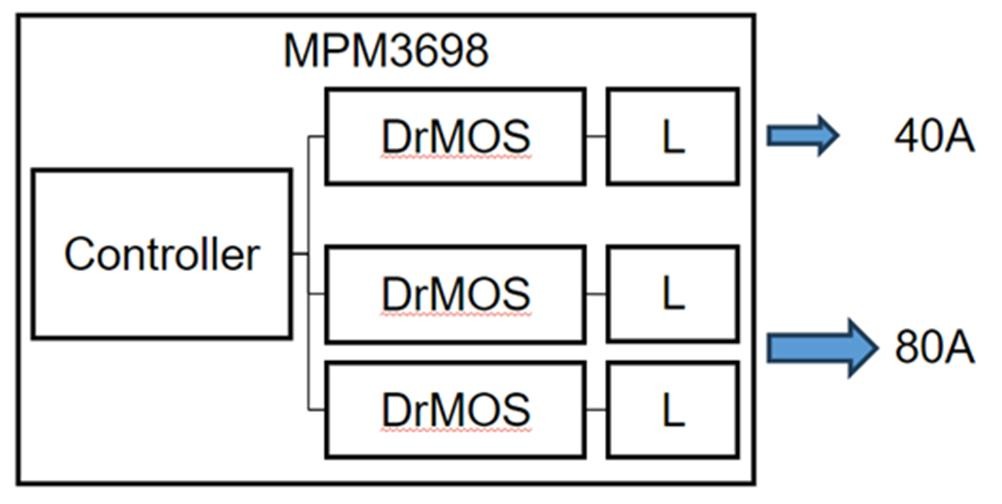

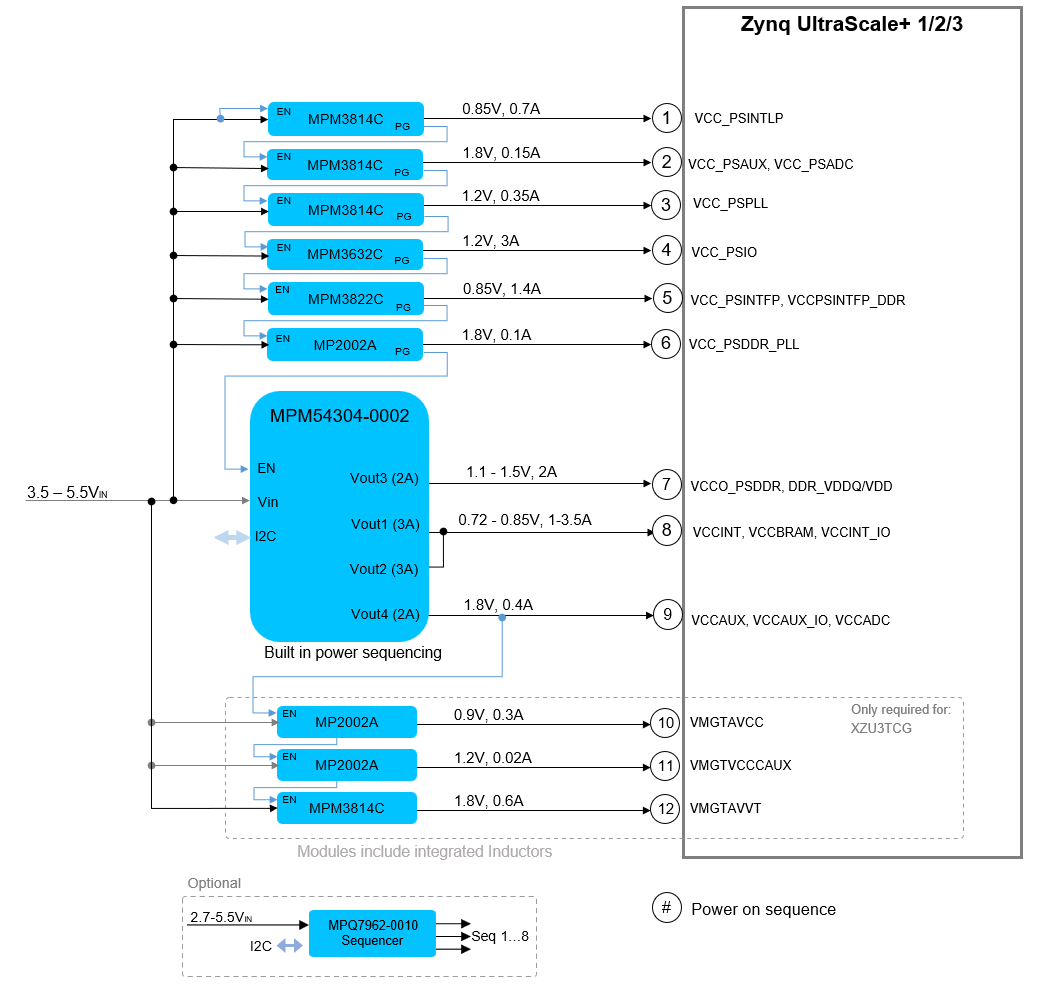

MPM3698は、デジタルインタフェースを備え、機能集積したシングルピークの120Aまたはデュアルピークの80A + 40Aの電源モジュールです。これは、VR14互換のデュアルループ、デジタルマルチフェーズコントローラと、3セットのドライバMOSFETおよびインダクタを搭載しています。MPM3698は、MPSが特許を持つデジタルノンリニア制御方式を備えており、最小限の出力容量で超高速過渡応答を実現します。

MPM3698の各位相は、最大40Aのピーク電流と30Aの連続電流を供給できます。3相の出力を並列接続でき、最大120AのピークIOUTまたは90Aの連続IOUTを供給します。

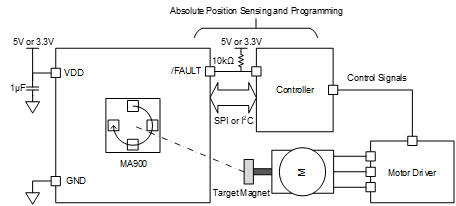

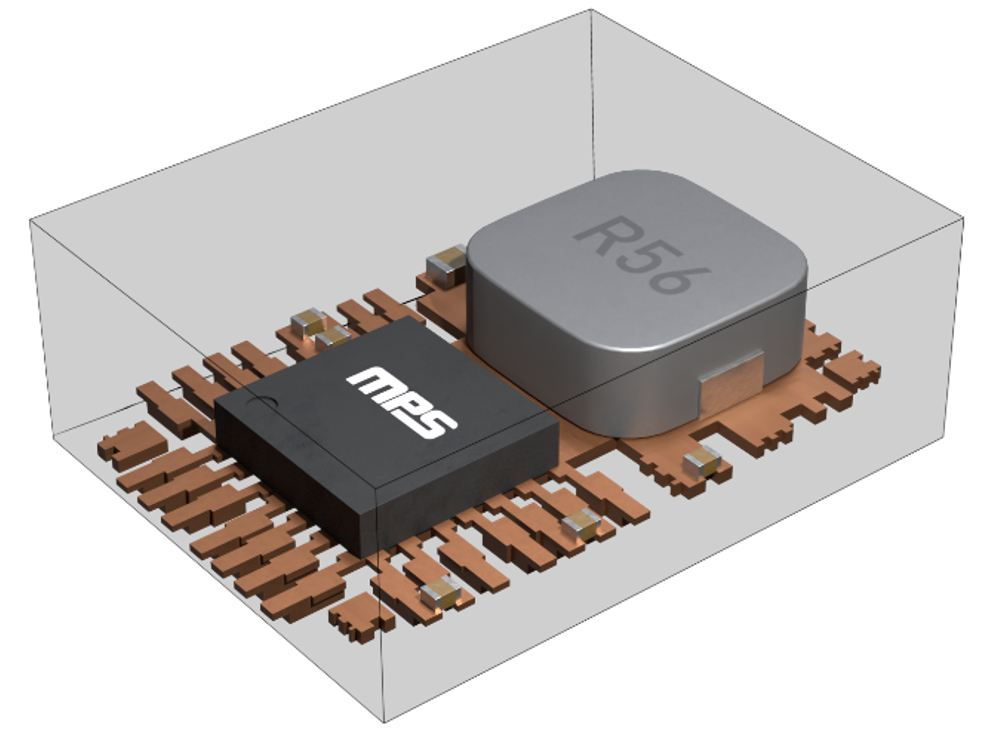

図2はMPM3698の内部セットアップを示しています。各MPM3698モジュールは3つのDrMOSとコントローラで構成されており、合計120AのIOUTを実現しています。

図2: MPM3698内部セットアップ

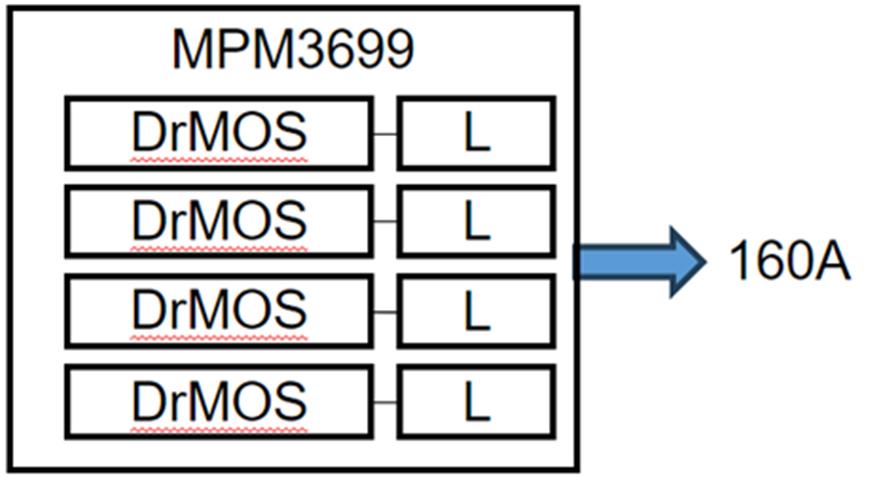

PWMコントローラ接続を介して外部 DrMOS として機能する追加モジュール (MPM3699 など) を実装すると、MPM3698のみを使用する既存の構成よりも多くの位相が可能になります。MPM3699電源モジュールを使用すると、IOUTは560A以上に達することができます。

MPM3699は4つの内部DrMOSモジュールを搭載しており、最大160AのIOUTを生成できます。図3はMPM3699の内部セットアップを示しています。

図3: MPM3699内部セットアップ

MPM3698 負荷過渡試験

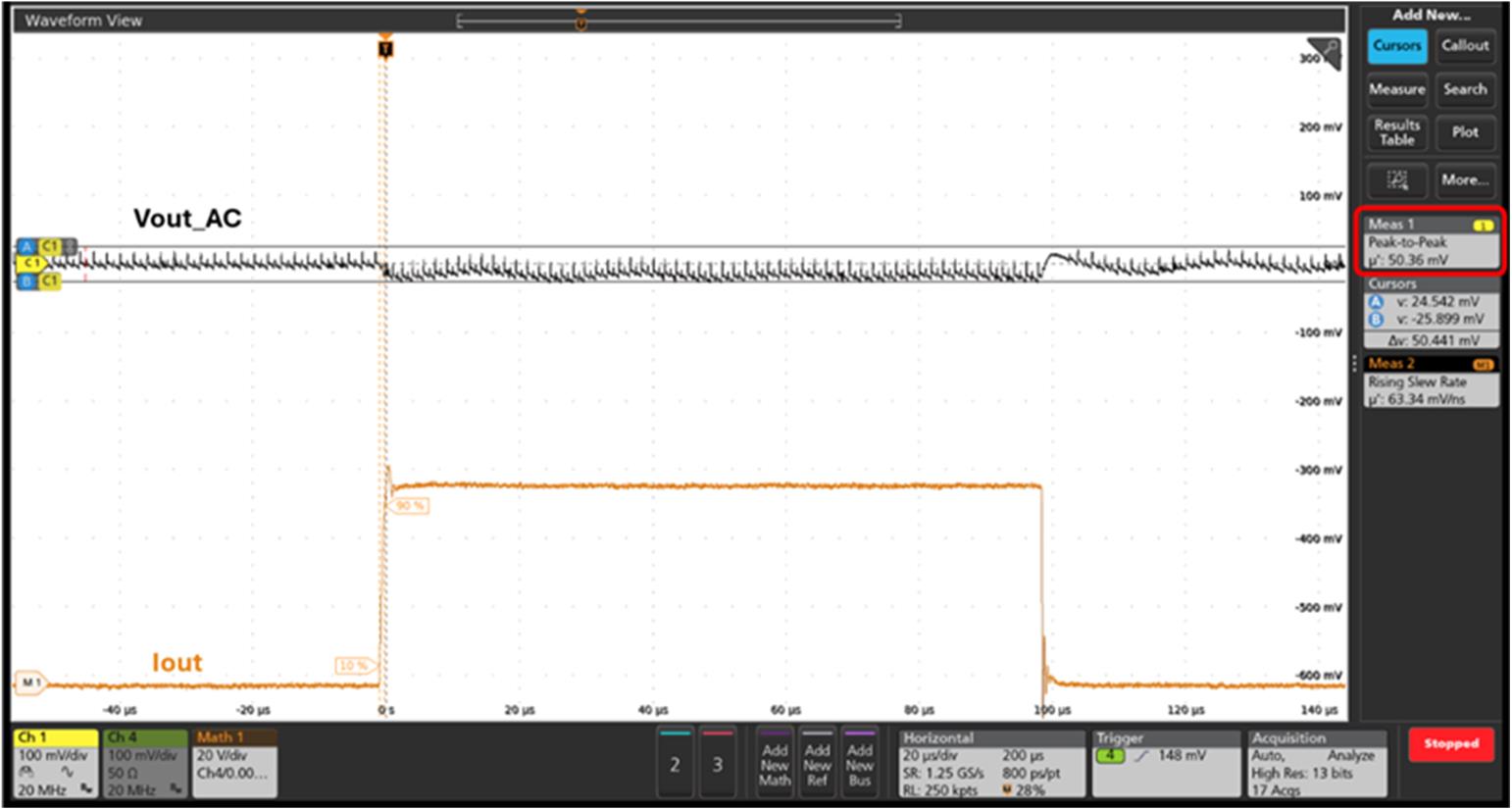

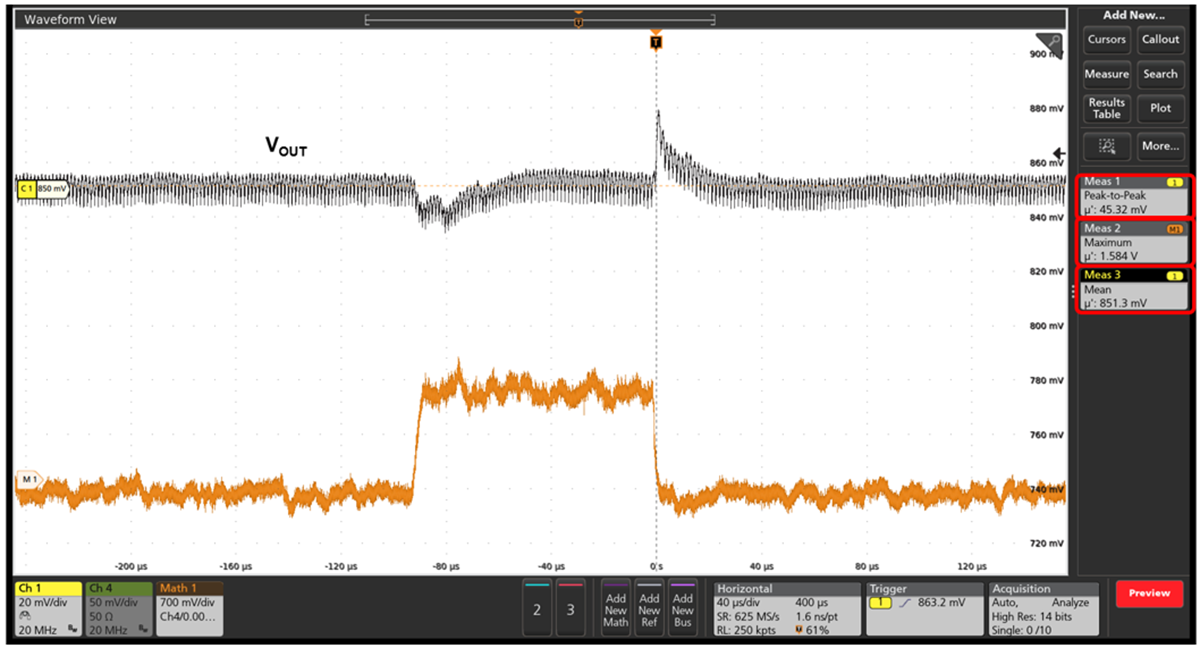

負荷過渡時の出力電圧許容差と安定性は、FPGAおよびASICアプリケーションにとって最も重要なパラメータの 1つです。負荷過渡試験の場合、出力コンデンサの総数は 47個で、各コンデンサの容量は47μFなので、合計2.2mFのMLCC 容量になります。さらに、4つの POSCAP が使用され、各コンデンサは330μFです。これにより、POSCAPの静電容量は合計1.32mF になります。

負荷過渡試験条件には12V VINは出力で0.85Vに変換され、最大電流は60Aで、2つの位相に分割され、0Aから60Aの幅です。この試験では、システムの素晴らしい過渡応答を示しており、出力電圧 (VOUT/AC)が ±3% (または ±30mV) の許容幅内に収まるようにします (図4参照)。これはFPGAのVCOREレールの標準要件です。

図4: 過渡試験 (1モジュール、2相、負荷過渡 = 0A~60A、ピークツーピーク電圧は±30mV許容幅以内)

負荷過渡解析から、MPM3698はFPGAコア電圧レールの過渡応答に関する厳しい規制要件を満たしており、0.85VのVOUTで、ピークツーピーク値が50.36mVであり、これは、I/O電圧許容値の3% (または±30mV) 以内です。

結論

FPGAおよびASICの電源に対しては注文が多く厳しい要求があるため、高性能デバイスに電力を供給するにはマルチフェーズ降圧型コンバータが不可欠になっています。マルチフェーズアプローチを実装すると、高電流能力を備えた低電圧を供給できます。マルチフェーズ電源は、高速な過渡応答を提供し、±3%の許容誤差内で厳密な電圧調整を維持する機能を備えています。これは、最新のFPGAおよびASICのコアおよび補助電源レールにとって不可欠です。

MPM3698は、MPS 独自のデジタルマルチフェーズノンリニア制御方式を採用しており、負荷過渡に対する超高速過渡応答を提供します。さらに、小さなソリューションサイズで設計のシンプルさと柔軟性を実現しています。複数の位相に電力を分散させることで、MPM3698やMPM3699などのデバイスの効率が向上し、熱ストレスが軽減され、必要な入力容量と出力容量が小さくなります。優れたインタリーブと高いパフォーマンスを実現するには、に関するMPSのカタログをご覧ください。

_______________________

興味のある内容でしたか? お役に立つ情報をメールでお届けします。今すぐ登録を!

アカウントにログイン

新しいアカウントを作成