デュアル出力モジュールを使用したFPGAへの電力供給

役立つ情報を毎月お届けします

プライバシーを尊重します

はじめに

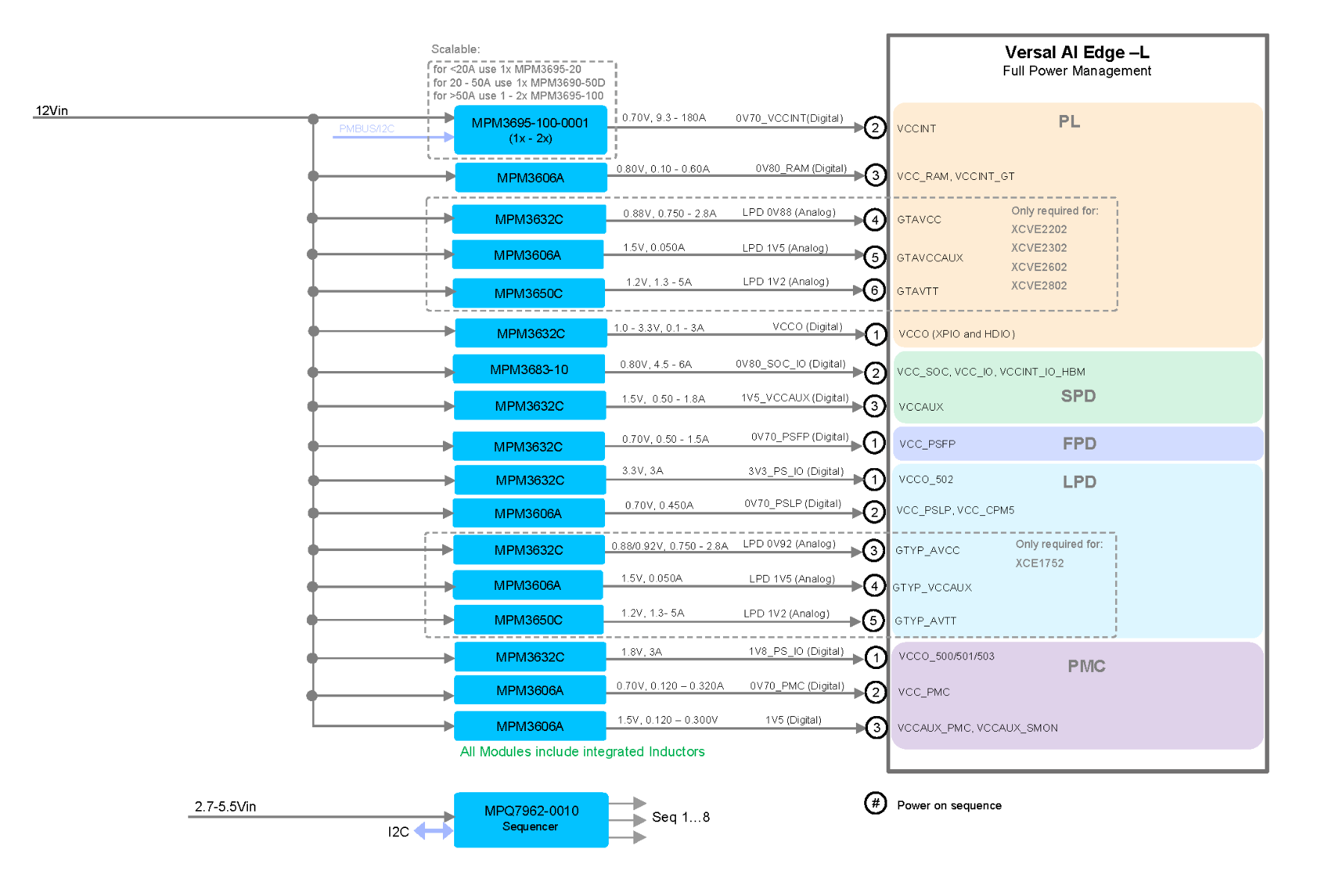

電気通信システム、データストレージ、フィールドプログラマブルゲートアレイ (FPGA) の需要の高まりにより、電力供給の複雑さと要件、特に 電圧レギュレータ (VR) 要件が増加しています。VRアプリケーションのほとんどの分野では、効率、I/O電圧幅、電圧許容値、サイズのバランスが必要です。FPGA電源レールの要求を満たすと同時に、正確な電圧制御を提供することが重要です。

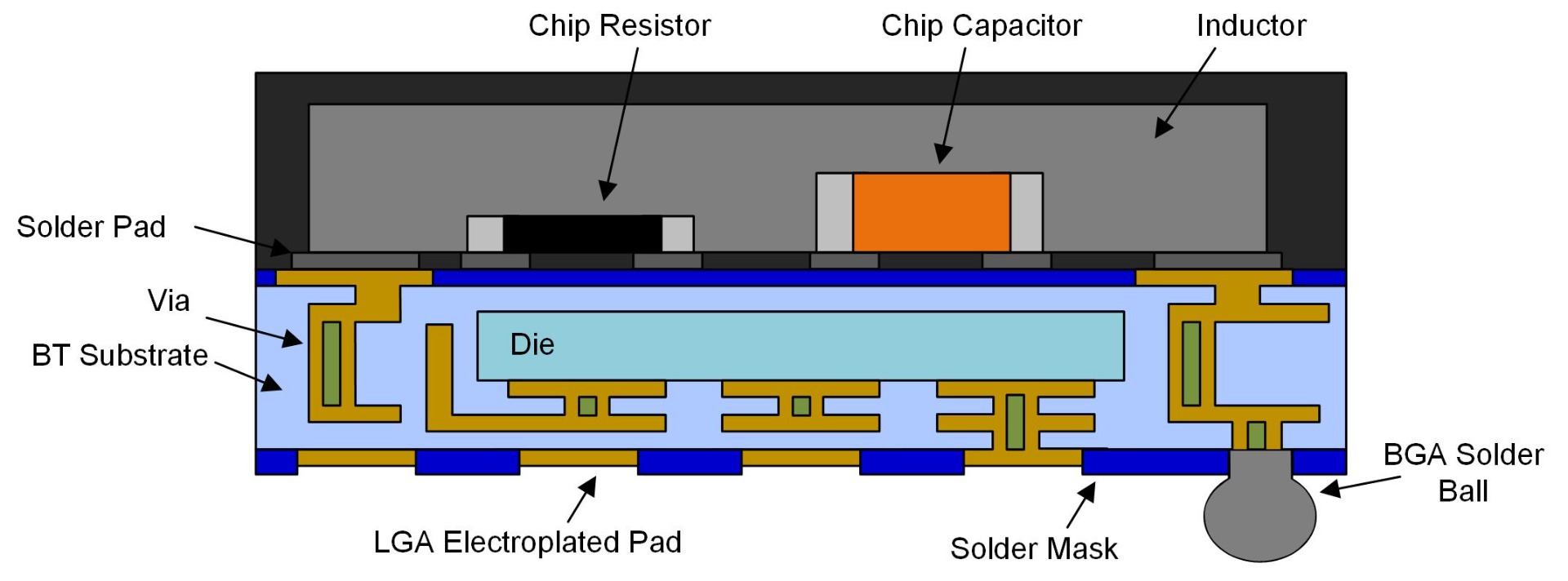

電源レールの数が増加するにつれて、設計者は大電流レールと低電流レールの両方のソリューションを見つける必要があります。多相電源ではインダクタサイズの要件を低減しながらより高い電流供給を実現し、多出力電源では単一のICで複数のFPGAレールに電力を供給できます。その結果、設計者は基板面積を削減し、設計を簡素化することで、電力供給に関する最新の要件をすべて満たすことができます。

本稿では、 デュアル出力電源モジュールであるMPM54322を使用してFPGA電源レール要件を満たすために複数出力電源を使用する方法について説明します。FPGAに電源を供給する際の重要な考慮事項には、電圧レールのレギュレーション、FPGA電源レールの適切な起動と安全シャットダウンが含まれます。

FPGA電圧レールレギュレーション

負荷過渡と電圧リップル

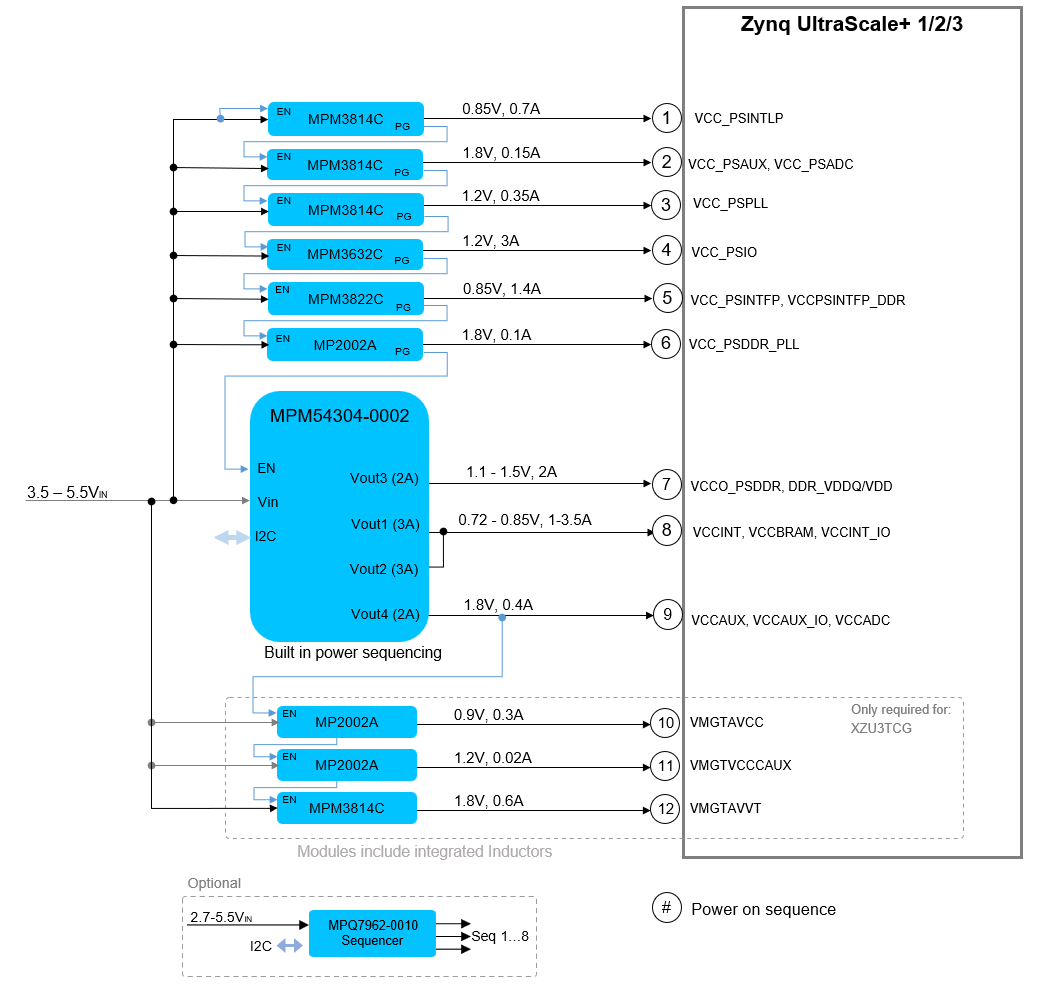

現代のFPGAでは、電圧と電流の要件が変化する多くの電源レールが必要です。高度なFPGA設計では、ダブルデータレート (DDR) メモリ、高速トランシーバ、その他の周辺機器などFPGAの機能に応じて、最大8本の電源レールが必要となることがよくあります。ほとんどのFPGAベースのシステムは12Vバスで供給され、FPGAの電源レールに必要な電圧は0.65Vから3.3Vの間で変化します。

電圧リップル耐性は、FPGAに電力を供給するための最も厳格な規制の1つとして電源設計の主な目的です。許容値はメーカーのデータシートに規定されていますが、一般的に電圧リップル許容値は定格電圧の±3%または±30mVを超えてはいけません。

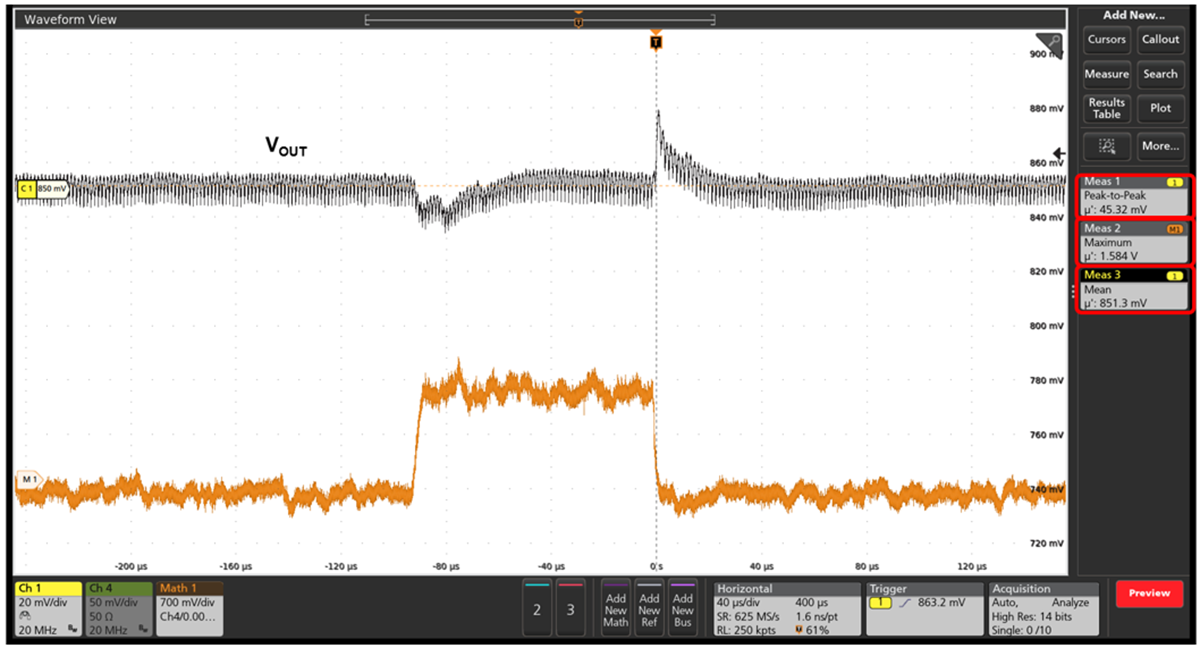

このような要件を満たす複雑さは、MPM54322、3A、デュアル出力電源モジュールで実施された負荷過渡試験で実証することができます。FPGAの動作をよりよくエミュレートするために、過渡は負荷スラマーを使用して生成され、これは最大130A/µsの非常に高いスルーレートで負荷ステップを実行します。

負荷過渡試験では、負荷は0Aから1.5Aにステップアップし、モジュールの3A出力のいずれかによって電力を供給されます。この試験は、入力電圧 (VIN) が12Vで出力電圧 (VOUT) が0.85Vで、最新のFPGA設計の最も一般的なコア電源レールをエミュレートするために実施されました (図1参照)。

図1: スラマー負荷時の負荷過渡値0A~1.5A

負荷過渡試験は、130A/μsの遷移中に±22.5mVの電圧ピークを持つ優れた過渡応答を実証しました。さらに、出力電圧リップルは、MPSの適応定オンタイム (COT) 制御により、FPGAコアレールの許容範囲内です。COT制御を使用することにより、電源は従来のピーク電流モード制御よりもはるかに速く負荷に必要なエネルギーを供給します。これにより、高い出力容量を必要とせず、電力過渡時に安定した電圧を維持することができます。

起動およびシャットダウンシーケンス

FPGAアプリケーションは、複数の電圧レギュレータに接続された複数の電源レールを持っています。基板の起動中は、システム効率を最適化し、起動電流のピークを最小限に抑えるために、レールを起動するための設定された順序を維持する必要があります。しかし、シーケンサの実装は基板スペースが非常に限られているため、実現可能な選択肢ではないかもしれません。MPM54322のような複数出力電源モジュールはMPS特許取得済みのフレックスタイマシーケンス制御を使用しており、シーケンサなしですべてのVRの起動と停止のタイミングを正確に制御することができます。

適切な起動の保証

ソフトスタート制御

ソフトスタート (SS) は、信頼性の高い起動を保証し、ICへの潜在的な損傷を防ぐためにFPGA電源レールにとって重要な要件です。この機能は、起動時のVOUT立ち上がり時間を制御する電圧レギュレータに実装されています。これは、電源レール上の容量性負荷が大きいため、FPGAの設計にとって特に重要です。SSがないと、起動時の突入電流が非常に高くなり、入力電源の電圧低下やFPGAや他の部品の損傷を引き起こす可能性があります。

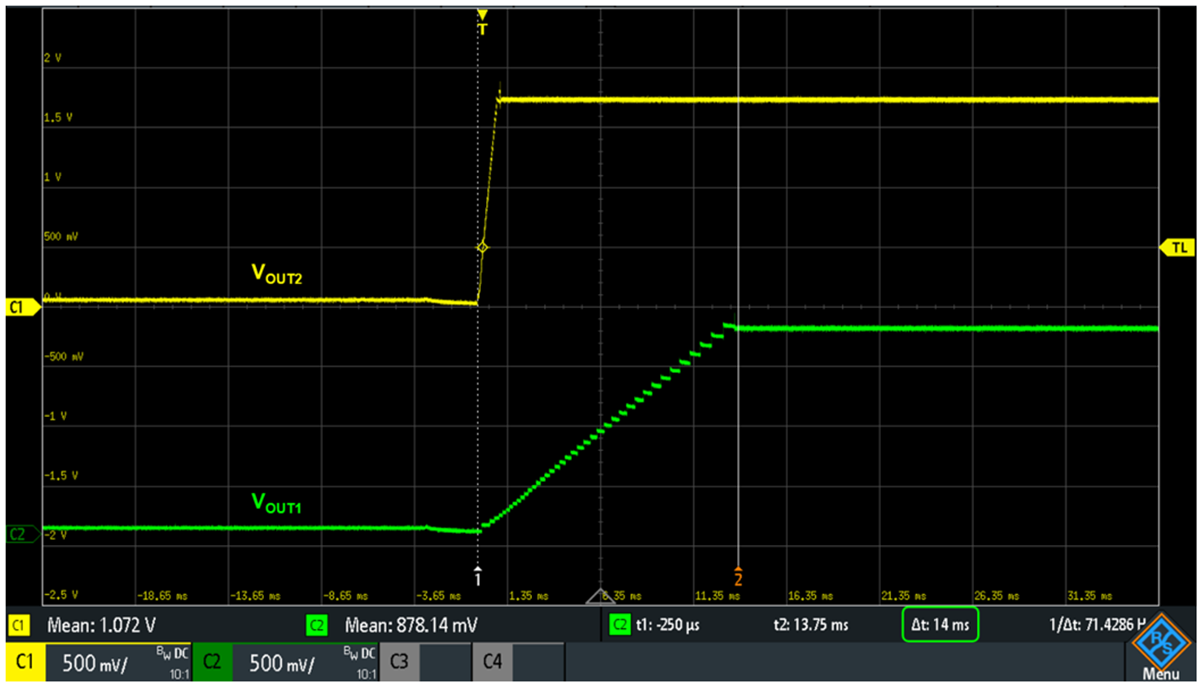

ほとんどのFPGAベンダーは、デバイスのソフトスタート時間 (tSS) を約10msと指定しています。tSSとともに電圧を徐々に増加させることにより、突入電流を制限し、スムーズな起動シーケンスを実現します。SSの要件を満たさないと、信頼性が低い起動、非単調な起動、FPGAへの損傷など、さまざまな問題が発生する可能性があります。

信頼性の高い動作を保証するためには、FPGAベンダーが規定するSS要件を満たすVRを選択することが重要です。MPM54322のようなレギュレータは、 FPGAおよび電源設計の特定の要件に合わせて微調整可能なtSSを提供します。

MPM54322は、 起動シーケンスでは1ミリ秒、長さ14ミリ秒のtSSを持つことができます (図2参照)。

図2: 2つの独立したレールを使用した起動シーケンス

MPS特許取得済みのフレックスタイマシーケンス制御

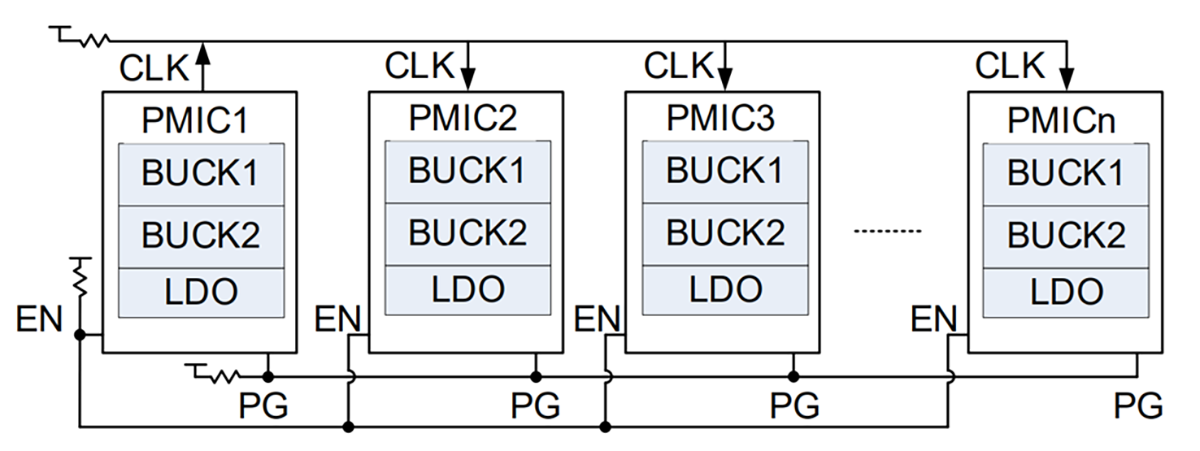

MPM54322はフレックスタイマシーケンス制御を使用して、異なる電源レールが開始される順序をよりよく制御します。このシーケンス制御方式は、すべての電力管理IC (PMIC) の制御信号がシーケンス調整のために接続されるマスター / スレーブ構造を使用します (図3参照)。

図3: フレックスタイマシーケンス制御

PMICの1つはクロック信号を生成するマスタとして設定され、他のPMICはクロック信号を受信するスレーブとして設定されます。すべての電源レールの起動およびシャットダウンシーケンスはクロック信号によって同期されます。

制御信号がアサートされると、起動シーケンスはマスタPMICがクロック出力を生成し、スレーブPMICがクロック信号をカウントするところから始まります。各電源レールについて、カウントされたクロック信号サイクルが事前に定義された遅延に達するとレールがオンになります。

マスタPMICのクロックサイクルがプリセット番号に達し、ステータス信号がイネーブルされたすべての電源レールがSS処理を完了したことを示すと、マスタPMICはクロック出力を停止し、スタートアップシーケンスが完了します。

シャットダウン中に制御信号が存在しない場合、マスタPMICはクロック出力の生成を開始し、スレーブPMICはクロック信号をカウントします。各電源レールについて、カウントされたクロック信号サイクルが事前に定義された遅延に達するとレールはオフになります。マスタPMICのクロックサイクルが設定値に達すると、マスタPMICはクロック出力を停止し、シャットダウンシーケンスは終了します。

このシーケンス制御方式は、追加のシーケンサモジュールを導入することなく、異なるPMICによって管理される複数の電源レール間で同期化された起動および停止プロセスを提供します。

アクティブ放電を使用した安全なシャットダウンの確保

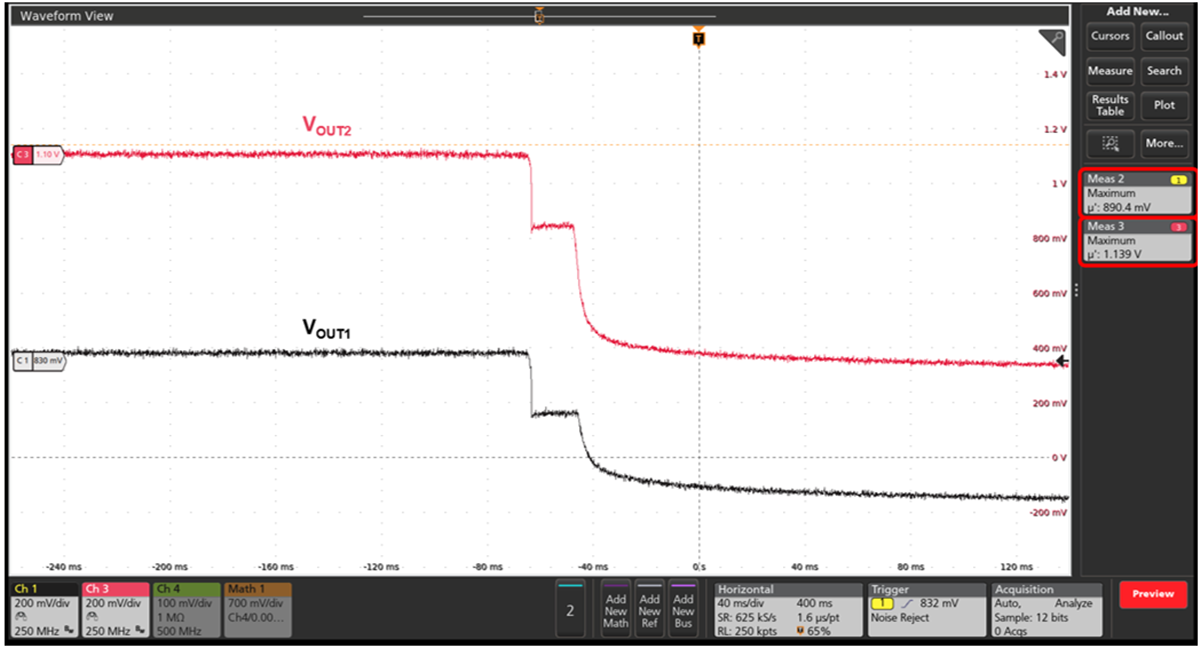

VOUTスパイクは、電源レールを介してFPGAに深刻な損傷を与える可能性があります。負荷が突然取り除かれると、出力コンデンサ (COUT) 内に蓄えられたエネルギー放電中に高電圧スパイクを引き起こす可能性があります。これらの危険を防ぐために、MPM54322は出力のアクティブ放電を実装します。

アクティブ放電の目的は、 負荷が突然取り除かれたり、電源が切れたりしたときにPMICのCOUTをすばやく放電することです。FPGA電源モジュールは安定性と最適な電圧レギュレーションのために大きなデカップリングコンデンサを使用するため、アクティブ放電はこれらのコンデンサを迅速に放電し、適切なシャットダウンシーケンスとタイミングを維持しながら電圧スパイクを防止するのに役立ちます。

アクティブ放電は、ICがディセーブルになり、内部デジタル・アナログコンバータ (DAC) の出力が下降するときに実行されます。VOUTは基準電圧とともに滑らかに下降します。DAC出力が850mVおよび650mVに達すると、これらのレベルで停止し、ソフトシャットダウンが完了します。出力はフィードバック抵抗を通して徐々に放電します。

図4にMPM54322のシャットダウンシーケンスを示します。

図4: MPM54322のシャットダウンシーケンス

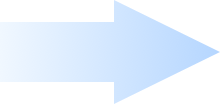

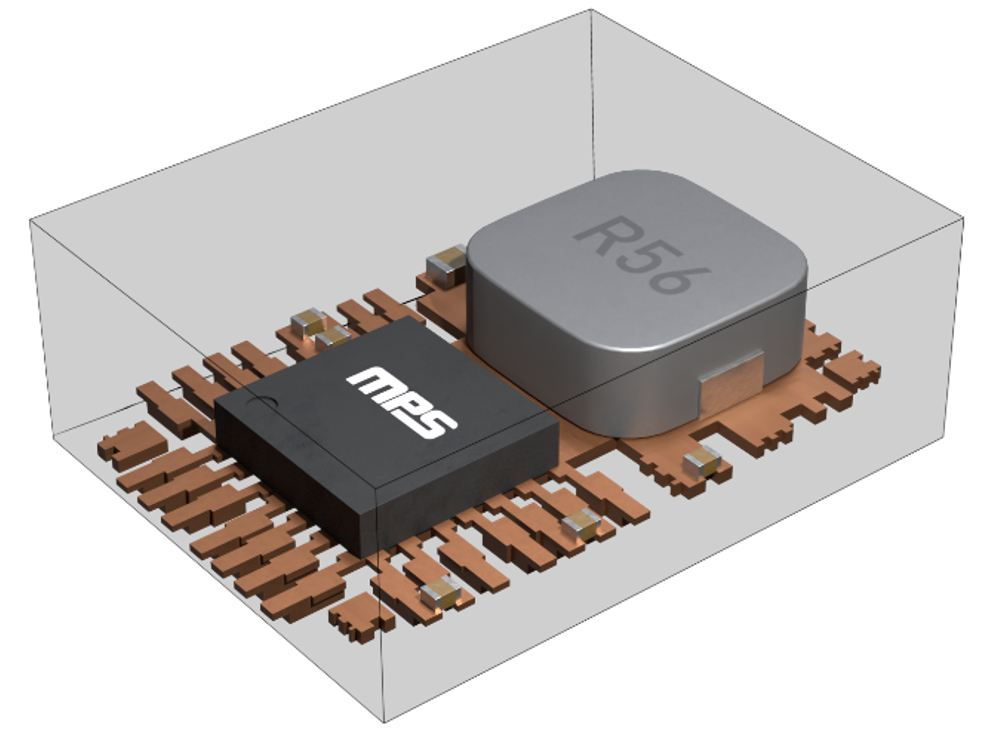

MPM54322の紹介

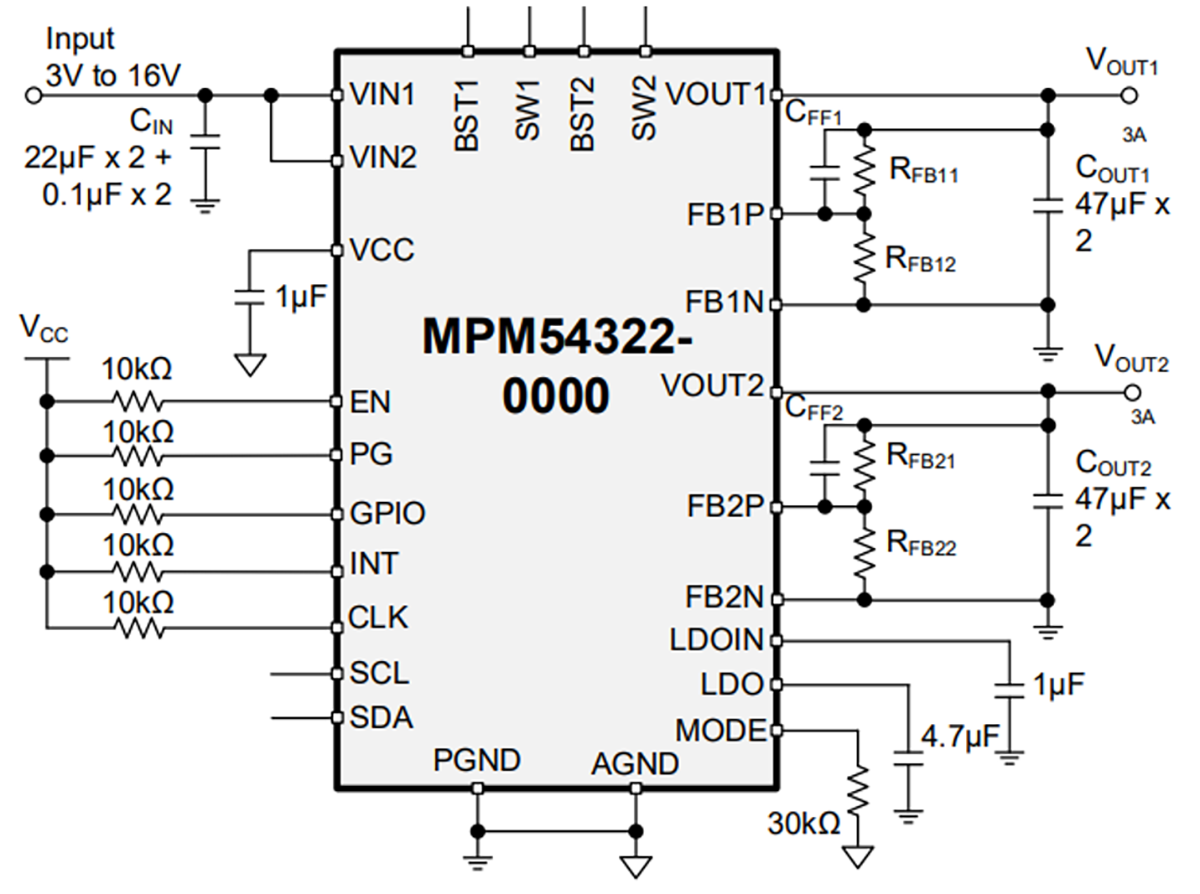

MPSは、柔軟でスケーラブルな複数出力電源モジュールを幅広く提供しています。MPM54322は3Aのデュアル出力パワーモジュールで、2つの高効率ステップダウンDC/DCコンバータIC、低ドロップアウト (LDO) レギュレータ、および受動素子 (DC/DCコンバータ用の2つのインダクタを含む) を1つのオーバーモールドパッケージに集積しています。MPM54322の2つの出力は、フィールドプログラマブルゲートアレイの2つの独立したレールに電力を供給するために別々に使用することができます。

図5は、MPM54322の代表的なアプリケーション回路を示します。

図5: MPM54322の代表的なアプリケーション回路

前述したように、FPGAシステムはFPGAとは関係のない別々のシステムのための多くのレールを含んでいます。同じ複数出力電源モジュールを使って他のサブシステムを起動することもできます。電圧と電流が異なる場合、デジタルサフィックスで区別されたICを使用すると、製造時やセットアッププロセス中に問題が発生し、FPGAに損傷を与える可能性があります。この問題に対処するために、MPM54322は最大10個のマルチタイムプログラマブル (MTP) ページ (MODEピンに接続された抵抗によって決定) を提供し、ユーザーは異なる電圧に対してプリセットの調整可能な構成を切り替えることができます。

結論

FPGAの消費電力の増加に伴い、先進的なFPGAアプリケーションに対応できる基板スペースを削減した電源を設計するために、高度な複数出力VRが必要です。

MPM54322のような高度な電源は、 高速過渡応答と正確な電圧レギュレーションを可能にし、さらにSSおよびMPS特許取得済みのフレックスタイマシーケンス制御を備えており、安全なシステムの起動とシャットダウンを保証します。さらに、システムがより複雑になるにつれて、MPM54322は設計者が同じICを使用して異なる出力設定のための10MTPページの中から簡単に選択することができます。

詳細については、MPSの電源モジュールのすべてのポートフォリオをご覧ください。

_______________________

興味のある内容でしたか? お役に立つ情報をメールでお届けします。今すぐ登録を!

アカウントにログイン

新しいアカウントを作成