MPSモジュールを使用したスマートFPGA電源ソリューション開発

役立つ情報を毎月お届けします

プライバシーを尊重します

はじめに

フィールド・プログラマブル・ゲートアレイ (FPGA) への電源供給は、ロジックセルの数が増えて複雑さが増すため、電源エンジニアにとって課題となります。これらの半導体デバイスは高度な構成が可能であるため、設計者はクロックとフェーズロックループ (PLL) 周波数を定義することに加え、それら内でロジック素子を構成することができます。さらに、ファームウェア、FPGAモデル、動作条件などの要因に依存するため、FPGAの消費電力の定義は複雑な作業になる場合があります。ほとんどのFPGAベンダーは、さまざまな条件に対するさまざまな電力消費目標を含む電力データを提供しています。FPGAは、通信、産業、自動車、医療機器用など、さまざまなアプリケーションで使用されるため、これは非常に重要です。

本稿では、Intel AgilexのFPGA電源設計と、MPSのすべて機能集積されたMPM3698とMPM3699モジュールが、どのように最も難しい仕様の1つである出力電圧 (VOUT) を非常に高速な電力過渡時に2%または3%以内の精度を保ち、どのようにソリューションスペースを最小限に抑えるのに役立つかに焦点を当てます。

FPGA電源の課題

効率的なスペースの利用は、コスト、パフォーマンス、電力消費に影響を与えるフィールド・プログラマブル・ゲートアレイの設計において重要な側面であり、電源エンジニアや設計者にとって重要な考慮事項になります。図1はFPGA電源の主な課題を示しています。

図1: FPGA電源の課題

FPGA電源レールには、ハードプロセッサシステム (HPS) と組み合わせたコアとトランシーバの2つの主なタイプがあります。FPGA内のこれらの個別の電源ドメインには、異なる設計の制約があります。コアとHPSレールは、さまざまな負荷と温度にわたって安定した精度を必要とし、ノイズに敏感なトランシーバでは、出力が特定のノイズレベルを下回る必要があります。

次世代のFPGAは、適切な機能を確保するために特定のシーケンスで起動またはシャットダウンする必要がある複数の内部電源ドメインで構成されています。これらの内部電源ドメインはいくつかのグループに分かれています。図2は、Intel Agilexのツリーグループの起動およびシャットダウンシーケンスを示しています。適切な電源シーケンスは、電圧スパイク、過剰な電流消費、タイミング違反につながる不安定クロック、損傷や誤動作につながる可能性のあるその他の電気的問題などの問題を防ぐのに役立ちます。

図2: Intel Agilex のツリーグループの起動およびシャットダウンシーケンス

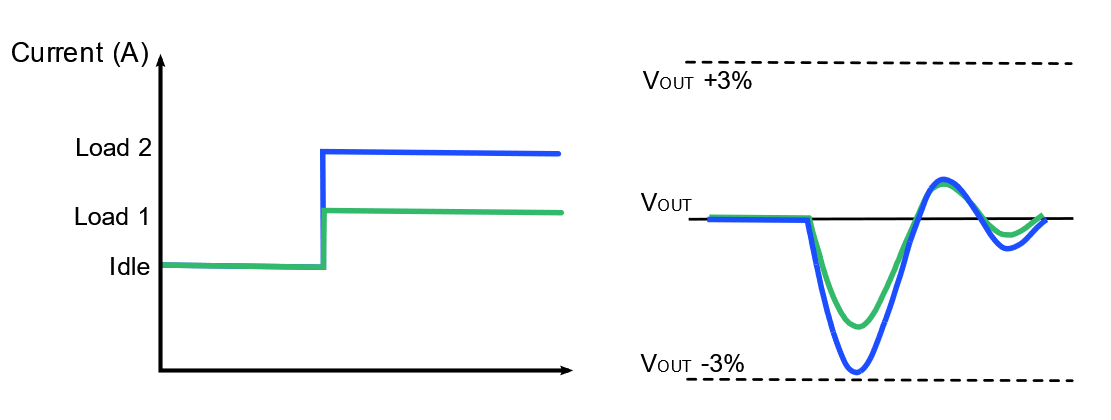

一方、出力電圧リップル (∆VOUT) または公称電圧仕様からの許容偏差に関して重要な考慮が必要であり、ほとんどのレールではVOUT精度は2%または3%以内である必要があります。これは、特にワークロードが動的に変化するアプリケーションや、デバイスのさまざまな部分が必要に応じて有効または無効化されるアプリケーションでは、最も困難なFPGA設計の制約の1つです。過度の電圧リップルは、特に敏感なアナログまたはミックスドシグナルアプリケーションでは、FPGAの動作に問題を引き起こす可能性があります。図3は、VOUTに大きな偏差を生じさせることがない負荷電流の変化を示しています (目標の±3%の許容内)。

図3: 出力電圧リップルと動的電力許容値

VOUTは電圧制御回路を使用して目標許容値内に維持されます。これらの回路は、指定されたレベルを満たすように電圧を調整し、FPGAおよび接続された部品のパフォーマンスと信頼性に影響を与える可能性のある不要な変動を防ぎます。最適なパフォーマンスを得るには、各FPGAレールの電圧レベル要件を指定された許容値内に維持することが重要です。さらに、VOUTを目標許容値内に維持することで、正確な信号処理とシステム内の他のデバイスとの互換性が保証されます。

消費電力の推定

ワークロードの変動は、多くのFPGAアプリケーション、特に通信、ソフトウェア定義無線 (SDR)、画像処理、エッジコンピューティングなどの分野でよく見られます。これらのアプリケーションでは、FPGAは変化するデータと処理要件に適応する必要があります。

最も優れたFPGAデバイスはダイナミックリコンフィギュレーションに対応しており、特定のタスクに合わせて複数のモード用にデバイスの機能をオンザフライで調整できます。ワークロードの変化を理解することで、電力消費量を推定および測定するという複雑なタスクが簡素化されます。電力消費量の推定は、設計の進化に応じて改良が必要な反復プロセスにまたがる場合があります。詳細な分析には、多くの場合、設計の機能、リソースの使用率、動作特性に関する特定の知識が必要です。これには、FPGAデバイスが電源から引き出して内部回路に分配する電流量を理解することも含まれます。FPGAデバイスの電流は、高速I/Oインタフェースの使用、外部負荷の駆動、またはデータ集約型のワークロードの処理によって、多数のロジック素子を有効化できます。

これらの各要因は、電力消費の増加に寄与する可能性があります。この状況では、安全で信頼性の高いFPGA動作を確保するために、ボードを設計するときに各レール用の適切な電流を定義することが不可欠です。これには現在の需要に対応する適切な 電圧レギュレータ、電源、および電力配電網の選択が含まれる場合があります。

ほとんどのFPGAベンダーは、最悪の場合の電力消費に基づくデバイス使用率を推定するツールを提供しており、FPGA設計者が設計の電力使用量を適切な精度で予測するのに役立ちます。これらのツールは、設計者が、電圧変動、過熱、または潜在的な損傷なしに、一貫したFPGA動作用に熱管理の決定を行えるように案内し、パフォーマンスと電力要件を満たします。全体として、デバイスの起動時の漏れ電流であるアイドル電力と、動作周波数から生じる動的電力を理解することが重要です。

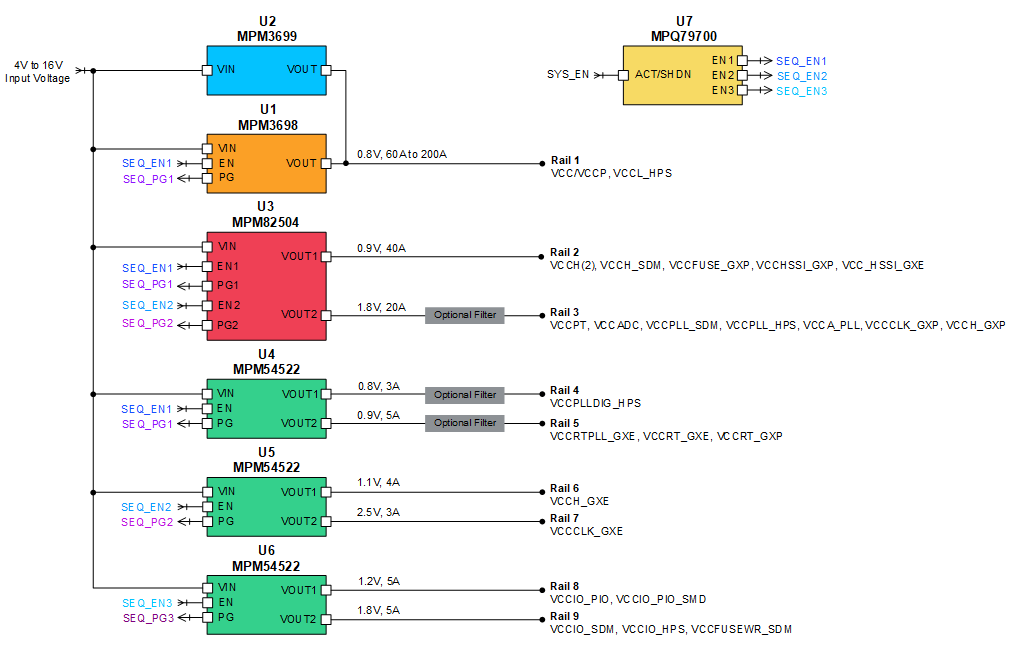

MPS電源モジュールを使用したAgilexパワーツリー

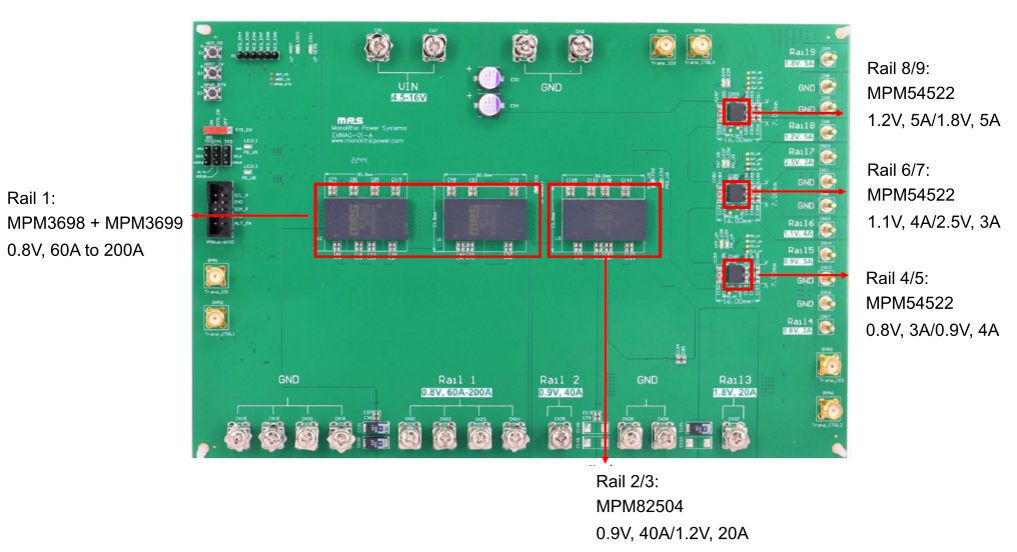

電源ツリーは、電源管理アーキテクチャをグラフィカルに表現したものです。このアーキテクチャでは、電源転送の入力電圧 (VIN) (通常は4V ~ 16V) がフィールド・プログラマブル・ゲートアレイに必要な電圧に変換され、デバイスの各部品が必要な電圧と電流が確実に受け取るようにします。図4は、完全なMPSソリューションを備えたIntel Agilex FPGA電源ツリーを示しています。レール1では、最大200Aの電流を処理できるMPM3698およびMPM3699モジュールが使用されます。このレールには公称0.8VのVOUTが必要で、最大許容誤差は±3% (DC + AC) です。

図4: Intel Agilexパワーツリー

MPSの機能集積されたモジュールは、コントローラ、電力段、インダクタ、およびほとんどの受動素子を1つのパッケージに搭載しています。このレイアウトは、回路の寄生インダクタンスと静電容量を減らし、PCBへの熱効率の高い接続性を向上し、システム全体の効率を高めるように最適化されています。

さらに、MPSの電源モジュールは、過電圧保護 (OVP)、低電圧保護 (UVP)、サーマルシャットダウンなどの故障保護機能に加え、アクティブ電圧ポジショニング (AVP)、自動フェーズシェディング、電圧識別 (VID) コード機能などの省電力技術も提供します。MPM3698のすべての機能はMPS Virtual Bench Pro 4.0ソフトウェアが完全に対応しており、ユーザーがさまざまなシステム要件に基づいてデバイスを構成するの役立ちます。

電源モジュールは、電圧レギュレータ、インダクタ、コンデンサなどのさまざまな部品を1つのモジュールに機能集積することで電源設計を合理化します。集積設計により、個別部品の数が最小限に抑えられ、全体的な設計プロセスが加速され、PCB上の入力コンデンサと出力コンデンサの選択が簡素化され、電源設計の全体的な効率が向上します。その結果、すべての電源モジュール設計を完了するには、PCB上で入力コンデンサと出力コンデンサのみを選択するだけで済みます。これにより、設計者はデジタル制御とシーケンスの利点を活かして、短期間で新しいアプリケーションを開発できるようになります。

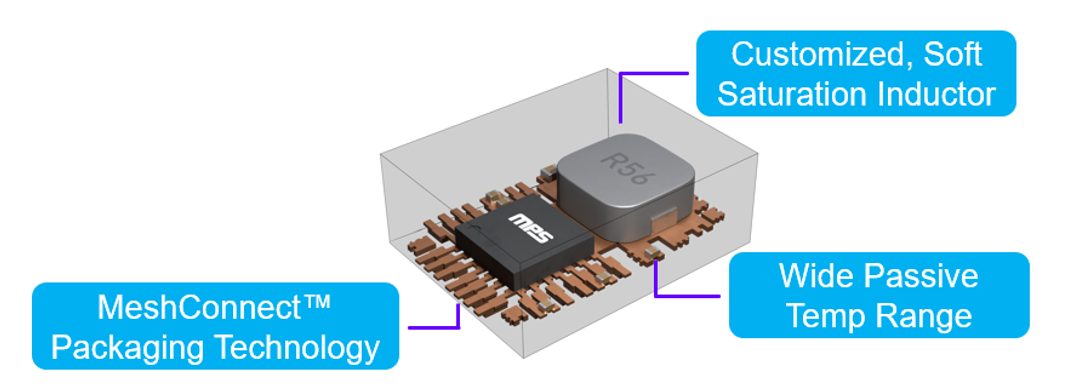

さらに、電源モジュールは共通のピン配置をもつ標準パッケージで提供されるため回路に簡単に統合でき、コンパクトな設計によりスペースが限られたアプリケーションに最適です。これらのモジュールは、FPGA、マイクロコントローラ、その他の電子デバイスの電源など、さまざまなアプリケーションで一般的に使用されています。図5は高精度受動部品を使用したモジュールレイアウトの例を示しています。

図5: 完全に機能集積されたモジュールレイアウト

高速電源過渡に対応する電源設計

フィールド・プログラマブル・ゲートアレイの柔軟性と構成可能性は、これらのデバイスの動的な電力要件を満たすために、電源と一致させる必要があります。FPGAの構成やモードが頻繁に変更されるアプリケーションでは、適応性が重要です。

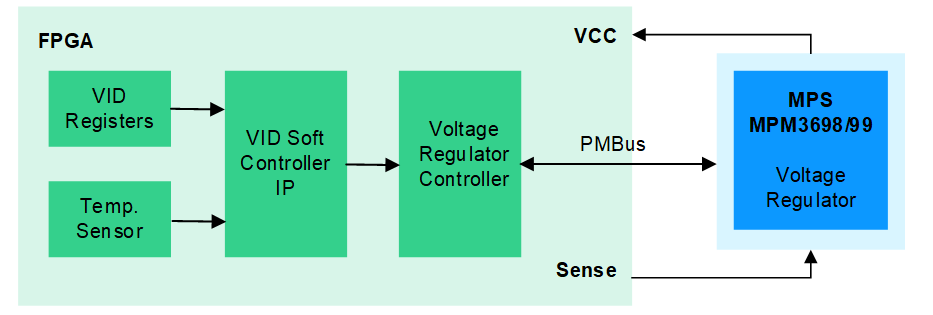

MPM3698およびMPM3699は、FPGA用のすべて機能集積されたMPSの電源モジュールであり、PMBusとAVSBusの2つの主要な通信プロトコルを組み合わせた高度な電源ソリューションを提供します。PMBusプロトコルを使用すると、電圧、電流、温度などの電源パラメータのリアルタイムモニタリングを可能にします。これにより、FPGAの厳格な電圧調整を満たすデジタル制御ループ構成が可能になり、激しい負荷ステップ中のフィードバックループ調整を可能にします。PMBusは、PMBusによる適応型電圧スケーリングを使用してプロセス変動を補正する電力最適化技術であるIntel Smart Voltage IDentification (SmartVID) もイネーブルにします。この技術は電力を節約し、エネルギー効率とパフォーマンスを最適化します。図6は、VCCレール全体にわたるSmartVID コントローラの一般的な構成を示しています。

図6: PMBusを使用してイネーブルになるIntel SmartVID

このケーススタディでは、インテルFPGA電力および熱計算ツールを使用して、Intel Agilexコア電圧 (VCC) および周辺電圧 (VCCP) 用の電力を推定します。ステップロードは次のように計算されます: トグルレートを15%と仮定して、コア使用率は80%、デジタルシグナルプロセッサ (DSP) 使用率は80%、M20Kメモリブロック使用率は30%。

表1は推定条件下での初期ステップ負荷とスルーレートを示しています。

表1: VCCとVCCPコア用のステップ負荷仕様

| dl (A) - ステップ電流 | dl/dt (A/μs) - スルーレート | |

| VCC VCCPコア | 32.5 | 325 |

さらに、Intel AgilexリファレンスデザインからのEVINAG-001-A FPGA評価ボードはMPSの電源モジュールの性能を評価するために使用でき、表1の仕様が満たされていることを確認できます (図7参照)。

図7: Intel Agilex用 EVINAG-001-A FPGA評価ボード

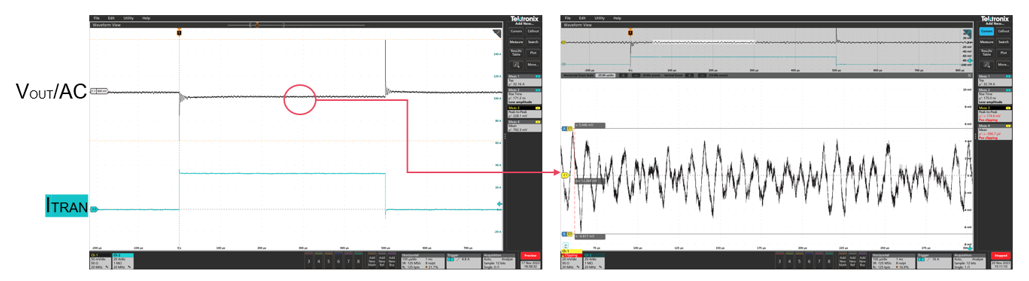

図8は、表1で与えられた仕様を使用したVCC / VCCPコアレール用の負荷過渡応答とリップル測定を示します。すべての必要な出力コンデンサは、32 x 47μFの積層セラミックコンデンサ (MLCC) と4 x 330μFのポリマーコンデンサ (POSCAP) です。

図8: EVINAG-001-A FPGA評価ボードを使用したMPM3698およびMPM3699の負荷過渡(∆IOUT = 32.5A、スルーレート = 325A/μs、VIN = 12V、VOUT = 0.8V、fSW = 500kHzでのVCC / VCCPコアレール)

図8では、負荷過渡時のピークツーピークVOUTが228.1mVであり、重負荷電流時の出力リップル測定値 (右の波形) は12.264mVです。これは±3%の最大VOUT許容値内です (DC + AC)。さまざまな負荷ステップ下でMPSのモジュールソリューションを使用したIntel Agilex FPGA電源ツリーの追加測定に対するEVINAG-01-Aテストレポートをご参照ください。

出力容量設計ガイドライン

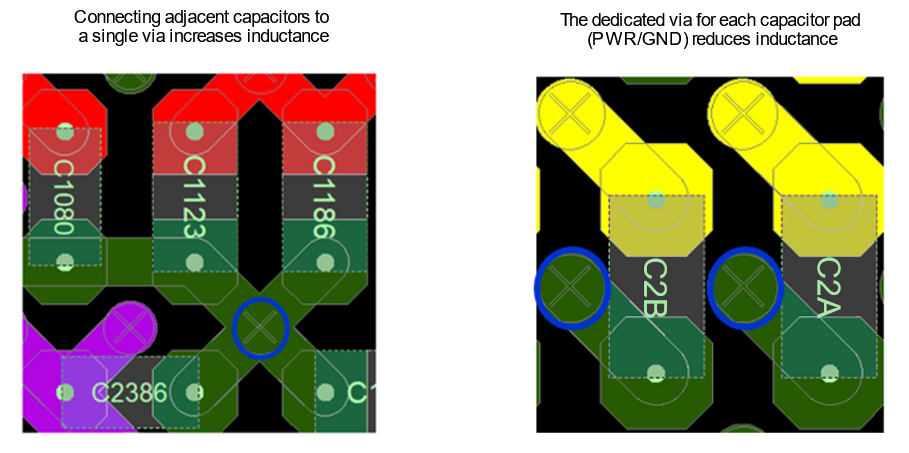

電力消費の動的な変化時に安定した電源を維持することは、信頼性が高く一貫性のあるフFPGAの動作にとって非常に重要です。安定した電源を実現するには多くの要因が影響します。負荷過渡時の制御ループの動作を最適化することで、電源のVOUTを規定の許容値内にとどまるためには、バイパスコンデンサとデカップリングコンデンサの適切な選択もVOUTを一定に保つ上で重要な役割を果たします。特に高速、高密度のPCB設計では、デカップリングネットワークの小さな改善がFPGAの全体的なパフォーマンスと信号の整合性に大きな影響を与える可能性があります。デカップリングコンデンサは、PCBレイアウト全体にわたって 戦略的に配置する必要があり、電源とグランドの接続を効果的にフィルタリングおよびデカップリングします。

さらに、すべてのコアBGAピンは高品質のセラミックコンデンサに直接接続する必要があります。従来の設計ガイドラインでは、デカップリングコンデンサをPCBの下側に配置することを推奨していますが、それに伴うトレードオフと考慮事項を理解することが重要です。スペースが限られた領域に追加の部品を搭載するには、同じビアを共有するようにコンデンサを割り当てる必要があります。ビアの寄生素子 (インダクタンスや抵抗など) はデカップリングネットワークの有効性に影響を与える可能性があり、ビアを共有すると全体的なパフォーマンスに影響を及ぼす状況もあります。図9は、FPGA設計に推奨されるコンデンサレイアウトを示しています。

図9: FPGA設計に推奨されるコンデンサレイアウト

結論

FPGA技術の進化は、通常、密度とパフォーマンスの向上と、電力消費とスペース要件の削減というトレンドに従います。スペースが厳しく制限されているFPGAアプリケーションでは、コンパクトな電源モジュールが、スペースを節約し、寄生素子が電力配電網 (PDN) に影響を与えるリスクを最小限に抑える貴重なソリューションを提供できます。コンパクトな電源モジュールは、個別の部品に比べて単価が若干高くなる可能性がありますが、部品数、組み立て時間、設計ミスのリスクが削減されるため、最終的にはコスト削減につながり、迅速なプロトタイピングと生産効率に特に有利です。

本稿では、MPM3698、そしてMPM3699を使ったFPGAソリューション用の電源モジュールについて説明しました。これは、レイアウトを削減し、受動部品を最適化し、パッケージのループを小さくするためEMIパフォーマンスが向上します。このソリューションは、安定した許容可能なVOUT許容値を提供するのに加え、非常に高速な電力過渡時にFPGAにクリーンな電力を供給します。MPSのステップダウン電源モジュールの全製品の中から、スマートなFPGA電源ソリューションに最適なオプションを見つけましょう。

_______________________

興味のある内容でしたか? お役に立つ情報をメールでお届けします。今すぐ登録を!

アカウントにログイン

新しいアカウントを作成