SPICEシミュレーションでの寄生インダクタンス効果を用いたVDSスイッチングスパイク予測

役立つ情報を毎月お届けします

プライバシーを尊重します

はじめに

電源産業界の主な目標の1つは、データセンターと5Gのようなアプリケーションのパワーデバイスに、より高い電力変換効率と電力密度をもたらすことです。ドライバ回路とパワーMOSFET (DrMOSとして知られる) をICに組み込むと、個別のドライバICを備えた従来のディスクリートMOSFETと比較して、電力密度と効率が向上します。さらに、DrMOSのフリップチップ技術により、応答時間を短縮し、ダイとパッケージ間のインダクタンスを低減することで、電圧レギュレータの性能を向上させます (図1参照)。

図1: 従来のワイヤボンド vs. フリップチップ技術

ただし、基板とPCBの寄生インダクタンスは、寄生インダクタンスとMOSFETの出力容量 (COSS) の間の共振特性により、ドレイン・ソース間電圧 (VDS) スパイクに大きな影響を与えます。高いVDSスパイクはMOSFETのアバランシェを引き起こす可能性があり、デバイスの劣化や信頼性の問題につながります。MOSFETのアバランシェ降伏を防ぐために、電圧ストレスを軽減する方法がいくつかあります。

1つ目の方法は、DrMOSに高電圧の二重拡散MOSFET (DMOS) プロセスを適用することです。このプロセスをパワーMOSFET設計に採用すると、同じ空間内の並列DMOSの数を低減することにより、DrMOS用のオン抵抗 (RDS(ON)) が高くなります。

2番目の方法は、スナバ回路を使用して電圧スパイクを抑制する方法です。ただし、この方法ではスナバ回路で余分な損失が発生します。さらに、スナバ回路を追加しても、共振動作を引き起こす浮遊インダクタンスは、主にDrMOSのパッケージに統合されるため、MOSFETのVDSスパイクが効果的に低下しない場合があります。

電圧レギュレータ効率を高めMOSFETの電圧スパイクを低減する場合、上記のトレードオフにより、PCBおよび基板上の寄生インダクタンスの影響を定量化し、最適化することが困難になる可能性があります。本稿では、まず寄生インダクタンスのモデリングについて説明します。次に、等価寄生回路モデルをSPICEシミュレーション ツールに適用して、VDSスイッチングスパイクを予測します。そして実験結果を示して寄生モデルの実現可能性を検証します。最後に、本稿ではDrMOS上の寄生インダクタンスの最適化についてさらに分析します。

関連コンテンツ

-

寄稿文

MPSの電源モジュールはザイリンクス Zynq UltraScale+ RFSoCにコンパクトで超低ノイズのソリューションを提供

ワイヤレスネットワークとデータセンターの帯域幅の増加によって駆動される高性能FPGAおよびASICアプリケーションが増加し、高電力密度、高速負荷過渡応答、およびインテリジェントな電源管理機能を備えた電力レギュレータが必要となります

-

ビデオ

サーバーアプリケーション向けの非絶縁型、2相ステップダウンIntelli-Module: MPC22163-130

MPC22163-130は、OAMフォームファクタのAIプロセッサ、FPGA、およびASICコア電源、PCIeアクセラレータカードなどのアプリケーション向けに設計された、130A、非絶縁、2相のステップダウンプロセッサintelli-moduleコア電源です

-

アプリケーション

5G用電源ソリューション

MPSはハイパワーデバイスに見合う製品で業界をリードする電力密度を提供します

-

寄稿文

Vcore DrMOS最適化のためのPCB上ACR損失の解析とシミュレーション

プリント基板 (PCB) のメインループリップル電流抵抗損失は、スイッチング電源損失要素として無視され、見落とされることが多いです

DrMOSでの寄生インダクタンスのモデリング

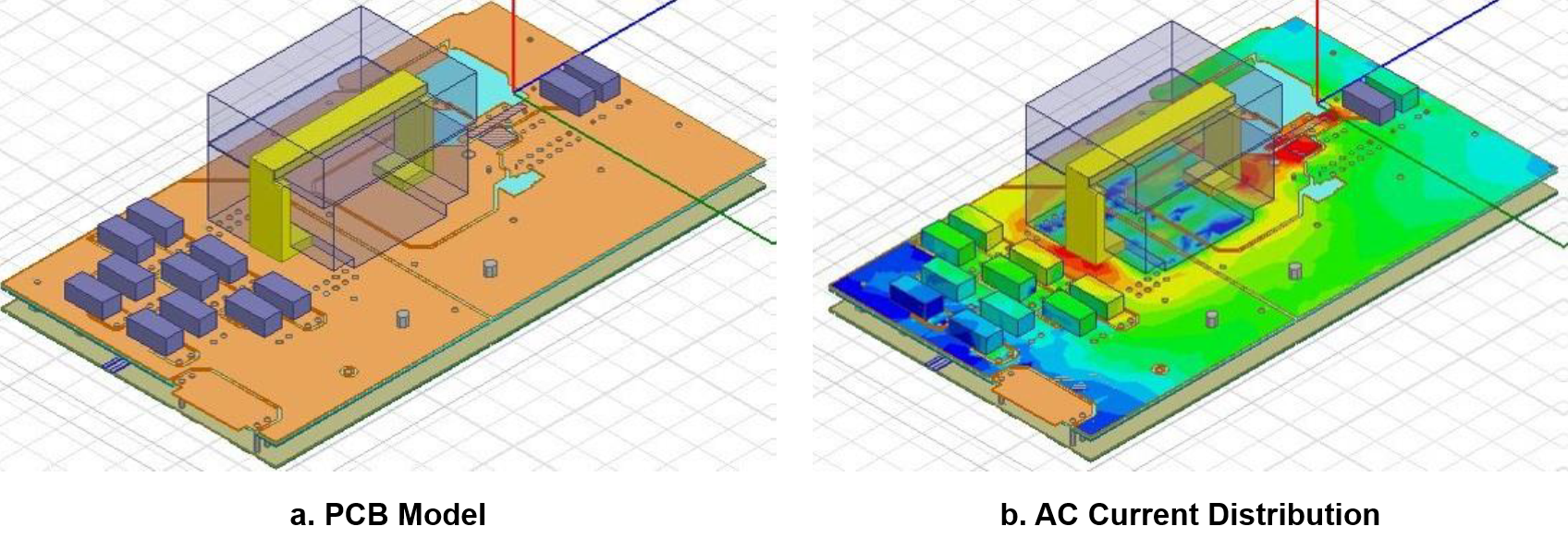

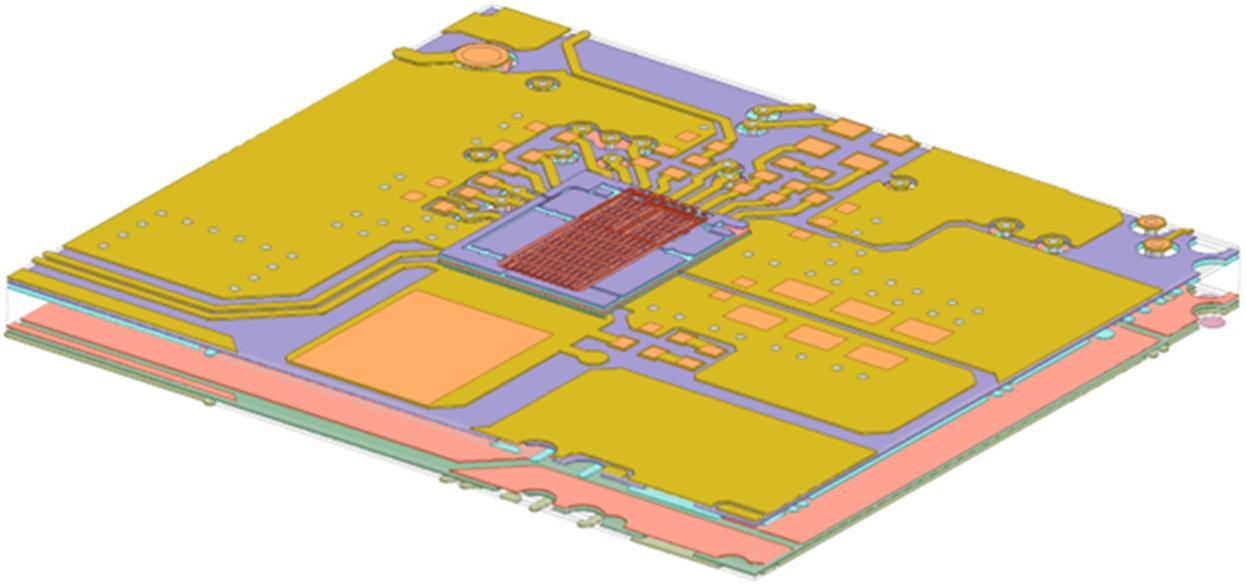

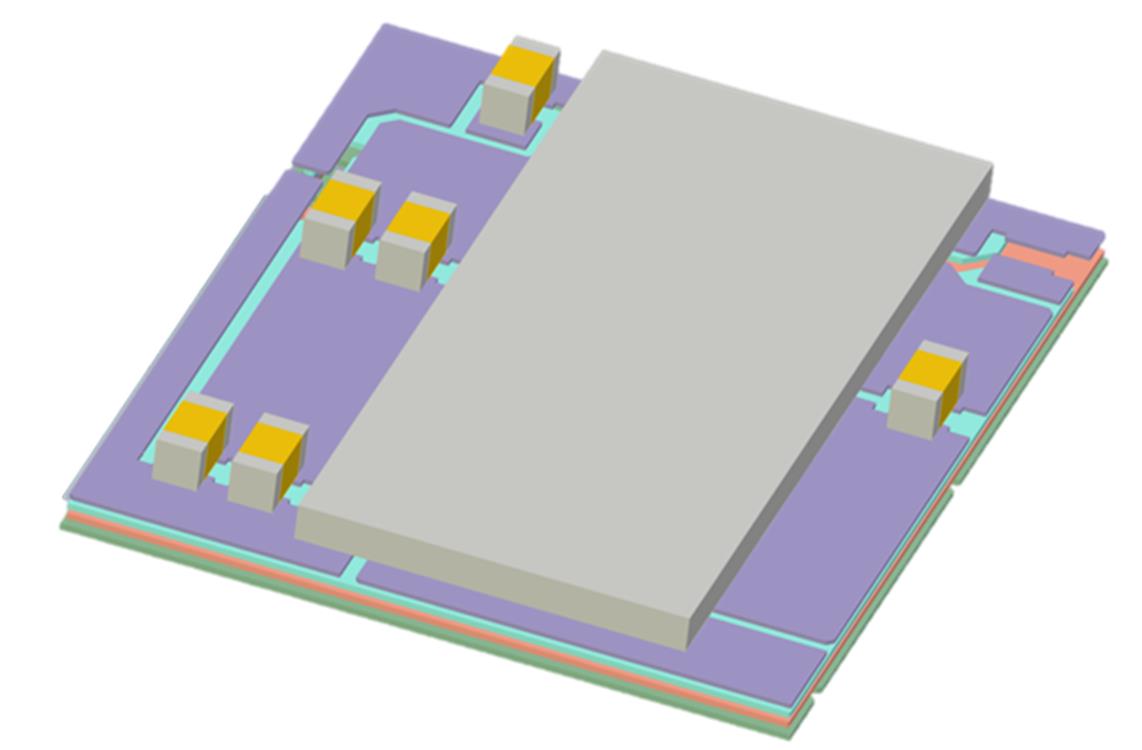

寄生インダクタンスをモデル化するために、DrMOSとPCBの両方の3D構造がシミュレーション解析用に構築されました (図2参照)。材料、スタックアップ情報、PCBおよびパッケージ層の厚さなどのパラメータは、モデリングの精度にとって重要です。

PCBとDrMOSを3Dモデリングした後、ANSYS Q3Dを介して寄生インダクタンスを特徴づけ、取得できます。本稿はMOSFETのVDSスパイクに焦点を当てているため、対象となる主なシミュレーション設定は、パワーネットとドライバネットの寄生パラメータです。

図2: DrMOSとPCBの3Dモデリング構造

Q3Dから得られる寄生成分を考慮する場合、DrMOS上の各ネットの自己インダクタンスと相互インダクタンスを含む寄生インダクタンス行列は、さまざまな周波数条件下で選択できます。?ハイサイドMOSFET (HS-FET) とローサイドMOSFET(LS-FET)でのVDS用の共振周波数は 300MHz~500MHzなので、300MHzの条件下での寄生インダクタンス行列がさらなる動作モデルシミュレーション用に採用されています。

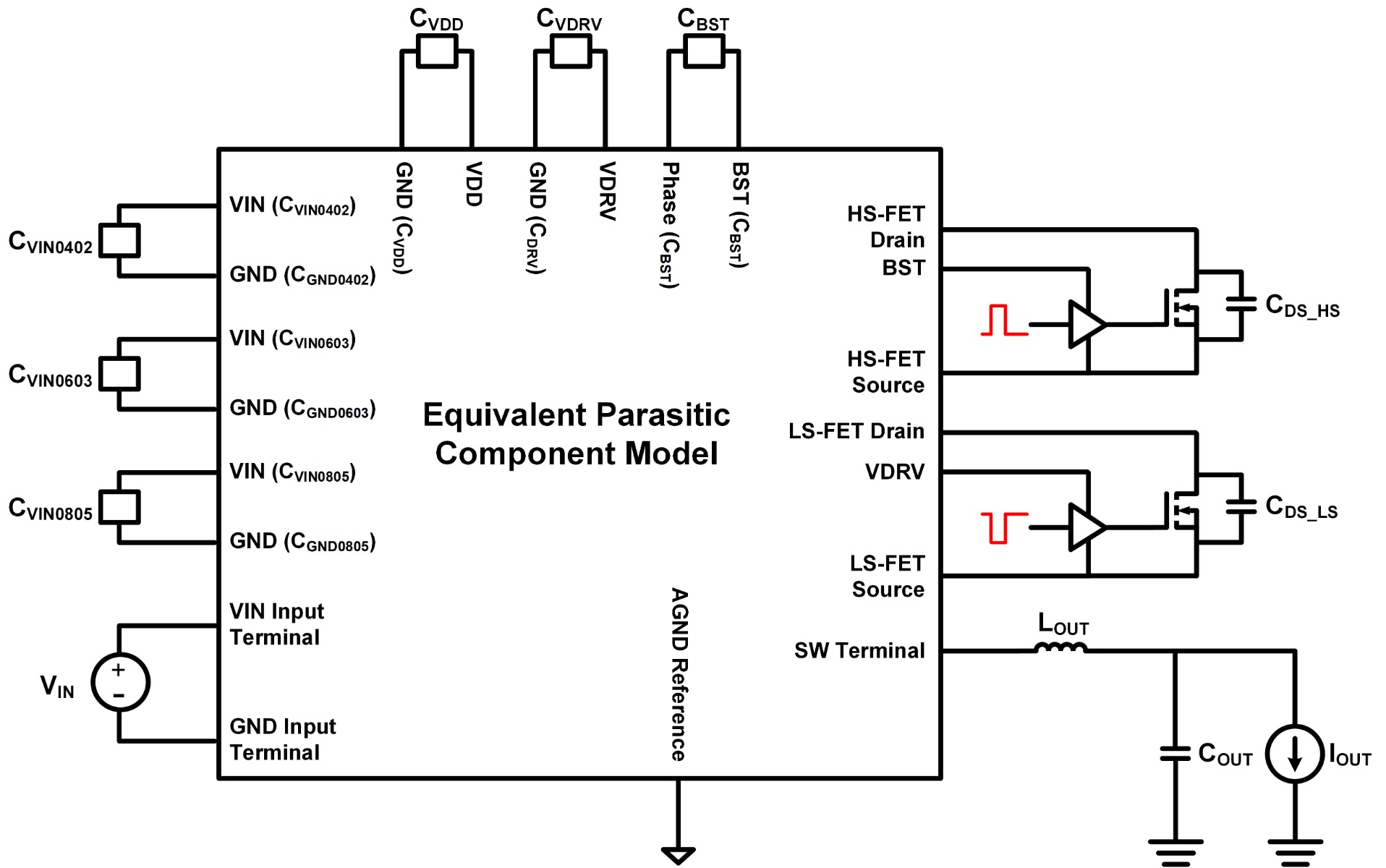

SPICEでの動作モデルシミュレーション

等価寄生部品モデルがQ3Dからエクスポートされた後、基板上のさまざまなタイプのデカップリングコンデンサの影響が考慮されます。積層セラミックコンデンサ (MLCC) にDC電圧を印加すると静電容量が低下するため、特定のDC電圧バイアス条件下で個々のMLCCの等価回路を考慮することが重要です。各考慮事項は、MLCCの動作電圧に基づいて行う必要があります。図3にSPICE上で動作モデルをシミュレーションするための回路構成を示します。

図3: 動作モデルシミュレーションの回路構成

表1に、図3の回路図に基づくシミュレーションと測定条件を示します。

表1: シミュレーションスキームと実験用テストベンチの仕様

| パラメータ | 値 |

| 入力電圧 (VIN) | 12V |

| 出力電圧 (VOUT) | 1.8V |

| スイッチング周波数 (fSW) | 800kHz |

| 出力インダクタ | 100nH |

| 負荷 | 50A |

| VDRV / VDD電圧 | 3.3V |

MP87000-Lを使用したDrMOSソリューション

MP87000-Lは、サーバーコアおよびグラフィックカード コアレギュレータ アプリケーション向けのパワーMOSFETとゲートドライバを内蔵した90Aモノリシック ハーフブリッジです。電圧のリンギングを抑えるために、MP87000-LにはQuiet SwitcherTMが搭載されています。これは、モノリシックなアーキテクチャでのみ実現可能なテクノロジーです。このテクノロジーにより、デバイスの信頼性が向上し、EMIが低減され、基板レイアウトに対する影響が軽減されます。

MP87000-Lは、高効率と高電力密度が必要なサーバーアプリケーションに最適で、TLGA-41 (5mm x 6mm) パッケージで提供されます。

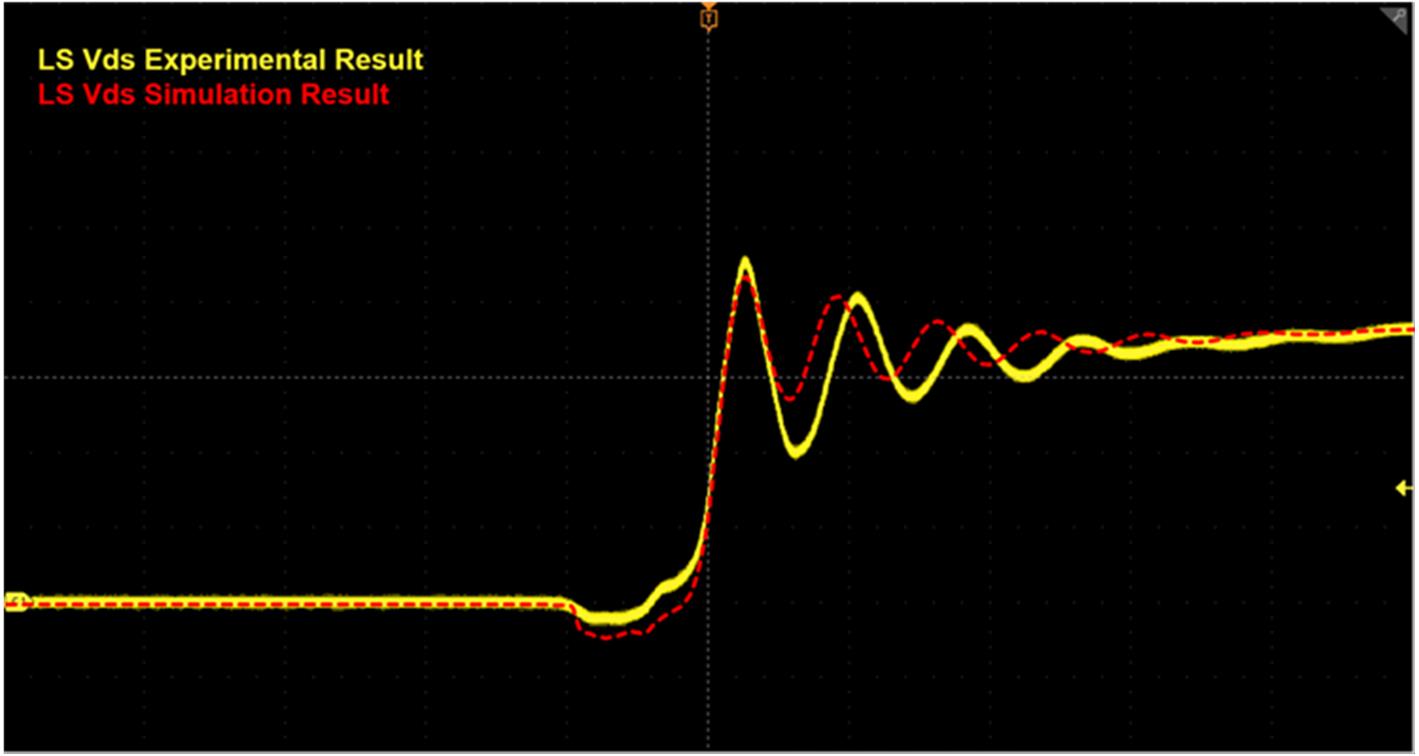

図4は、MP87000-L を使用した、LS-FETのVDSのシミュレーションと実験結果を示しています。

図4: VDS (LS-FET)のシミュレーションと実験結果

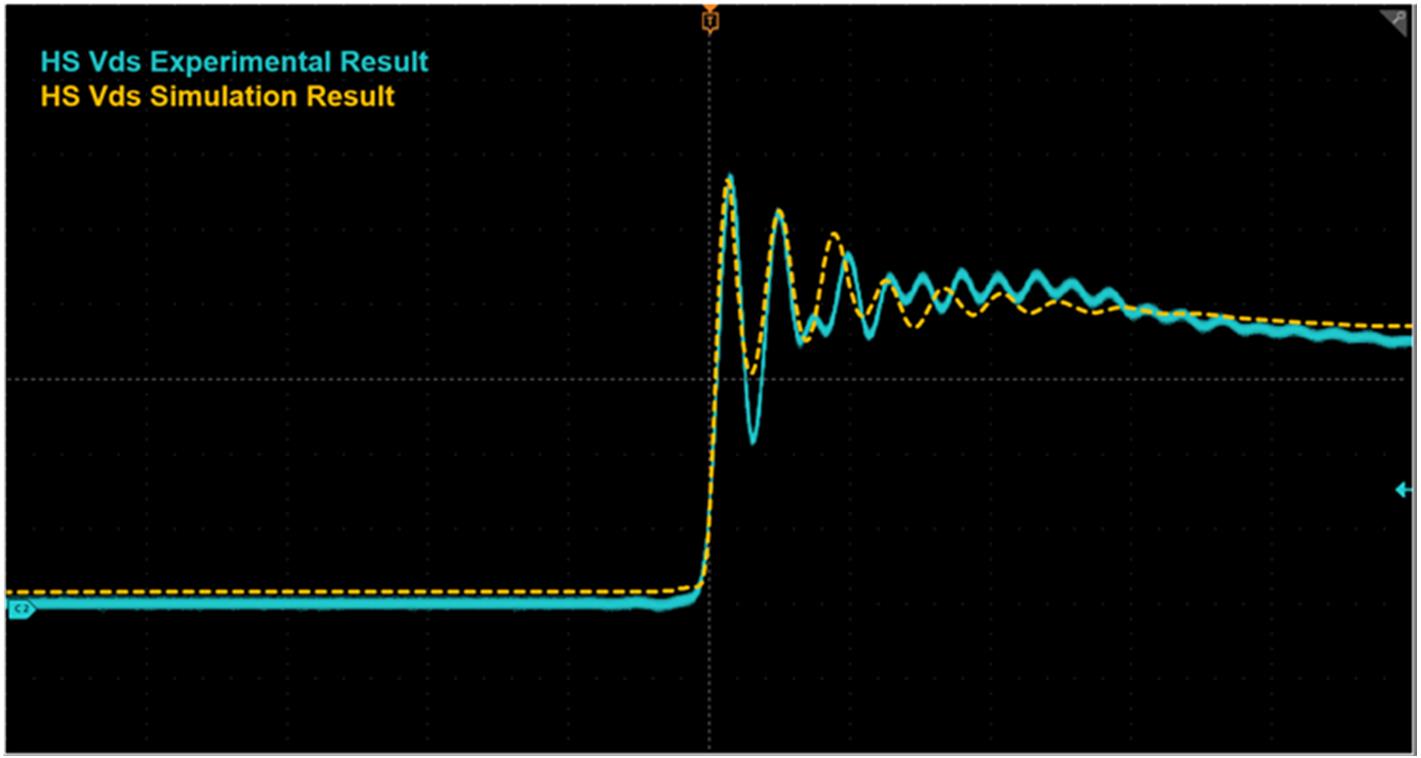

図5は、MP87000-Lを使用した、HS-FETのVDS

図5: VDS? (HS-FET) のシミュレーションと実験結果

図4と図5から、シミュレーション結果のVDSスパイクは実験結果とほぼ同じです。表2は、さまざまな負荷条件下での追加シミュレーションと実験の結果を示しています。

表2: さまざまな負荷条件下でのシミュレーションと実験結果

| 負荷 | シミュレートされたHS-FET VDSスパイク | 測定されたHS-FET VDSスパイク | シミュレートされたLS-FET VDSスパイク | 測定されたLS-FET VDSスパイク |

| 30A | 14.4V | 15.8V | 12.4V | 13.9V |

| 40A | 14.6V | 15.4V | 12.5V | 13.5V |

| 50A | 17.1V | 16.5V | 13.4V | 13.3V |

| 60A | 19.1V | 19.2V | 12.9V | 13.1V |

| 70A | 21.4V | 21.8V | 13.5V | 13V |

表2は、シミュレートされたVDSが測定結果と一致しています。つまり、動作モデルシミュレーションからのVDSスパイク予測は、寄生インダクタンスを低減できるいくつかの最適化アプローチを実行することにより、MOSFETの潜在的なアバランシェ降伏を予測できます。

寄生インダクタンスの最適化

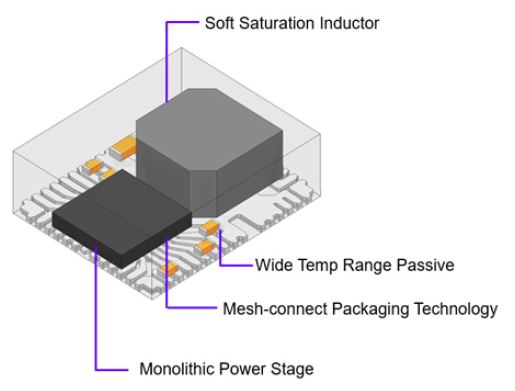

効率を損なうことなくVDSスパイクを抑えるには、基板とパッケージの寄生インダクタンスを最適化することが重要です。高度なパッケージ技術を使用すると、入力コンデンサをパッケージに統合してデカップリング経路を短縮できます (図6参照)。パッケージ内の埋め込みコンデンサを並列接続すると、DrMOS上の等価寄生インダクタンスを効果的に低減できます。

図6: コンデンサを埋め込んだDrMOS構造

表3に、MP87000-Lで異なるデカップリングコンデンサ構成を使用する場合の等価寄生インダクタンスとVDSスパイクを示します。

表3: 異なるコンデンサ構成の等価寄生インダクタンスとVDSスパイク

| コンデンサ構成 | 等価寄生インダクタンス | シミュレートされたHS-FET VDSスパイク (負荷=50A) | シミュレートされたLS-FET VDSスパイク (負荷=50A) |

| 3つの埋め込みコンデンサ、 2つのPCB 0402コンデンサ、 3つのPCB 0805コンデンサ |

157pH | 17.1V | 13.4V |

| 2つの埋め込みコンデンサ、 2つのPCB 0402コンデンサ、 3つのPCB 0805コンデンサ |

180pH | 18.2V | 14.3V |

| 1つの埋め込みコンデンサ、 2つのPCB 0402コンデンサ、 3つのPCB 0805コンデンサ |

206pH | 21.5V | 16.9V |

| 2つのPCB 0402コンデンサ、 3つのPCB 0805コンデンサ |

285pH | 27.7V | 20.6V |

表3のシミュレーション結果から、等価寄生インダクタンスが低下するだけでなく、MOSFETのVDSスパイクも抑制されます。さらに、MLCCの低ESR特性のおかげで、埋め込み入力コンデンサで追加の電力損失が発生することはありません。したがって、DrMOSアプリケーションの寄生インダクタンスを低減するために、さまざまな埋め込み入力コンデンサを追加することが可能です。

結論

本稿では、VDSスイッチングスパイクに対する寄生インダクタンスの影響、およびVDSスイッチングスパイクによるMOSFETのアバランシェ降伏を防ぐいくつかの方法について説明しました。

VDSに対する寄生インダクタンスの影響を定量化するために?本稿では、スイッチングスパイク、寄生インダクタンスのモデリングを初めて紹介し、SPICEでの動作モデリングが提案されています。SPICEによって得られた結果は、MP87000-LなどのDrMOSソリューション用の実験結果とほぼ一致しました。これは、動作モデルがMOSFETのアバランシェ降伏のリスクを正確に予測できることを意味します。

トレードオフなしにVDSスパイクを効果的に抑制するために、パッケージ内に埋め込みコンデンサが導入されました。動作モデルのシミュレーションは、これらのコンデンサが等価寄生インダクタンスを低減でき、それにより追加損失なしでVDSスパイクが低くなることが確認されました。MPSは、?データセンターソリューションを完成させるための48Vモジュール、ステップダウンコンバータ、そしてプロセッサコア電源コントローラの豊富なポートフォリオを提供します。

_______________________

興味のある内容でしたか? お役に立つ情報をメールでお届けします。今すぐ登録を!!

アカウントにログイン

新しいアカウントを作成