アナログ回路の設計再利用は神話か?

役立つ情報を毎月お届けします

プライバシーを尊重します

私は電子設計自動化 (EDA) についてコメントするよう求められました。私がイノベーションにあまり貢献していない産業界のテーマですが、アナログ設計者としての長いキャリアの中で恩恵を受けてきた者として、一言だけ言えることがあります。

DC/DCパワーコンバータやカスタムおよびスタンダードアナログIC製品の設計に25年以上の経験を持つ私は、長年にわたってEDAツールセットに革命的な変化を見てきました。さまざまな企業に勤め、現在はMPSに所属しているので、設計手法の多様なアプローチを見てきたことは確かです。

私の考えでは、EDAの継続的な発展の背後にある推進力は、結果として得られるシリコンで成功するという信頼性に加えて、設計実行速度が絶えず向上していることです。シミュレーションエンジン、データの可視化、寄生要素のレイアウト後の抽出などの改善が行われているにもかかわらず、常に新たなアップグレードが行われているようです。「すべてはデジタル化されているが、世界はまだアナログだ」という昔のことわざが頭に浮かびます。ここでのアナログはエンジニアのことで、EDAの継続的な発展を推進しているのは、この人間的な要素なのかもしれません。

私の仕事の人生を支配するテーマは回路の再利用です。MPSに入社する前の面接でも話題になりました。アナログデザインコミュニティの人々がIPブロックを再利用するのがなぜ難しいのでしょうか?」と聞かれました。不意を突かれ、私は再利用の障壁を説明する準備ができていませんでした。私はまた、IP追跡のための会社の内部システムについて何も知らなかったので、面接官に決定的な答えを提供することができませんでした。MPSで設計プロセスやレガシー回路について学びながら、この疑問を投げかけ続けてきました。

経験豊富な設計技術者なら誰でも好きなバンドギャップを持っていると答えるのは簡単です。MOSFETの使用を好む人もいれば、バイポーラを使用する人もいます。しかし、私は答えがより根本的であると結論付けました。そしてこれらの絶え間ない葛藤はいくつかの点に要約できます。機能の貧弱な理解につながる不十分なドキュメンテーション、および理想的な規律ではない設計階層です。「やれやれ…」ソフトウェア工学にありそうな状況のように聞こえますね。

とはいえ、EDAは設計ブロックの適切な再利用を容易にするアナログの助けとなるでしょうか? また、エンジニアがプロジェクトでやり取りする方法を改善し、設計をより迅速に完了できるようにすることができるでしょうか? できるかもしれませんが、これはまだ進行中の作業です。再利用に役立ったEDAツールの6つの側面について説明したいと思います。

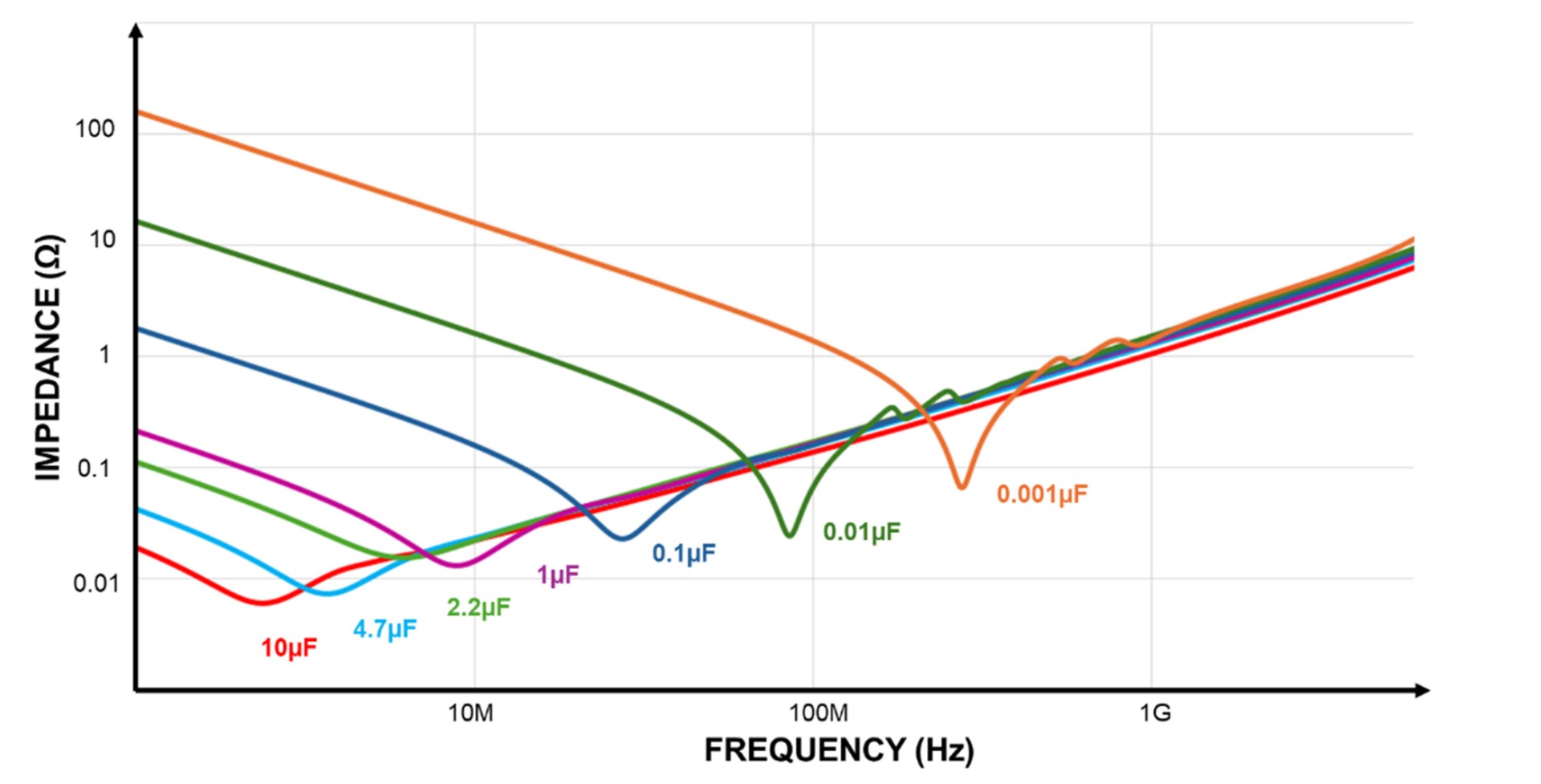

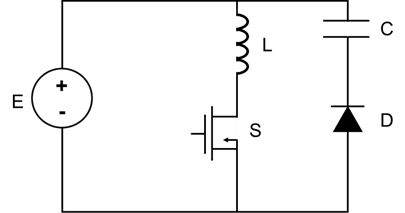

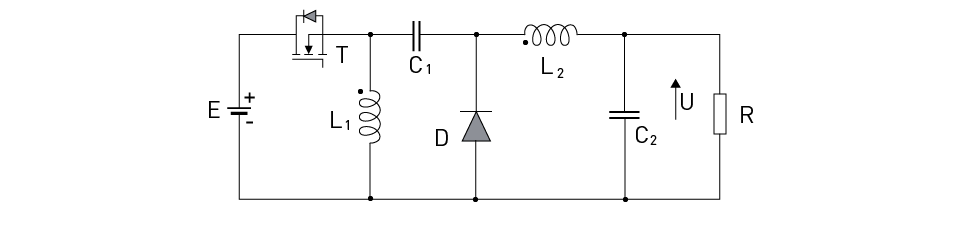

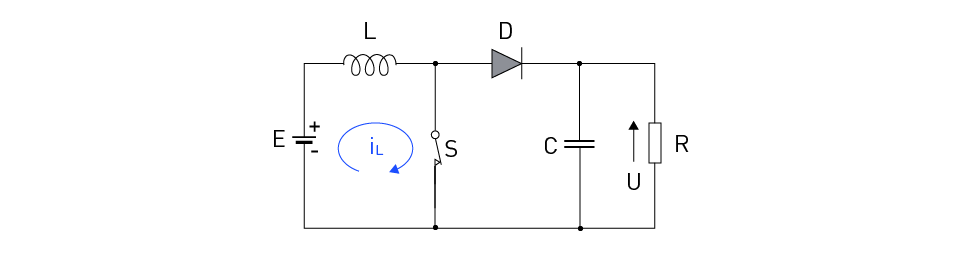

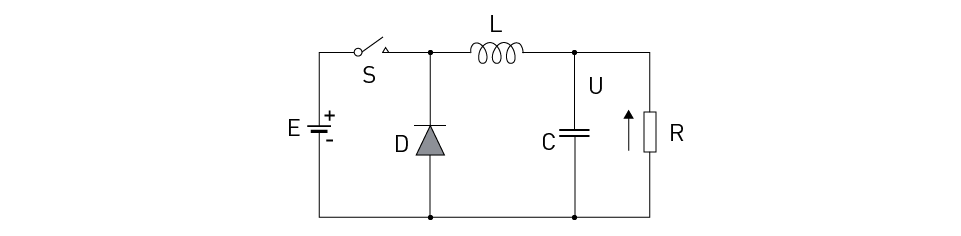

- システム内のマクロモデリングブロックは、理解とチームコミュニケーションを容易にします。以前にLTSpice™を使用したことがあり、現在の仕事では、私が設計するスイッチモードのコンバータの定期的なシステム安定性解析を提供するSimplis™を使用しています。得られたマクロモデルの回路図は理解するのに十分単純であり、概念実証シミュレーションを実行することができます。これらのモデルは、回路設計選択の指針とするために、チームメンバーと共有することができます。リリース後は、既製のシミュレーションツールを使用してICモデルを顧客に送信し、より高いレベルの性能をシミュレートすることができます。これは、このタイプのEDAツールを使用したウィン・ウィン・ウィンの状況です。

- 回路図にメモを直接追加したり、各ブロックのプレゼンテーションを追加したりするなど、すぐれた回路図ドキュメントは透明性を生み出し、レビューを迅速にして再利用を促進します。例えば、ほとんどのシミュレータは回路のDC動作点を効果的に提示できますが、この情報は設計技術者が結果を解釈した場合、運転ヘッドルーム、コモンモード入出力範囲、利得 / 位相マージンなどに影響を与えるため、さらに有用です。

- 階層的な規律は明確さを維持するために不可欠です。ブランキングを伴うコンパレータのような単一の関数を複数の階層レベルで区切られたブロックに分散させる悪い例を見たことがあります。階層を適切に使用することで、回路図の外観をシンプルにして理解を深めることができ、レイアウトや機能的なサブブロックとそのレイアウトの再利用を容易にすることができます。エンジニアは、内部の働きや外部ブロックとのタイミングの相互作用が「複雑で面倒」と認識される場合、何かを再利用しない傾向があります。

- 技術間のシンボルとデバイスモデリングの互換性は、移行と再利用を容易にします。デバイスピンの位置が変わったときに回路図を再作成するのは非常に面倒で、この作業はスケジューリングの観点からは新たなスタートと考えられます。新たなスタートは、単純化のために回路内のニュアンスが廃棄される可能性が高いことを意味します。エンジニアは回路図を再作成するときに個人のIPを失うことを認識しているので、私が知っている多くのエンジニアは、数年間… または可能であれば、彼らのキャリアのために1つテクノロジーにとどまることを望みます。しかし、これは不可能なため、エンジニアは、モデリングパラメータを変更しなければならない場合でも、回路要素の形状、適合性、機能を維持することで、技術間で設計を再利用するための迅速な作業を行う必要があります。

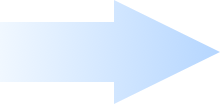

- 長年の経験を持つ同僚は、署名ブロックに「レイアウトは回路である」と書いています。寄生レイアウトデバイスは基板を含む全ての階層を悩ませるため、設計を成功させるにはモデル化する必要があります。基板レベルでは、寄生要素は通常、スイッチ電流に直列のインダクタンスです。ICレベルでは、通常、ノイズの多い信号を敏感な信号に結合したり、高速信号 (デジタルまたはアナログ) を遅くしたりするコンデンサです。レイアウト後に抽出されたシミュレーションは非常に重要なステップです。ヒントは、デバッグを容易にするために回路図にネット命名規則を使用することです。つまり、階層の複数のレベルで伝播されたときに競合しない信号名を慎重に選択することです。

- メタデータを保存できる要件追跡ソフトウェアは、部門間でコラボレーションするためのフレームワークを作成し、製品リリース後は外部監査を行います。これまでにJAMA ConnectやGitlabなどのプログラムを使用しました。この最後のEDAツールは、他のEDAツールの出力を合成する際に重要な役割を果たすことができます。

EDAツールに関するこの簡単な解説が役に立ち、議論に火が付くことを願います。要約すると、エンジニアは設計時に多くの選択肢を提示されます。十分に文書化され、よくモデル化され、透明化された設計と、これらの属性で「才能」を持たない設計の間で選択する場合、エンジニアが理解可能な設計のセキュリティを選択するでしょう。そうでなければ、意図的に透明なドナーが見つからない場合、設計を完全にやり直すかもしれません。これがアナログ回路の再利用についての私の長年の答えです。

_______________________

興味のある内容でしたか? お役に立つ情報をメールでお届けします。今すぐ登録を!

アカウントにログイン

新しいアカウントを作成