PoE (パワーオーバーイーサネット) PD設計を最適化する方法

役立つ情報を毎月お届けします

プライバシーを尊重します

PoE (パワーオーバーイーサネット) とは?

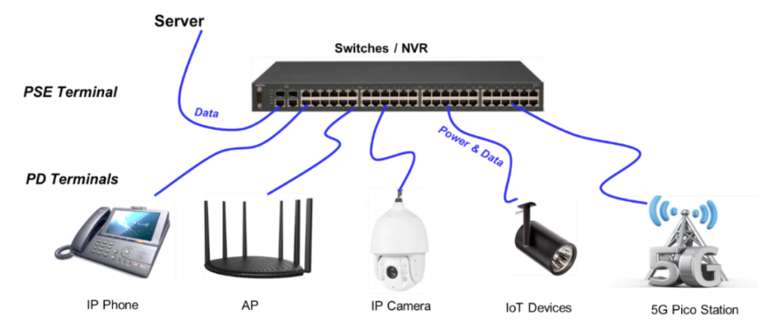

PoE (パワーオーバーイーサネット) ソリューションにより、イーサネットケーブルはDC電力を伝送しながら、イーサネット規格によって設定された、既存のワイヤ接続を変更せずに、すべてのIP端末デバイスに並列で同時にデータを伝送できます。電力とデータを1本のケーブルで送信することにより、導入が簡略化され、信頼性が向上し、電力とイーサネットラインが不要になることでコストが削減されます。これにより、PoEデバイスは、機器室やオフィス、新しい送電線の設置に不便な古い建物で人気のある選択肢です。

本稿では、PoE・PD設計の概要とこれらのシステムを実装する設計者が直面する課題について説明し、MP8017を使ったPoE・PD設計を最適化する方法について推奨事項を検証します。MP8017は、統合されたPoE PDおよびフライバック電源コンバータです。

PoEの進化

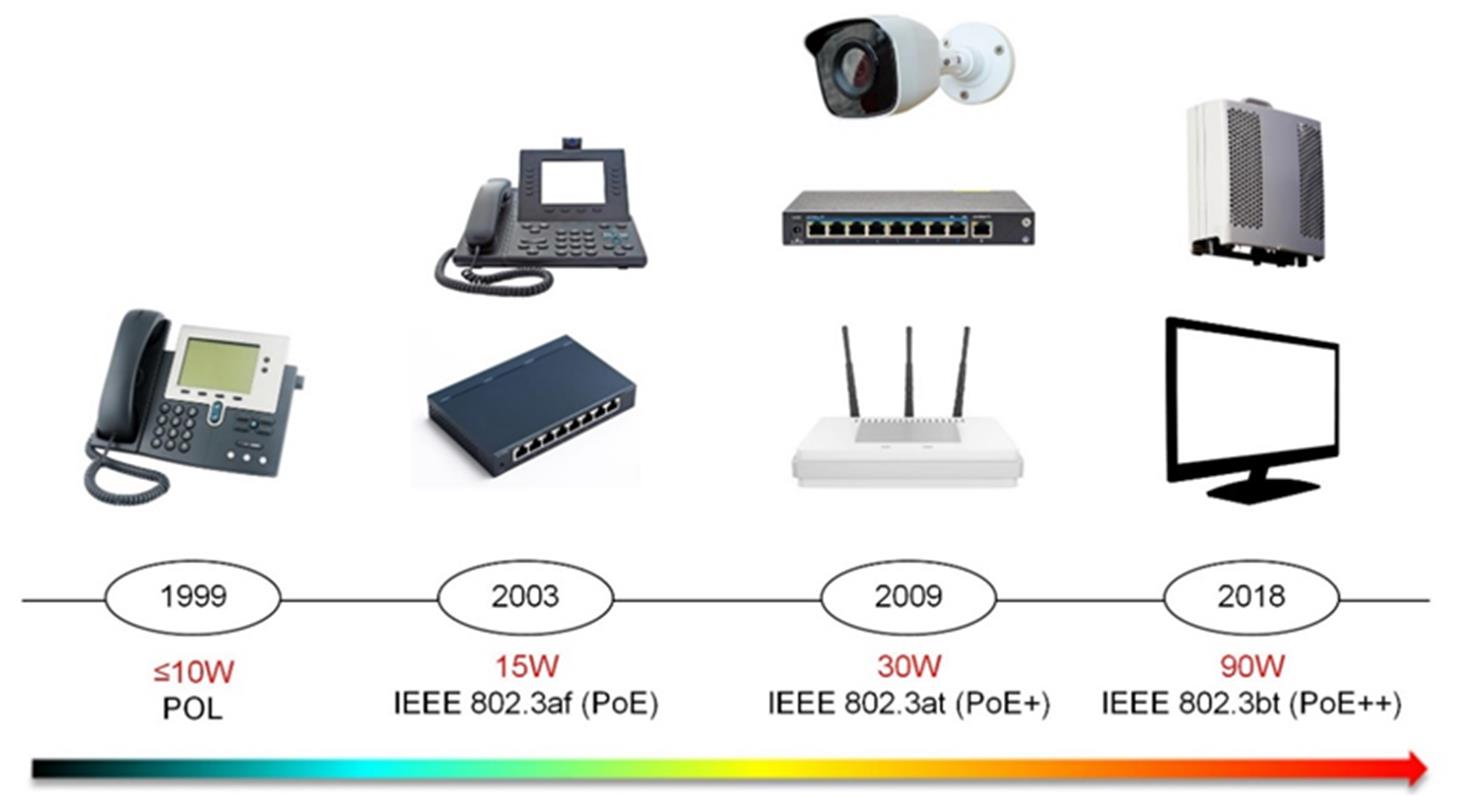

1999年、IEEEとイーサネット・アライアンスは、接続された受電デバイス (PD) と給電機器 (PSE) の幅広い範囲にわたって相互運用性を確保することを目標に、PoEの標準化に努めました。これらの標準の最初のものであるIEEE 802.3afは、2003年に批准されました。この規格は、1本のケーブル内でスペアペアまたはデータペアのいずれかによって電力を伝送できる必要があることを規定しました。現在のPoE規格はIEEE802.3bt (90W) で、5Gスモールセル、ディスプレイ・ユニット、APルータなどの追加アプリケーションをカバーしています。図1は、1999年の≤10W規格から始まったIEEE PoE規格のタイムラインを示しています。

図1 : PoE規格の進化の歴史

PoE電力分類

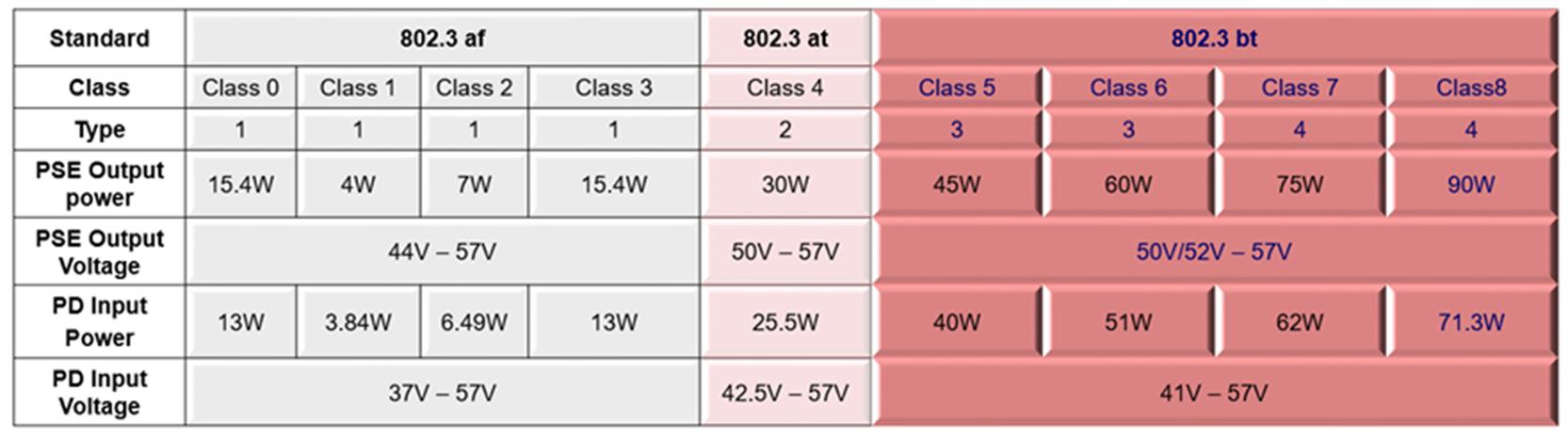

PoEデバイスには、必要な電力に基づいてクラス (クラス0~8、合計9つのクラス) が割り当てられます。802.3af規格は、クラス0からクラス3をカバーし、電圧範囲は37V〜57Vで、出力電力は最大15.4Vです。これらのデバイスは、センサや単純なカメラに推奨されます。

802.3at規格 (PoE+とも呼ばれる) はクラス4を導入し、同じ電圧範囲で出力電力を30Wに上げますが、これらのデバイスは PoE+ PSEとのみ互換性があり、複雑なカメラ、LCDディスプレイ、およびタブレットで使用できます。

最後に、802.3bt規格 (PoE++とも呼ばれます) は、クラス5からクラス8までを導入し、出力電力は45W〜90Wの間です。これらのデバイスは、ラップトップ、テレビ、および建物内の電気システムをサポートできます。図2は、これらの電力クラスと、関連する入力電圧、入力電力、および出力電圧をまとめたものです。

図2 : PoE電力分類

関連コンテンツ

-

ビデオ

PoE (パワーオーバーイーサネット) およびPoEコントローラとコンバータについて理解する

PoE (パワーオーバーイーサネット) が設計でどのような意味を持つかを探る

-

寄稿文

MP8017の紹介 : 超小型IEEE802.3af PoE PDソリューション

MPSの電源デバイス (PD) ソリューションの詳細をご覧ください

-

寄稿文

PoE (パワーオーバーイーサネット) ソリューションの設計

PoEの一般的な要件と、PDのDC/DC変換の設計を知る

-

カテゴリーページ

PoE (パワーオーバーイーサネット)

MPSのPoE ICは、簡単な設計、シンプルなBOM、および高効率を可能にします

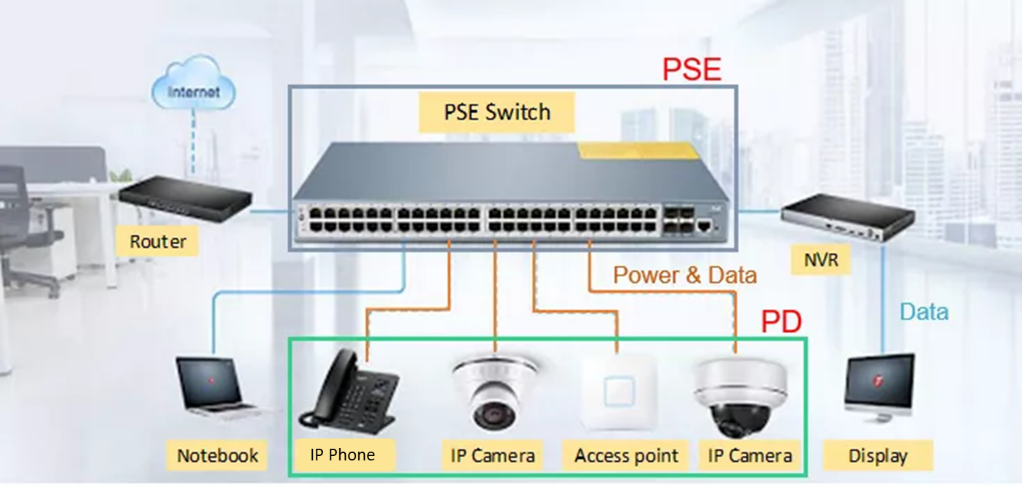

PoEの動作原理

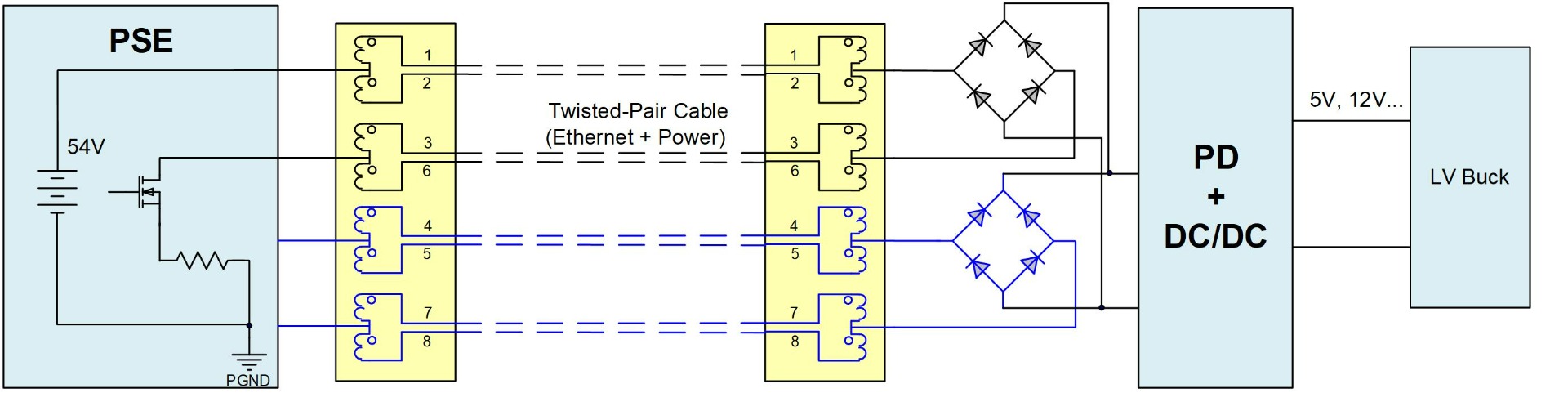

ネットワークケーブルは、情報を送信できるデータペアと、スペアペアと呼ばれる未使用のペアを用いた、ペアでよりあわされたワイヤで構成されます。PDとPSEが正常に通信することをハンドシェイクと呼びます。PSEがPDとハンドシェイクするときは、以下に示す主な手順に従います。

- PDチェック : PSEはテスト電圧 (<10.1V) をPD抵抗 (24.9kΩ) に送ります。インピーダンス値が一致する場合、これは標準PoEデバイスの存在を示します。

- 電力分類 : PSEはある電圧を送り、電流フィードバックを取得してPDの電力レベル (クラス1~クラス8) を確認します。

- 供給電力 : PSEの入力電力は約54Vまで上昇します。

- 電源を安定させてモニタする : 電力は約54Vで安定し、分類結果に基づいて最大電力が制限されます。

- 切断 : PDが切断されると、PSEは電力の供給を停止します

図3は、全体的な通信構造を示しています。

図3 : PSEおよびPD通信ハードウェア構造

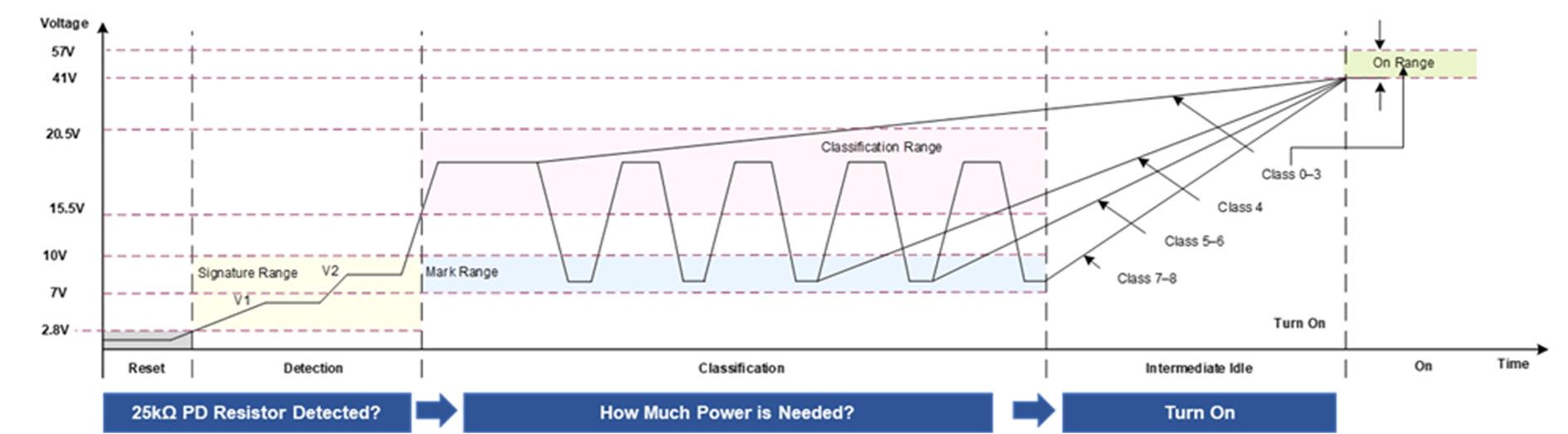

図4は、PSEとPDの間でハンドシェイクが起こっているときに電圧レベルがどのように変化するかを示しています。

図4 : ハンドシェイク中の入力電圧の変化

PoEソリューションを設計する際の課題

PoEデバイスはいくつかの課題に直面しています。最初の課題は効率です。PoEデバイスには電力とデータ転送の両方が組み込まれていますが、正しく設計されていないと効率が低下する可能性があります。特に、設計者は電源回路を最適化して部品のインピーダンスを減らし、最適なトランスを選択して効率を向上する必要があります。

さらに、大量の電力伝送によって可聴ノイズが発生し、デバイスが最新のEMI規格を満たす能力に影響を与える可能性があります。調整されていない場合、EMIは周囲のデバイスを劣化させ、システムの寿命を縮める可能性があります。より多くの電力を供給するPoEデバイスは物理的により大きいため、スペースに制約のあるアプリケーションでは必須の空間を占有してしまう可能性があります。

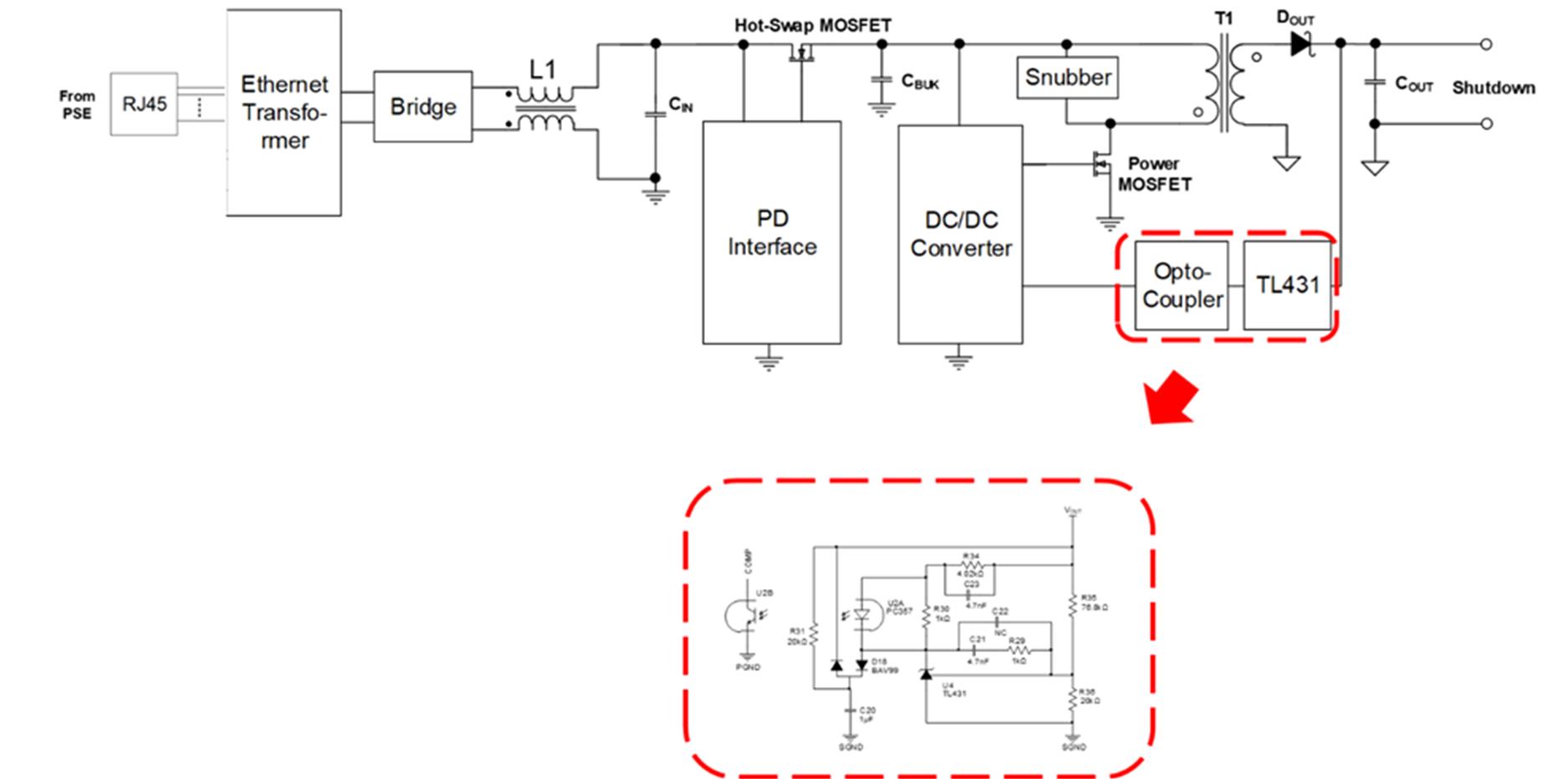

図5に、代表的な15WのPoE PD電源回路を示します。必要な部品の数が多いため、この回路は複雑でかさばります。フォトカプラとTL431電圧レギュレータだけでも、多数の部品からなる独自の回路システムを構成しています。

図5 : フォトカプラのフィードバックを備えた従来の15W PD電源回路

PoEソリューションの最適化

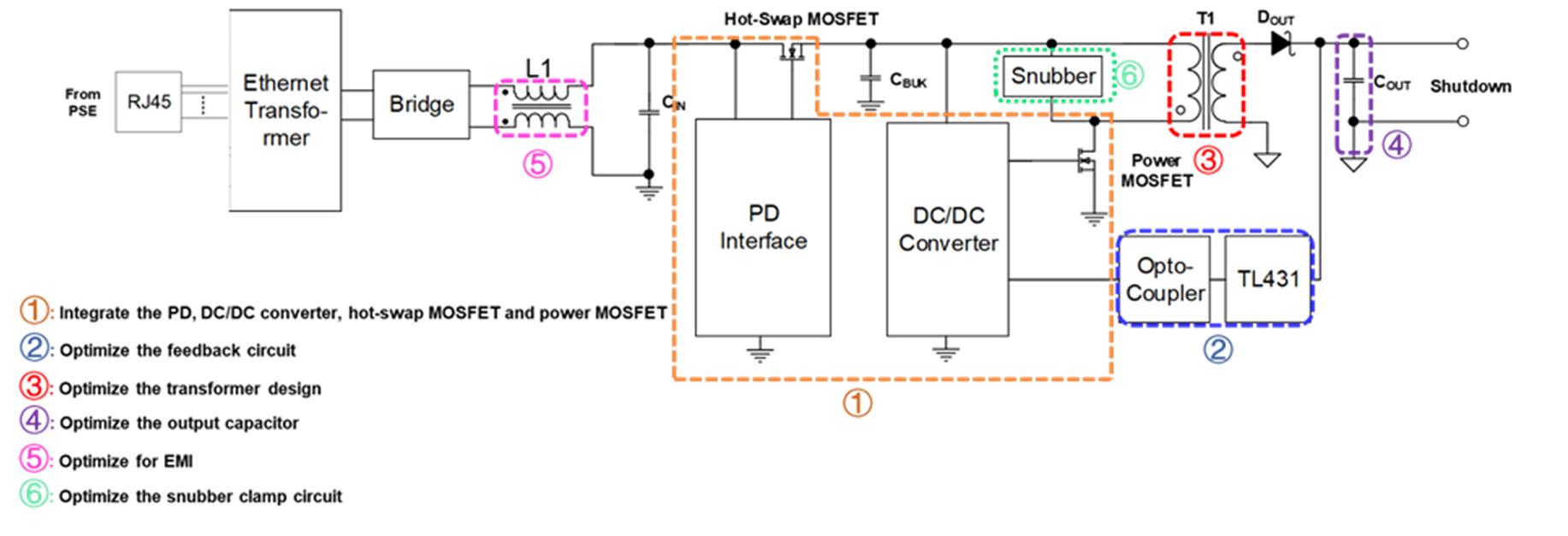

この回路を最適化するには、6つの簡単な方法があります (図6参照)。

図6 : PoE PD設計の最適化

これらの方法について、以下で詳しく説明します。

- 完全統合: PoEデバイスの場合、完全に統合されたソリューションは、ソリューションをコンパクトに保つ優れた方法です。PoEソリューションに関するよくある質問には、「このシステムにPDとDC/DCコンバータを含めることはできますか?」、「ソリューションにホットスワップMOSFETとパワーMOSFETを含めることはできますか?」などがあります。

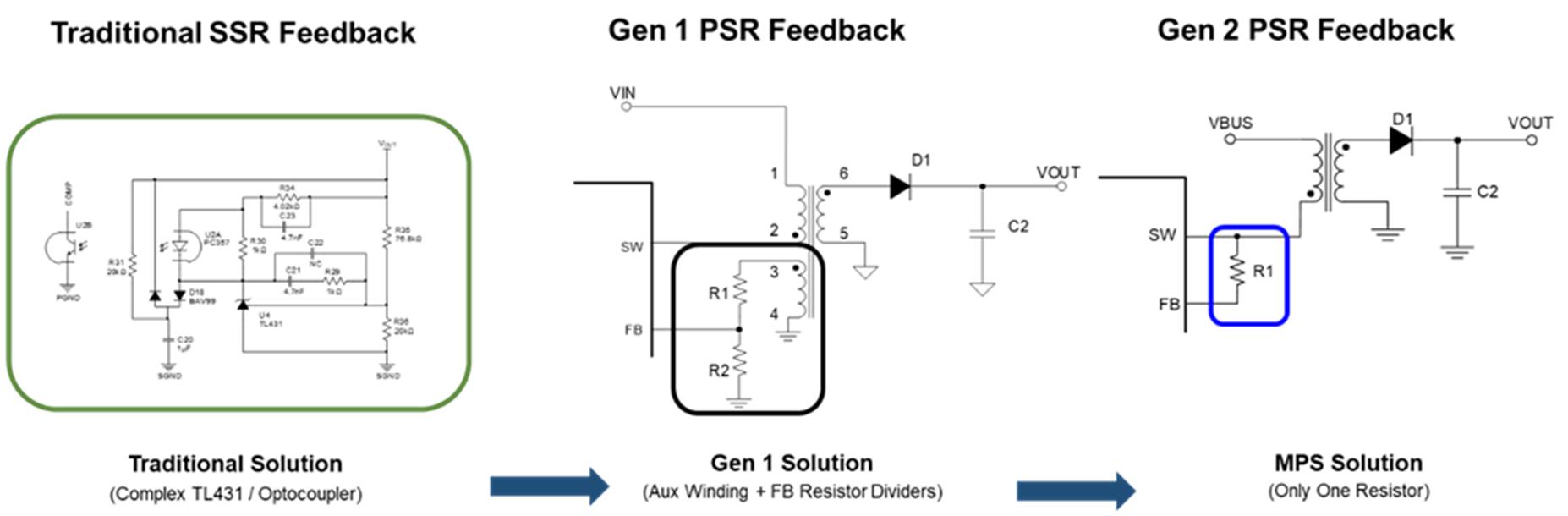

両方の質問に対する答えはイエスです。PD、コンバータ、MOSFETを統合することで、設計者はPCBサイズと設計サイクルを大幅に削減できます。統合されたソリューションは、簡素化されたソリューションでは必要な外付け部品が少なくて済むため、BOM費用も削減します。 - フィードバック回路 : 従来のフライバック回路では、電圧レギュレータ、フォトカプラ・フィードバックネットワーク、ループ補償、およびソフトスタート回路が必要です。図8は、従来のSSRフィードバック回路など、さまざまな回路の複雑さを示しています。フライバック技術の進化に伴い、基本的なフィードバック方式が導入されました (Gen 1 PSRフィードバック)。このタイプの回路には通常、補助巻線が含まれます。

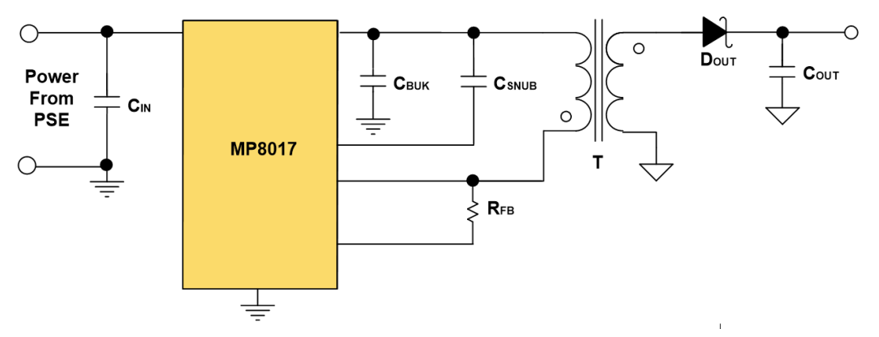

MP8017のPoE PDソリューションは、Gen 2 PSRフィードバックと呼ばれる新しいフィードバック方式を使用します。このシステムは、補助巻線やフォトカプラを必要としません (図7参照)。代わりに、デバイスはSWピンから出力電圧 (VOUT) をサンプリングします。この方法の利点は次のとおりです : - トランスが補助巻線を必要としないことによる、設計回路の簡略化

- トランスのコスト削減

- インピーダンス低減し、効率を向上する、同じコアに巻ける追加の電力巻線。

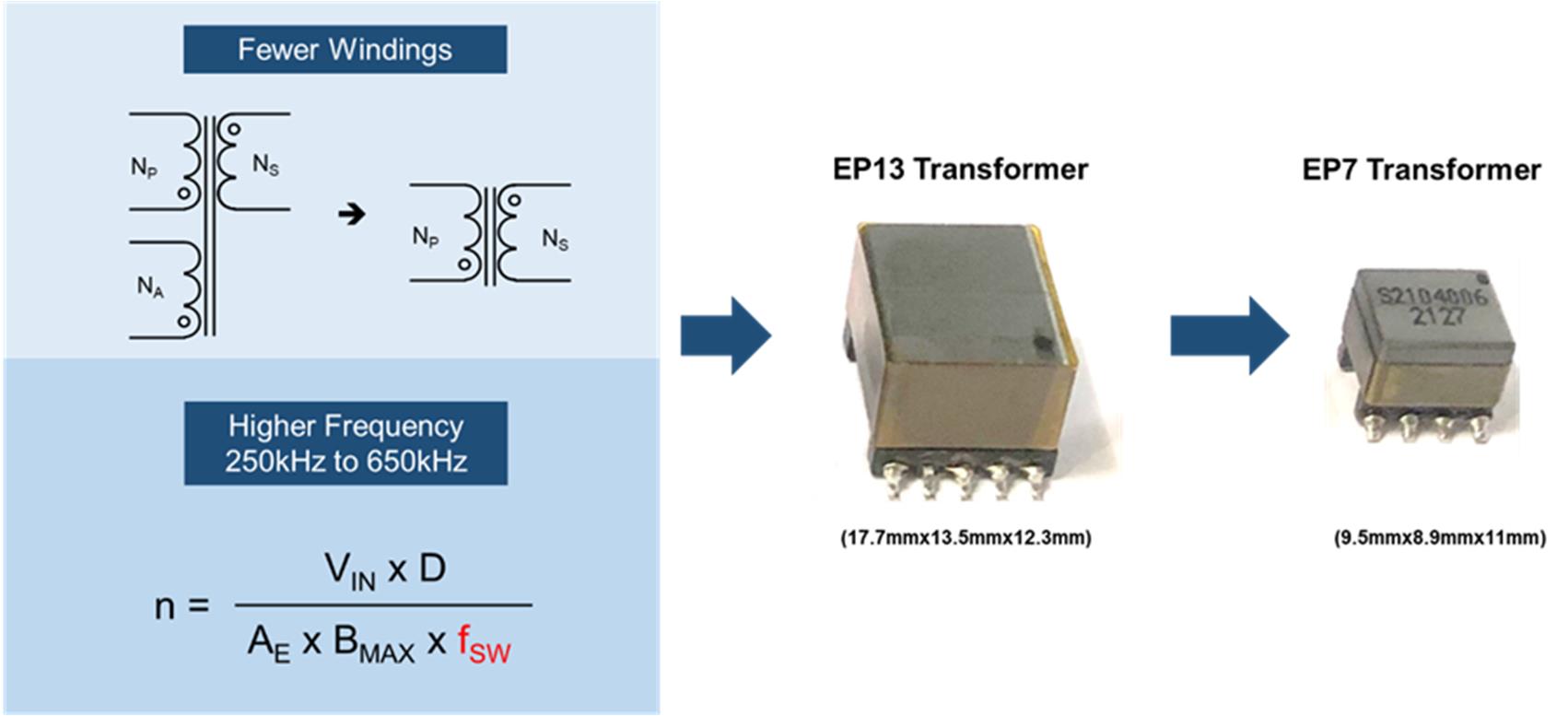

- 変圧器の設計 : ほとんどの設計では、トランスは回路内で物理的に最大かつ最も高価な部品です。従来、12WのアプリケーションにはEP13トランスが使用されていました。しかし、フィードバック回路を最適化し、補助巻線の必要性をなくすことで、設計者は高いスイッチング周波数 (fSW) を実装して、トランスの巻数を減らすことができます。これは、EP7がスペースの3分の1未満しか占有せずに、EP7トランスがEP13を置き換えることができることを意味します (図8参照)。

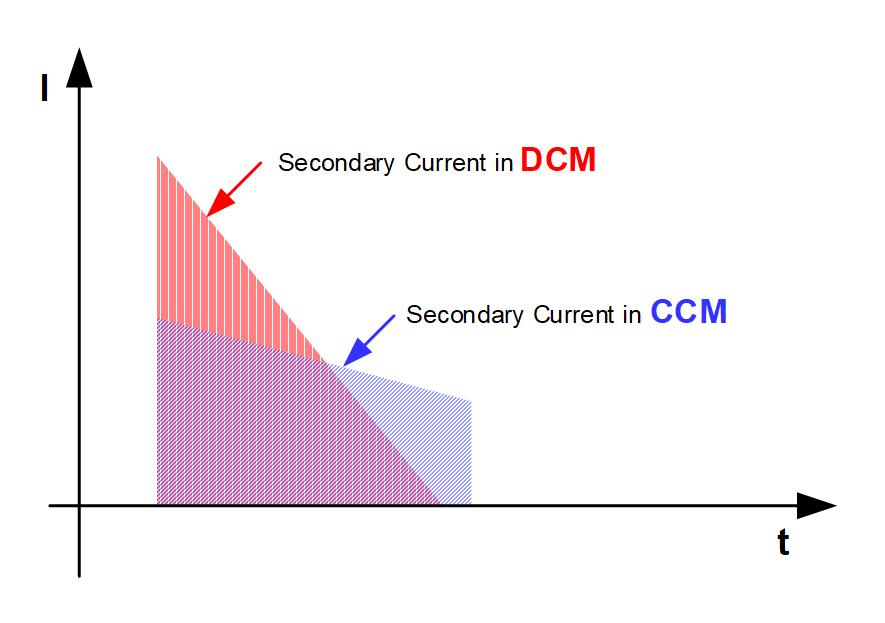

- 出力容量 : 従来のPoEデバイスの標準周波数は約250kHzで、出力リップルを減らすために電解コンデンサが必要です。もし、fSWが増えると、出力コンデンサの数を減らすことができます。たとえば、fSWが650kHzの場合、12Wのアプリケーションでは、0805サイズのセラミックコンデンサは2つしか必要ありません。また、連続導通モード (CCM) 制御を利用することで、トランスの二次側ピーク電流が小さくなります。ピーク電流が小さくなると、出力コンデンサのESRとレイアウトボードの抵抗によって生じる出力リップルがさらに減少します。図9は、CCMと不連続導通モード (DCM) の両方での二次電流を比較しています。

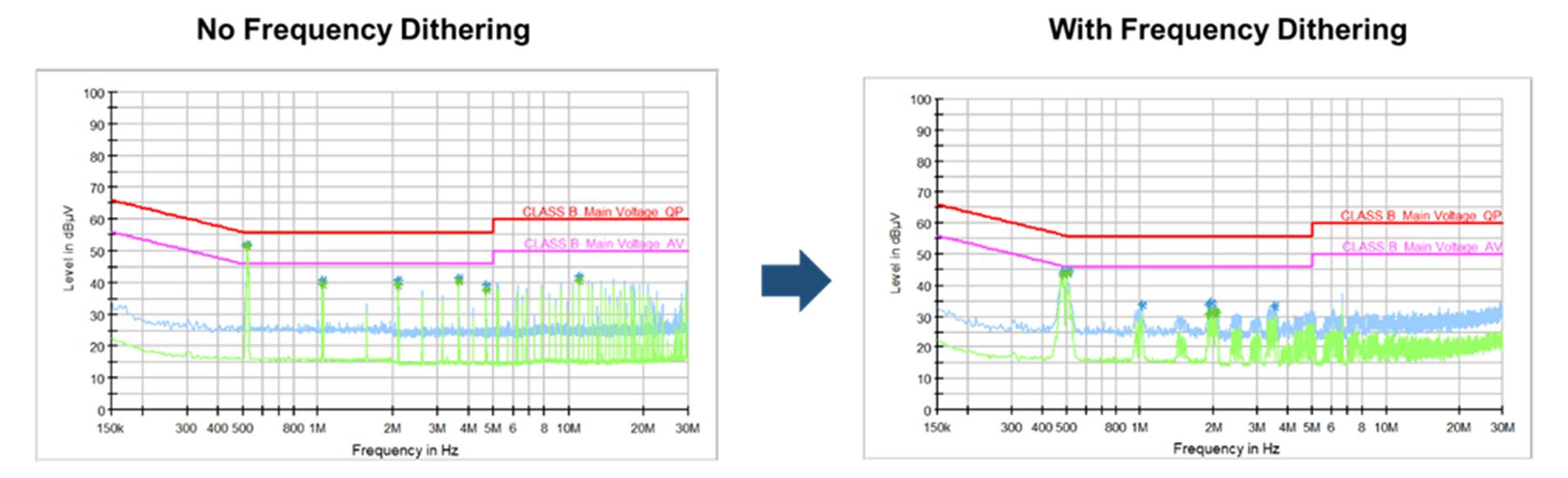

- EMI設計 : 関連するすべてのデバイスはEMC規格に合格する必要がありますが、EMI性能のためにデバイスを最適化することが困難な場合があります。フライバック・ソリューションでは通常、EMI性能を向上するためにコモンモード (CM) インダクタが必要ですが、このインダクタは高価で、重要なPCBスペースを占有する場合があります。CMインダクタを使用せずにEMIの課題に対処するには、スペクトラム拡散周波数ディザリングをサポートする方法と、よりスムーズなSW波形を作成する方法の2つがあります。スペクトラム拡散周波数ディザリングでは、fSWは公称範囲内で変動します。MP8017は、M/Dピンを使用したディザリング機能をサポートしています。その周波数ディザリングは、約9kHzの変調周波数で±6%に固定されています。図10は、周波数ディザリングを使用してノイズ・スパイクを低減する方法を示しています。

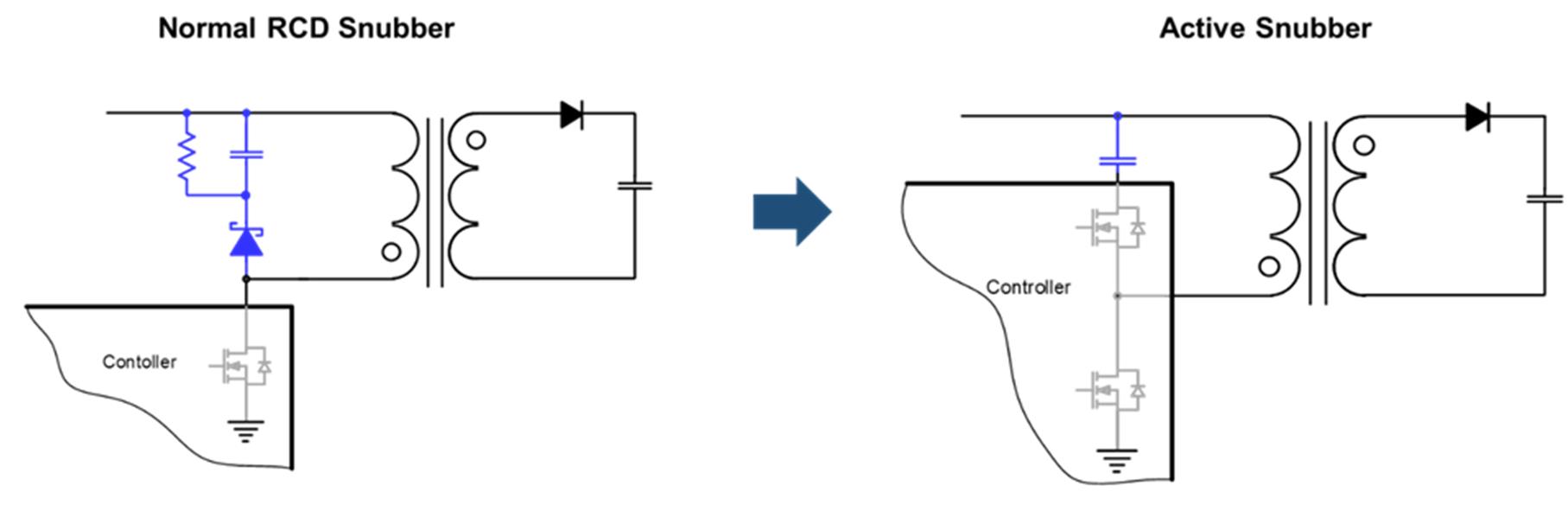

- アクティブスナバ : フライバック・アプリケーションでは、抵抗コンデンサダイオード (RCD) は通常、SWのピーク電圧を低減し、漏れインダクタンスエネルギーを吸収するためのクランプ回路として使用されます。ただし、この回路には2つの問題があります :

- SWはEMI性能に悪影響を与える共振を発生する。

- 漏れインダクタンスのエネルギーが消費されると、システム効率が低下する。

図7 : フィードバック・ソリューションの比較

この高度なフィードバック方式を使用すると、回路が簡素化され、BOMが削減されます。

図8 : EP13トランス 対 EP7トランス

図9 : DCMおよびCCMにおけるトランスの二次側電流

図10 : 周波数ディザリングなしと周波数ディザリングあり

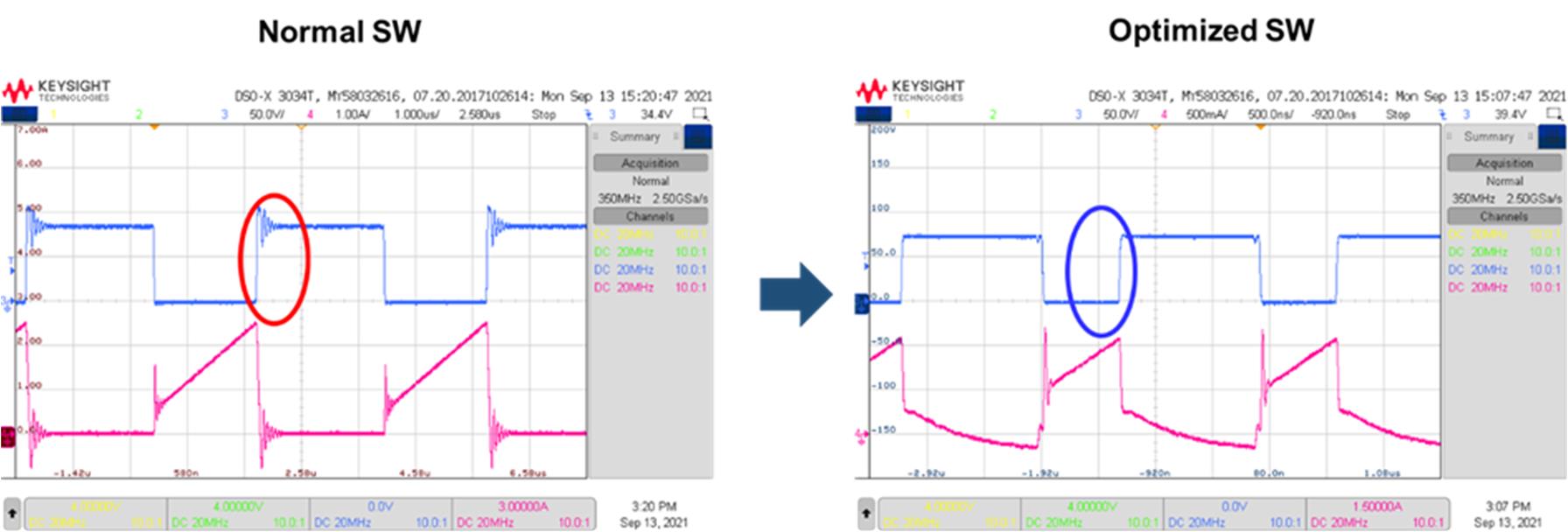

SW波形の最適化は、EMIを改善するもう1つの方法です (図11参照)。

図11 : 通常のSWと最適化されたSW

MP8017でこれらの方法を実装した後、EMI性能は大幅に向上し、EMI性能を低下させることなくCMインダクタが低減されました。

アクティブクランプ制御方式は、これらの問題を軽減できます (図12参照)。この方法では、パワーMOSFETを使用して、従来のRCDスナバに見られる抵抗とダイオードを置き換えます。これにより、MP8017などのデバイスは二次側レギュレーション (SSR) を実装でき、効率が向上します。

図12 : RCDスナバ 対 アクティブスナバ

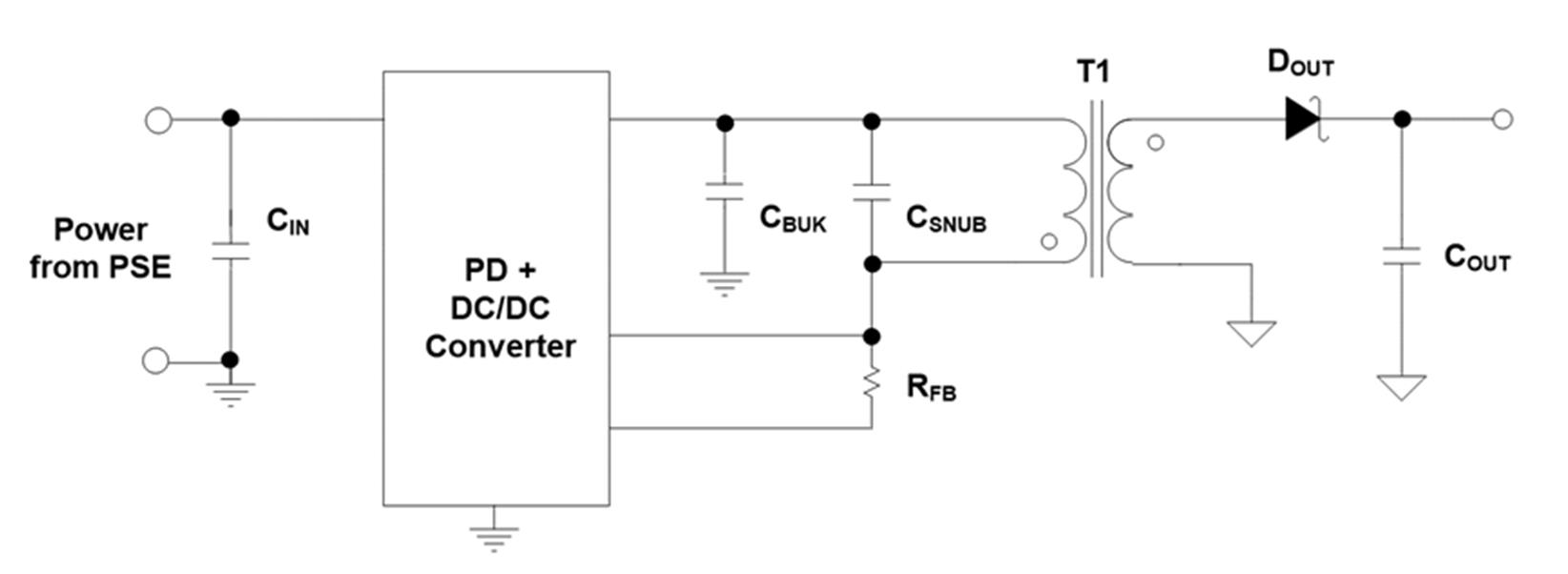

上記の6つの主な方法を実装することで、最終回路を従来の回路に比べて大幅に簡素化できます (図13参照)。

図13 : 最終回路

結論

PoEは、現代テクノロジの増大する電力需要に対応するために継続的に進化している革新的な概念です。一般的な信頼にもかかわらず、設計者がこれらのソリューションで高い効率を維持することは困難な場合がありますが、いくつかの最適化方法を実装することでこれらの問題を軽減することができます。MP8017は、最適なトランス、スナバ、および出力コンデンサを選択すること、および周波数ディザリングを実装し、単一のダイに部品を統合することが、性能を妨げることなく効率を保証する効果的な方法であることを裏付けました。

_______________________

興味のある内容でしたか? お役に立つ情報をメールでお届けします。今すぐ登録を!

アカウントにログイン

新しいアカウントを作成