AN222 - MP5048を用いた並列アプリケーションの設計

役立つ情報を毎月お届けします

プライバシーを尊重します

はじめに

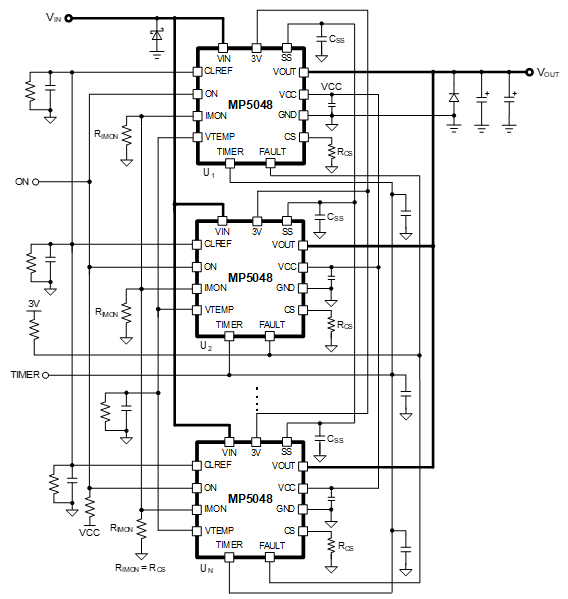

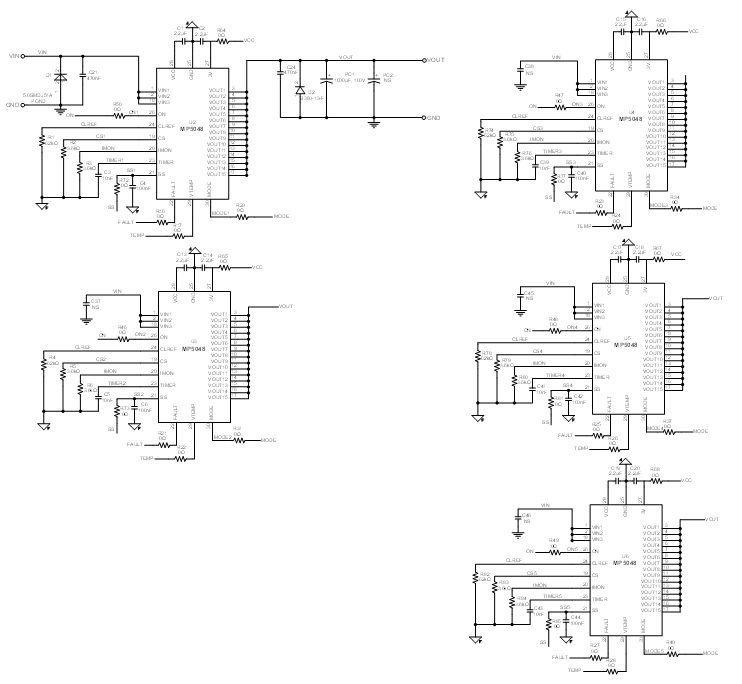

このアプリケーションノートでは、並列アプリケーション向けのMP5048の設計について説明します。MP5048は、高電流アプリケーション向けに並列接続できるモノリシックなコントローラおよびスイッチを搭載しています。当ICには、ハイサイドMOSFET (HS-FET) と、スタンドアロンデバイスとしての動作やホットスワップコントローラによる制御を可能にする回路が含まれています。これはMP5048あたり最大15Aの連続電流を駆動できます。図1は、単一MP5048デバイスの代表的なアプリケーション回路図を示しています。

図1: MP5048のスタンドアロンの代表的なアプリケーション回路図

MP5048は、アクティブなバックプレーン電源に回路カードが挿入されたときに負荷への突入電流を制限し、バックプレーンの電圧降下を制限します。また、電流制限リファレンス入力を通じて、ゲート電圧を制御することで、内部MOSFETの電流も制限します。

MP5048は、出力電流 (IOUT) とダイ温度をモニタするソリューションなど、システム設計を簡素化する多くの機能を備えています。これにより、外付けの電流検出パワー抵抗、パワーMOSFET、また熱検出が不要になります。また、パワーFETのゲートソース、およびドレインの短絡状態も検出して、コントローラ用のフィードバックを提供します。

並列アプリケーション

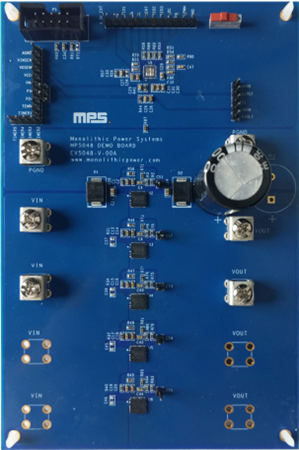

15Aの制限を超える電流を可能にするために、MP5048は並列アプリケーションで使用できます。図2は、複数のMP5048デバイスを並列に接続した一般的なアプリケーションの回路図を示しています。

図2: MP5048の並列動作の代表的なアプリケーション回路図

5ページの表1に、適切な機能を可能にするピン接続を示します。各CSピンには個別の抵抗器が必要であり、一緒に接続することはできません。また、すべてのCS抵抗器の抵抗値は同じである必要があります。

表1は、並列アプリケーションで接続する必要があるMP5048のピンを示しています。

表1: 並列アプリケーションに必要なピン接続

| ピン名 | 必要なピン接続 |

| CLREF | CLREFピンの通常電圧 (VCLREF_NORM) と電流制限 (ILIMIT) に基づいて各相に抵抗を配置します。VCLREF_NORMは式 (1) で計算できます:

$$V_{CLREF\_NORM} = I_{CLREF\_NORM} \times R_{CLREF}$$ ここでICREF_NORMはCLREF通常電流で、RCLREFはCLREF抵抗です。 ILIMITは式 (2) で計算できます: $$I_{LIMIT} = \frac {V_{CLREF\_NORM}}{(g_{CS} \times R_{CS})}$$ ここでgCSは、パワーFETが完全にオンのときの電流検出ゲイン (通常25µA/Aで、RCSはCS抵抗です。 さらに、CLREFとAGNDの間に1nF~10nFのコンデンサを配置します。 |

| ON | ON並列に接続されたすべてのMP5048は、同じイネーブル信号を確保するためにONピンを一緒に接続する必要があります。これは、ロジックデバイスから、またはVINピンとONピン間の抵抗分圧器を介して行うことができます。 |

| IMON | IMONピンは動作中に総電流を供給し、式 (3) で計算できます :

$$\text{総電流} = N \times \text{電気ヒューズ}$$

起動時に、IMONはMP5048デバイス間のソフトスタート (SS) 電流のバランスを取ります。各相に抵抗器を配置します。RCSの計算の詳細については、MP5048のデータシートをご参照ください。

等価IMON抵抗 (RIMON) は式 (4) で計算できます (RIMON): $$R_{IMON} = \frac{R_{cs}} {N}$$ ここで、Nは並列に接続されたデバイスの数です。 |

| GND | 各MP5048のGNDピンは同じグランド基準に接続する必要があります。 |

| VIN | VINピンは、電気ヒューズの高電圧 (HV) 入力です。並列に接続されたすべてのMP5048は、同じ電源プレーンに接続する必要があります。入力電圧 (VIN) がMP5048のデータシートに指定された制限を超えないようにするのを防ぐTVS保護デバイス装置が必要です。 |

| SS | 各相のSSピンとアナログ信号グランドの間にコンデンサを配置します。これにより、起動シーケンス中に同期されたソフトスタートが保証されます。 |

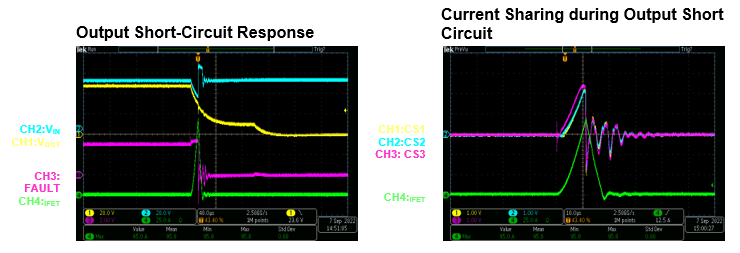

| VOUT | 並列に接続されたすべてのMP5048のVOUTピンは、同じ電源プレーンに接続する必要があります。過電流保護 (OCP) または短絡保護 (SCP) 状態時に高電流フリーホイールパスを提供するために、VOUTピンとGNDピンの間にショットキーダイオードを接続する必要があります。 |

| TIMER | 各相のTIMERピンとアナログ信号グランドの間にコンデンサを配置します。TIMERは、並列に接続されたすべてのICの挿入遅延、再試行遅延、およびOCPタイマーを同期します。 |

表2は、MP5048のオプションのピン接続を示しており、これらは個別または組み合わせて使用できます。

表2: オプションのピン接続

| ピン名 | オプションのピン接続 |

| VTEMP | VTEMPとアナログ信号グランドの間に、最小10kΩの抵抗と最大1nFのコンデンサを配置します。すべてのMP5048のVTEMPピンを接続してICの最高読み取り値を取得することも、個々の信号をルーティングして各電気ヒューズの温度を読み取ることもできます。 |

| VCC | 各相のVCCとアナログ信号グランドの間に1µFのコンデンサを配置します。各電気ヒューズのVCCピンは、一緒に接続することも、個別の接続のままにすることもできます。 |

| 3V | 各相の3Vとアナログ信号グランドの間に1µFのコンデンサを配置します。各フェーズの3Vピンは一緒に接続することも、個別の接続のままにすることもできます。 |

| FAULT | FAULTピンはオープンドレイン出力であり、システムに必要な電圧レベルに応じて、FAULTとVCC間、またはFAULTと3V間の10kΩ~100kΩのコンデンサを介してプルアップできます。FAULTは、詳細な電気ヒューズモニタリングのために個別の接続として残すことも、すべての電気ヒューズ用の複合故障信号を取得するために接続することもできます。 |

| MODE | MODEは、故障状態時に電気ヒューズの動作をヒカップモードまたはラッチオフモードのいずれかに設定します。すべてのMP5048のMODEピンは個別に設定できますが、並列に接続されたすべてのMP5048は同じMODE設定にする必要があります。MODEピンを接続してICの動作を設定できます。 |

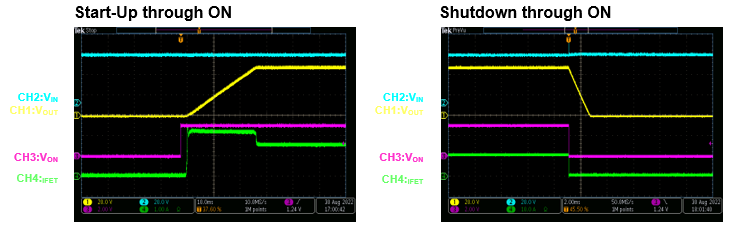

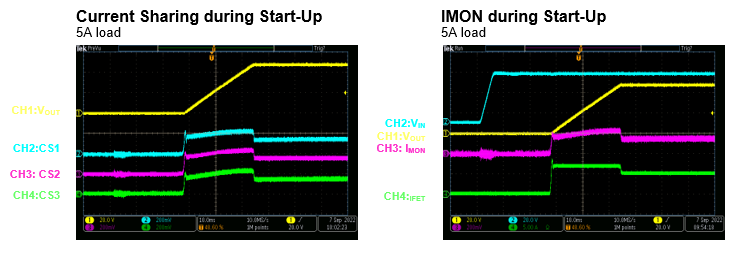

起動シーケンス中、並列に接続されたMP5048間の電流バランスは、SSピンとIMONピンの接続を使用して実現されます。SSピンは、並列に接続されたすべてのMP5048の起動シーケンス中にソフトスタート (SS) のランプレートが同じになることを保証します。これにより、出力電圧 (VOUT) 上昇に応じてMP5048間の固有の電流バランスを実現します。MP5048の1つで電流が増加するような状況が発生すると、IMONからの合計電流とCSピン経由の個々の電気ヒューズ電流を使用してアクティブ電流バランスループがアクティブになり、並列に接続されたMP5048全体の電流のバランスを取ります。

レイアウトに加えて、MOSFET抵抗の正の温度係数 (RDS(ON)) は電流のバランス調整に役立ちます。1つのMP5048がより多くの電流を流すと、ICはより熱くなり、RDS(ON)が増加し、他のMP5048に電流を強制的に流します。

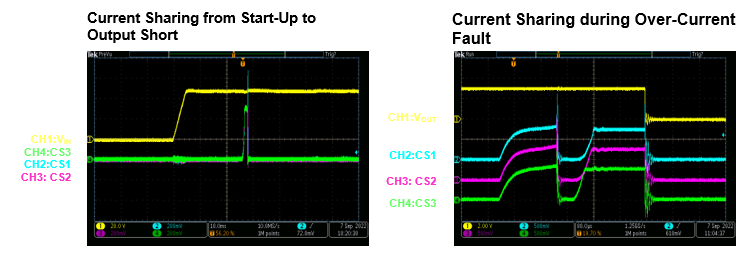

過負荷状態が発生した場合、並列に接続されたMP5048は設定された過電流保護 (OCP) しきい値に調整され、接続されたTIMERピンが充電を開始します。TIMERピンの電圧がトリップしきい値 (0.6V) に達すると、過電流 (OC) 状態のため、すべてのMP5048が無効になり、シャットダウンされます。MP5048がラッチオフモードに設定されている場合、故障をクリアするには2つの方法を使用できます。MP5048は、ONピンの電源がローサイクルの間故障状態のままで、再びハイサイクルになると故障状態がクリアされ、SSターンオンシーケンスが開始します。故障をクリアして完全なICリセットを実行するには、100msの間、入力電圧 (VIN) を3V未満に下げ、VCC電圧 (VCC) 低電圧誤動作防止機能 (UVLO) 下降しきい値をトリガーします。これにより、ICが完全にリセットされ、VINが上昇すると挿入遅延が発生します。

電源サイクル中にVINは100msの間3V以下に下がらないと、 並列に接続されたすべてのMP5048に対してVCC UVLO下降しきい値がトリガーされません。VCC UVLO下降しきい値をトリガーするMP5048は初期化モードに入り、VCC UVLO下降しきい値をトリガーしていないMP5048は通常動作のままです。MP5048の動作状態が異なる場合、並列に接続されたMP5048は正常に再起動しません。

MP5048がヒカップモードの場合、TIMERは並列に接続されたすべてのMP5048間の再試行時間をシーケンスします。再試行時間の終了時に、並列に接続されたMP5048が再度イネーブルになり、新しい起動シーケンスが開始されます。

パワーオンリセット (POR) VINを防止するためには、通常動作中に5.25Vの低電圧誤動作防止機能 (UVLO) しきい値を超える必要があります。

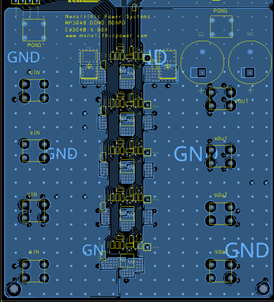

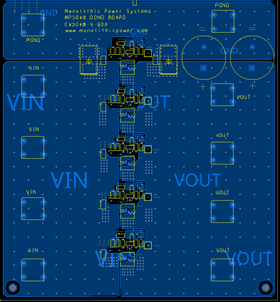

EV5048-V-00A評価ボード

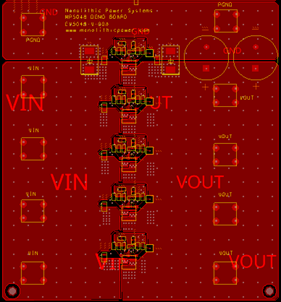

図3は5相EV5048-V-00Aを示しています。このアプリケーションノートでは、3相 EV5048-V-00Aを使用したテスト結果について詳しく説明します。

図3: EV5048-V-00A 評価ボード

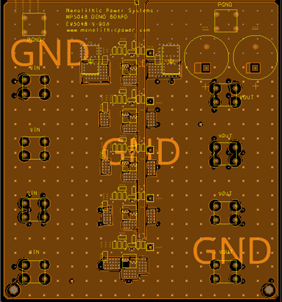

評価ボードのレイアウト

EV5048-V-00A評価ボードは、4つの層で構成されています (図4~図7参照)。各電気ヒューズの最上層は同じ形状になっており、定常動作中にすべてのMP5048間での電流バランスを実現します。

図4: EV5048-V-00A 最上層

図5: EV5048-V-00A 中間層1

図6: EV5048-V-00A 中間層2

図7: EV5048-V-00A 最下層

評価ボードの回路図

図8は、電気ヒューズのEV5048-V-00A評価ボードの回路図を示しています。

図8: EV5048-V-00A 電気ヒューズ回路図

波形

波形

このアプリケーションノートでは、適切な並列動作を保証するためにMP5048を使用したシンプルなシステム設計について説明します。並列アプリケーション向けの電気ヒューズ設計は、高電流回路保護の需要の高まりに柔軟に対応します。MP5048は、戦略的なピン接続と正の温度係数を提供し、高電流並列動作のための堅牢な回路保護と電流バランスを実現する多様なソリューションです。

_______________________

興味のある内容でしたか? お役に立つ情報をメールでお届けします。今すぐ登録を!

アカウントにログイン

新しいアカウントを作成