低EMI DC/DCコンバータのPCB設計

役立つ情報を毎月お届けします

はじめに

すべてのスイッチモード電源は、広帯域のノイズ源になります。DC/DCコンバータすべてのスイッチモード電源は、広帯域のノイズ源になります。

通常、DC/DCコンバータやその他の高速回路からのノイズは、効果的なアンテナパスを提供する接続されたケーブルを介して放射されます。この潜在的な放射パスを遮断するために、各ケーブルの接続ポイントにフィルタ回路が必要です。このフィルタリングは、ノイズ源からのHフィールドまたはEフィールドがフィルタ部品またはケーブルに結合しない場合にのみ有効です。

近いフィールド環境では、フィールドの振幅は、距離の2乗分の1 (1/d2) で減少します。したがって、ノイズ源、フィルタ部品、およびコネクタの間には、一定の最小距離が必要です。

残念ながら、ケーブルに対するPCBサイズとコネクタ位置は、通常、機械的な制約によって事前に決められています。さらに、PCBの特定の領域では部品の最大の高さが制限される場合があり、両面アセンブリが不可能な場合があります。これらの条件では、特に自動車製造などの規制の厳しい産業で作業する場合は、注意深い部品配置とPCBレイアウトが必要になります。

部品配置のプランニング

DC/DCコンバータのEフィールドおよびHフィールドがコネクタやケーブルに直接結合するのを避けるために、回路はPCB接続ポイントからできるだけ離して配置する必要があります (図1参照)。

図1 : ノイズ源をコネクタとケーブルから最大距離に配置

EMCフィルタ、コネクタ、およびケーブルでの電界強度を必要な低レベルに下げることができるのは、距離を離すか、シールドを追加することだけです。シールドは距離に代わることができるものです!

DC/DC回路とフィルタ部品が基板の反対側に配置する、少なくとも4層の両面アセンブリPCBを使用するのがベストです。ノイズ源からフィルタ回路へのクロスカップリングを最小限に抑えるために、少なくとも1つの内層をGNDベタにする必要があります。

DC/DC回路をコネクタのすぐ近くに配置する必要があるシステムでは、設計プロセスの早い段階で効果的なシールドを考慮する必要があります。熱的に必要なヒートシンクをシールドに使用できる場合も時々あります。理想的には、インダクタ、パワーMOSFETを備えた DC/DC IC、およびそのデカップリング・コンデンサのすべてをシールドの下に配置します。

PCBレイアウトのガイドライン

ステップダウン・コンバータで、主なフィールドソースは次のとおりです :

- 2つの電源スイッチとCINによって形成され、広帯域の磁場を放射する高di / dt ループ (ホットループ)

- 強いEフィールド放射をもつ、パワーFETとインダクタ間のSWノード

- EフィールドとHフィールドを放射するインダクタ

AC磁場は、渦電流の誘導を可能にする個体金属領域によってシールドされます。導電率が高いため、銅は非常に効果的です。PCB上の固定電位に戻る電位差の経路にある導体は、Eフィールド放射を効果的にシールドします。

高di / dtループは、ループ面積と電流振幅に比例するHフィールドを放射します。アンテナループ領域を最小限に抑えるために、低インピーダンス接続で入力コンデンサを2つの電源スイッチ近くに配置します。

このループからの磁場をさらに減らすために、2組のコンデンサを電源スイッチに対称に配置します。理想的には、両方のループのピーク電流が元の半分になり、Hフィールドが6dB減少します。2つのループの向きが逆になっているため、放射されるHフィールドがさらに減少します。 (1)

DC/DC回路の下の層には、100µメートル未満の距離が空いた、GNDベタ領域が必要です。この銅領域では、回路部品とPCB配線を流れる高di / dt電流が渦電流を誘導します。渦電流は部品側で元の電流とは逆向きに流れ、それらの磁場は元の磁場を打消します。これは、渦電流が部品側からの高di/dtループ電流を最小限の距離で鏡像化できる場合に最適に機能します。

これにより、PCBの部品側からのHフィールド放射が減少します。理想的なケース (超伝導、ゼロ距離、および両方のループ形状の完全な一致) では、渦電流からのHフィールドによって打ち消されます。

DC/DC回路の下のGNDの銅領域にはインピーダンスがあるため、高di / dtの渦電流によって電位差が生じ、この領域にノイズが発生します。このノイズの多いGND領域は、システムのGND領域、特にフィルタやコネクタのGND基準から分離する必要があります。多層PCBで、個々の層の形状や、層間を接続するビアのインピーダンスによって、これらは分離されます。

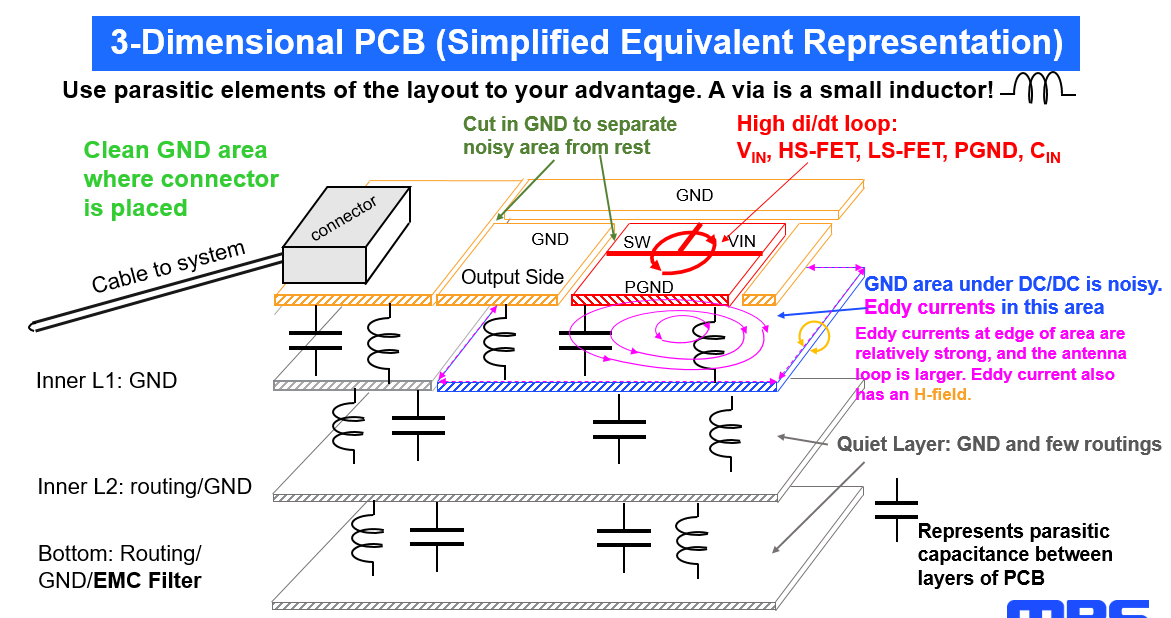

多層PCBの3次元図は、この概念を示しています (図2参照)。

図2 : PCBの3次元図 – レイアウトは回路の一部

注 :

1) 「 Henry W. Ott, Electromagnetic Compatibility Engineering, John Wiley, 2009」をご参照ください。

最上層では、入力コンデンサ (CIN) と2つのパワーFETがVIN領域とPGND領域 (赤色で表示) をつなぎ、ビアを介して内層に接続されます。VINパスに関して、ビアの後の部品は誘導性素子でなければなりません (例 : 1µH~2µHのコイル)。スイッチ遷移による高di/dtの電流は、CINのみに強制的に流れ、PCBを横切りません。

PGND領域は部品側の他のGNDに直接接続されておらず、DC/DCブロック (青色で表示) の下のPGND領域へのビアを介してのみ接続されています。目的は、高周波電流を部品側に保ち、ノイズを「外界」から分離することです。低インピーダンスのシステム基準を提供するために、少なくとも1つの層をPCBの全サイズでGNDベタにする必要があります。レイアウトは回路の一部であることを忘れないでください。

インダクタの下に銅を配置するべきか?

一部のPCBレイアウトツールは、インダクタコアの下に銅線を配置できないよう事前設定されています。この問題に関する見解には、銅をまったく使用しないという見解から、PCBの部品側のコイルの真下に銅を使用するという見解までさまざまあります。

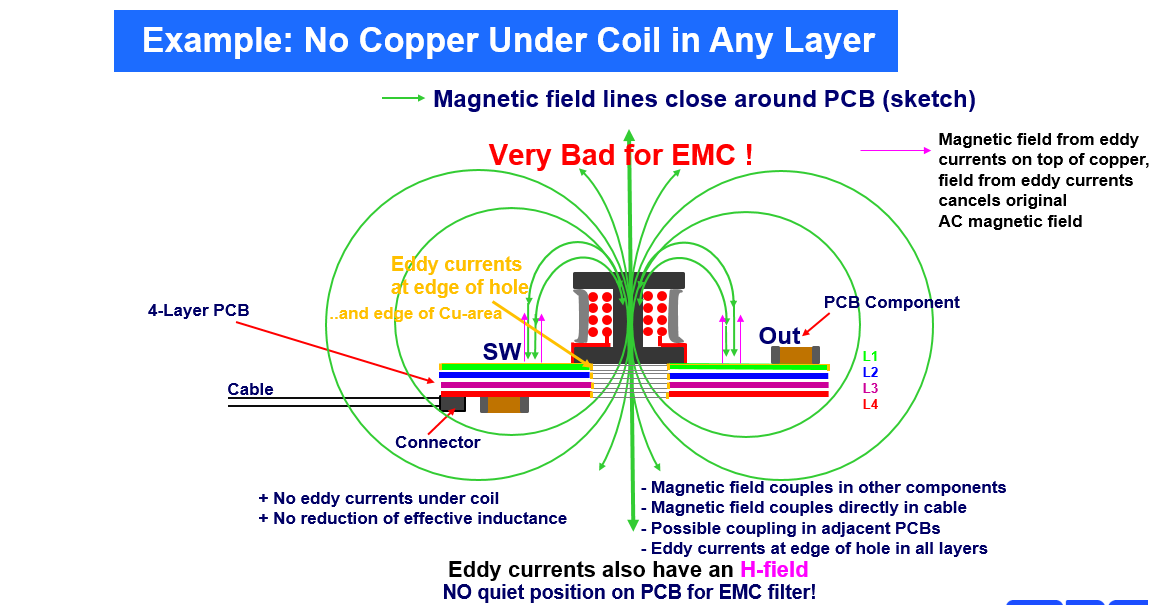

図3 : コイルの下に銅を使用しない4層PCB

図3は、4層PCBのどの層でもコイルの下に銅がない場合のコイルの周囲の磁場の略図を示しています。コイルからの強力な磁力線はPCBの底面に存在し、PCBの周囲で閉じており、接続されたケーブルに効果的に結合します。PCB上のフィルタ部品は空気を介してバイパスされます。これにより、車載用OEMの電磁両立性レベルを満たすことは、不可能ではないにしても非常に困難になります。

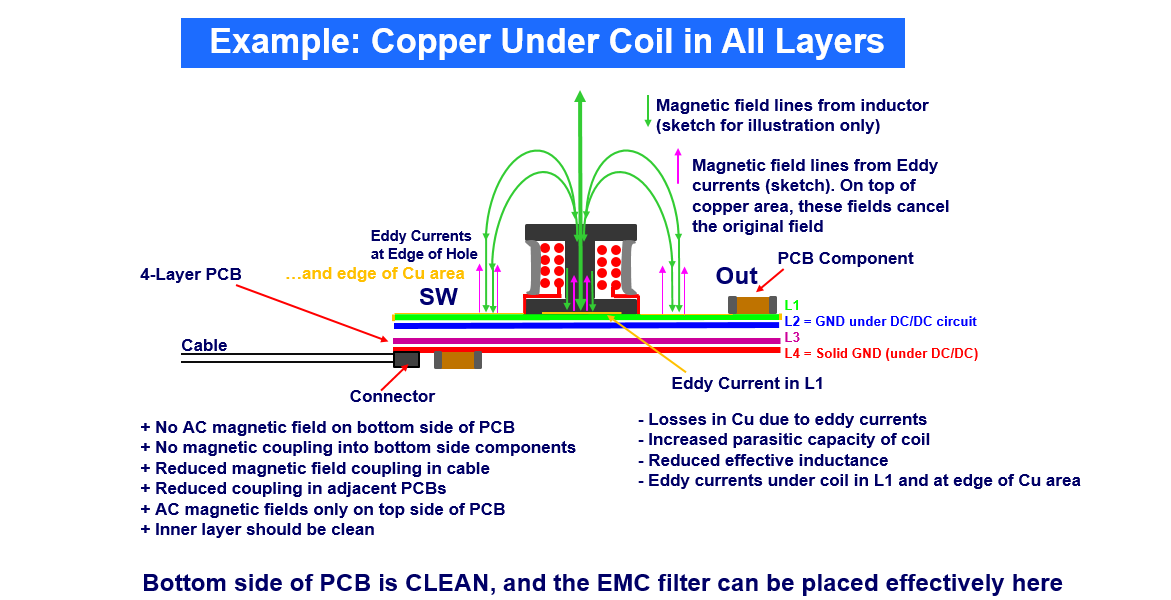

図4は、部品側のコイルの真下に銅を配置したPCBレイアウトを示しています。

図4 : PCBのコイルの下にある銅の効果

これにより、渦電流がPCBの外側にすでに存在する磁場を打ち消すための領域が提供されます。内層2と底面層はクリーンです。電磁両立性用フィルタ部品は底面に効果的に配置できます。渦電流の磁場は、コイルの実効インダクタンスをいくらか減少させます (通常5%未満)。渦電流は、GNDの銅にもいくらかの損失を生じさせます。インダクタのコア直下の銅によるもう1つの小さなデメリットは、巻線からGNDへの寄生容量が増加することです。ただし、ほとんどの設計では、静電容量が非常に小さいため、この影響は支配的なものではありません。

PCBレイアウトの例 : MPQ443xファミリ

MPQ443x ファミリは、動作静止電流が低く、出力電流が1A~3.5Aで40Vの同期整流式降圧コンバータで、車載用および産業用アプリケーションに最適です。

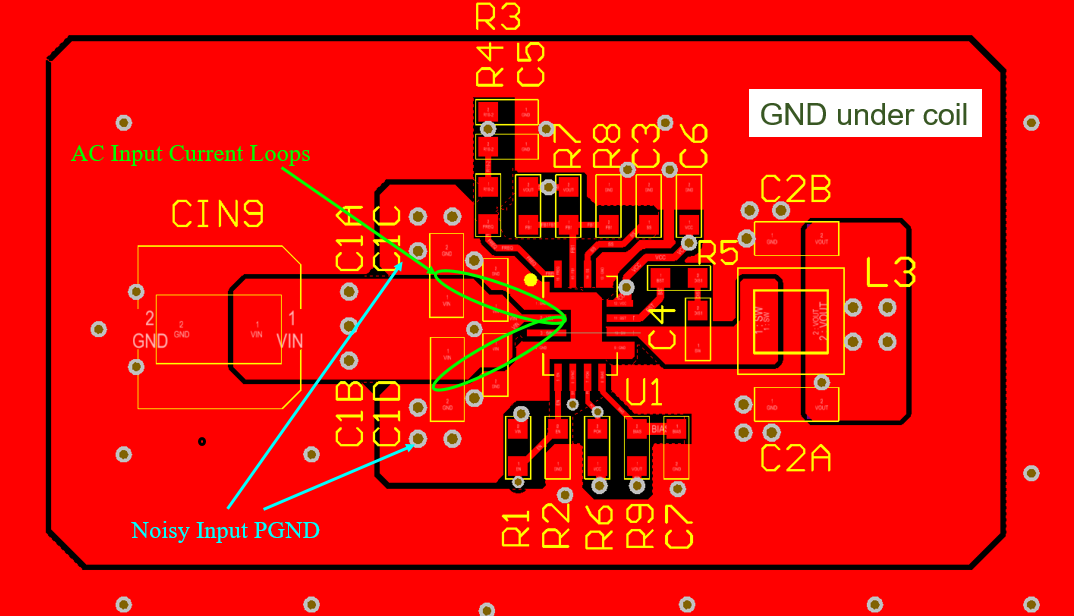

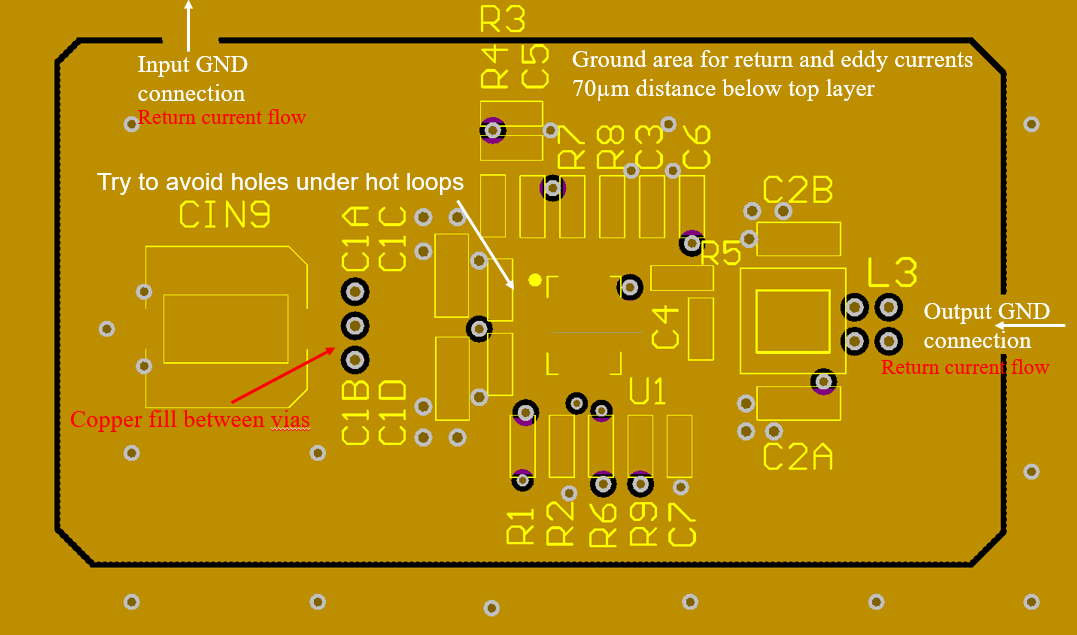

CBの上部には、MPQ4430 IC (U1) に対称なCIN一式 (C1A-C1D) があります。これらのコンデンサのGNDは、底面のFETのソースであるICのPGNDピンに直接接続されます。この部分的GND領域には非常に多くのノイズがあります。部品側では、このGND領域は他のGND領域に直接接続されていません。唯一の接続は、DC/DC回路の下層のGND領域へのビアを通じた接続です。この構成では、電力段からの高di / dt電流は部品側にとどまります。電流密度が最も高いのは、VINとPGND間の配線の内側の端で、例の中で緑色の楕円で示されています (図5参照)。

図5 : MPQ4430 PCB最上面レイアウト

VINはビアによってレイヤ3に接続されます。ビアのインダクタンスにより、入力電流の高周波部分が最上面に残ります。CIN9は、IC上のこのVINノードを減衰させますが、高さ6mmでGNDにカソード接続されているため、SWノードとコイルからの電界放射の一部も遮断します。

上面のDC/DCブロック周りのカットは、すべての高周波電流をこの領域内に保ちます。カットがないと、ホットループ電流の一部がPCBのコーナーに流れ、その領域にノイズが発生します。

高dV / dtのSWノードはインダクタに接続されていて。このインダクタは通常大きく、そしてEフィールドを放射します。ほとんどのインダクタでは、巻き始めがSWノードに接続されている場合、Eフィールドの放射は小さくなります。

コイルからのEフィールド放射を減らす1つの方法は、コイルの両側に出力コンデンサ (C2A & C2B) を配置することです。これは、コンデンサがコイルと同じかそれ以上の高さにある場合に最も機能します。一般に、小型で薄型のインダクタは、大きくて高いコイルよりもすぐれた電磁両立性性能を提供します。

図6 : 内層1 推奨 PCBレイアウト

電磁両立性最適化基板の内層1はGNDです。最上面の下の70µmに配置する必要があります (図6参照)。このGND領域にはノイズが多くあります。DC/DCブロック周囲のGND領域のカットアウトにより、コネクタおよびフィルタ部品の下層の端で残留電流が流れるのを防ぎます。カットには、正確な位置に2つの狭い開口部が必要です。VINおよびVOUTは 下層のDC/DC回路につながれ、明確で局所的なリターンパスを提供します。

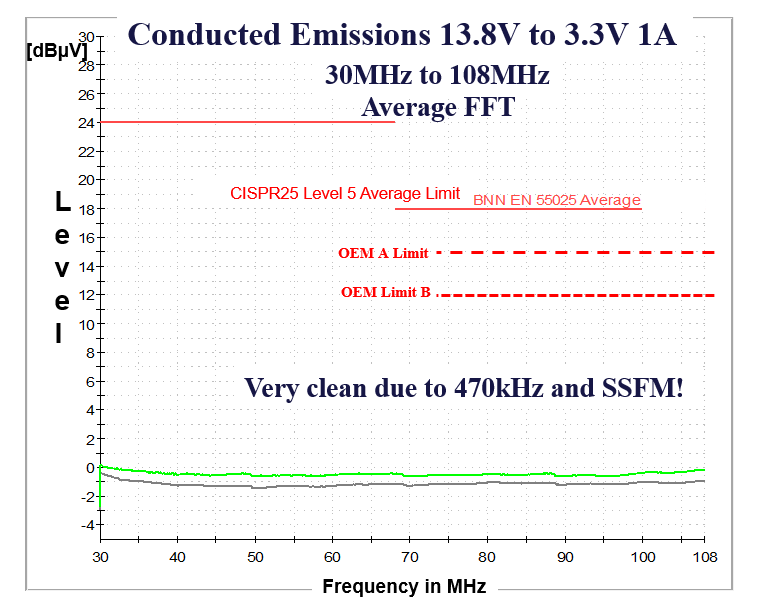

結果 : 伝導エミッション 30MHz~100MHz

fSW = 470kHzおよびスペクトル拡散周波数変調 (SSFM) の場合、30MHz~108MHzまでのCEテスト結果は約0dBµVで、システムノイズをわずか数dB上回るだけです (図7参照)。

図7 : CEテスト結果、30MHz~108MHz

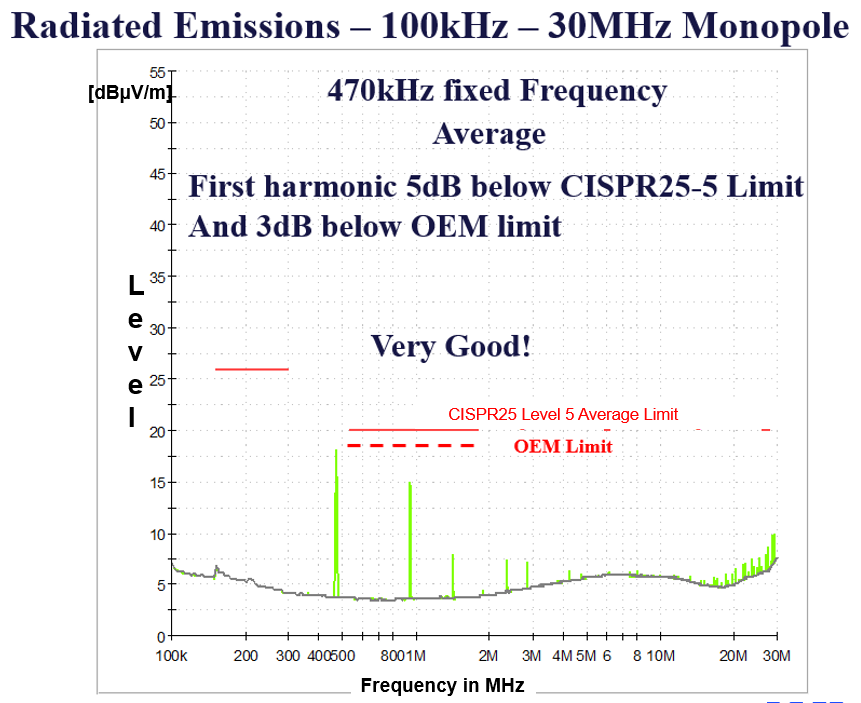

0805 2.2µHインダクタと2つの0805出力コンデンサを備えた470kHzでのMPQ4431のスイッチングは、追加のシールドやSSFMなしで低周波REモノポールテストに合格しました (図8参照)。

図8 : 低周波モノポール試験結果

結論

寄生要素を含むレイアウトは回路の一部であるという観点から、PCB設計は DC/DCコンバータの低EMI向けに最適化できます。MPSのMPQ4431降圧コンバータは、慎重な部品配置と基板レイアウトによって、自動車市場内の厳しい電磁両立性制限を満たすことができることを実証しています。

_______________________

興味のある内容でしたか? お役に立つ情報をメールでお届けします。今すぐ登録を!

アカウントにログイン

新しいアカウントを作成