AN145 -マルチモードPFC + 電流モード LLCコントローラ

役立つ情報を毎月お届けします

プライバシーを尊重します

1. はじめに

HR1211は、マルチモードPFCコントローラと電流モードHB LLCコントローラを集積し、非常に高いパフォーマンスを発揮するコンビネーションコントローラです。詳細については、HR1211データシートを参照してください。

1.1 主な機能

1. 一般的な機能

- 起動用の高電圧電流源

- ACが接続されていないときのスマートXコンデンサ放電器

- パラメータプログラミング用のUARTインタフェース

- PFCおよびLLC設計を最適化するためのユーザーフレンドリーなGUI

2. 力率補正 (PFC) コントローラ

- 軽負荷から全負荷まで高効率の特許取得済みCCM / DCMマルチモードPFCコントローラ

- 入力コンデンサの電流補償による高効率

- 電磁干渉 (EMI) を低減するための設定可能な周波数ジッタ

- 正確な調整と自動調整可能な出力電圧

- 電圧ループ補償用のデジタルPI

3. ハーフブリッジLLCコントローラ

- 集積ブートストラップ (BST) ダイオードと高いdV/dt耐性を備えた600Vハイサイド (HS) ゲートドライバ

- 電流モード制御

- 最小および最大制限による適応デッドタイム調整

- 軽負荷運転時のスキップ / 昇圧モード切り替え

- 設定可能なソフトスタート

4. 保護

- 正確な復電 / 停電保護 (設定可能なしきい値と再起タイマ)

- サイクルごとの電流制限

- PFC出力過電圧保護 (OVP)

- 設定可能なPFC開ループ保護 (OLP)

- 短絡保護 (SCP)

- LLC過電力保護 (OPP)

- 外部保護用のSOピン

- LLC静電容量モード保護

- 過熱時遮断 (TSD)

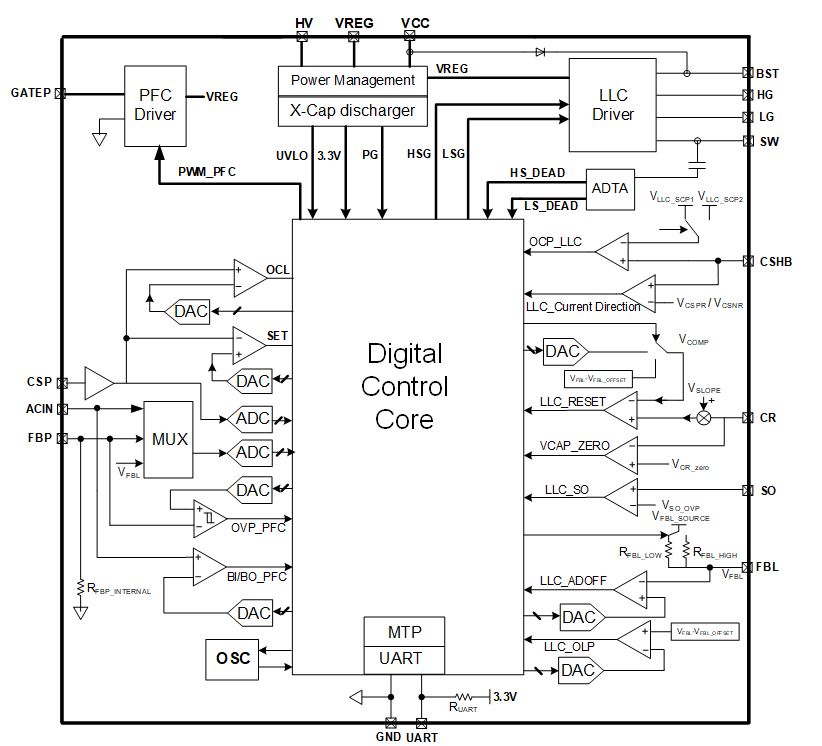

1.2 ブロック図

図1に、HR1211のブロック図を示します。機能は以下のとおりです。

- 電源管理

- デジタルPFCコントローラ

- デジタルHB LLCコントローラ

- MTPおよびUART通信

図1: HR1211ブロック図

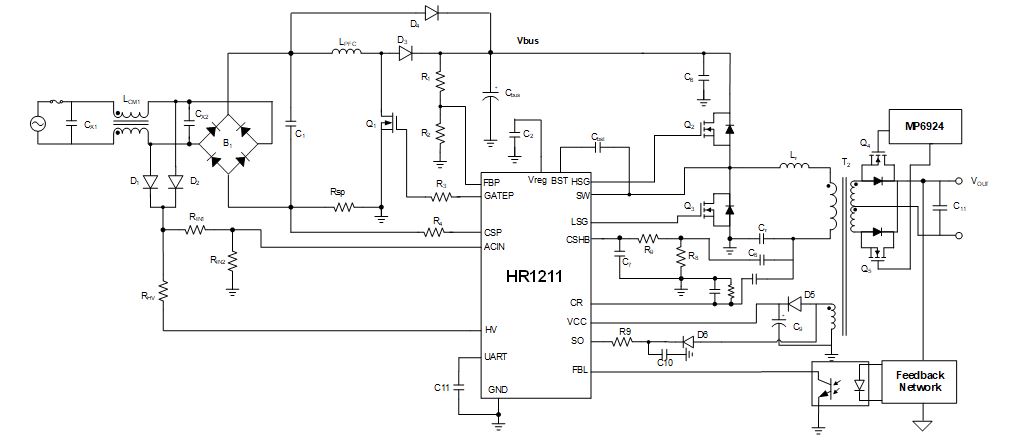

2. 代表的なアプリケーション回路

図2: 代表的なアプリケーション回路

3. 電源機能

HR1211の電源セクションには、ICを起動するための高電圧電流源 (HVCS)、ゲートドライバに電力を供給するためのVREGレギュレータ、およびデジタルコアに電力を供給するための3.3Vレギュレータが含まれています。HR1211には、ICをより堅牢にするための監視回路と保護回路があります。

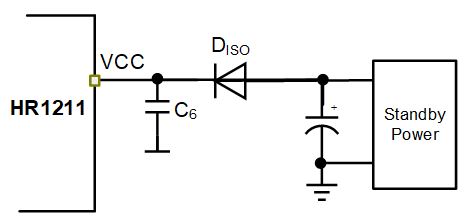

3.2.1 外部電圧によるVCCの供給

外部電圧は、待機電力またはDC電力にすることができます。通常、VCC電圧はVCCUVP2より高くなければなりません。HVCSがVCCを充電しているときにICに正常に電力を供給するために、スタンバイ電力をVCCから分離するためにダイオードを追加する必要があります(図7を参照)。

図7: VCCに待機電力を供給する

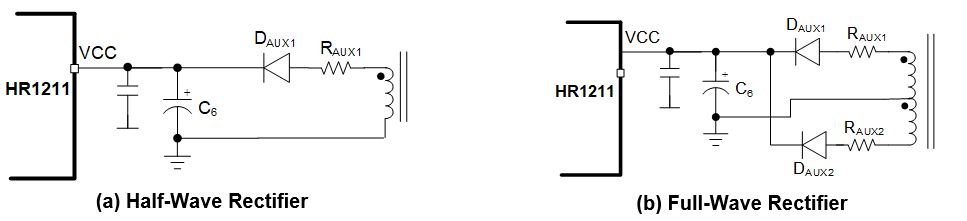

3.2.2 LLC補助巻線によるVCCの供給

非スタンバイ応用の場合、VCCはLLC補助巻線によって供給され、効率が向上します。図8は、半波整流器と全波整流器の2種類の補助巻線構成を示しています。通常、全波整流器は効率が高く、2つの巻線の巻数が同じである場合、より大きなVCCを生成するため、軽負荷での効率が向上します。ただし、全波整流器には別の巻線と整流ダイオードが必要であり、コストが高くなります。

図8: LLC補助巻線を備えたVCCへの供給

3.2.3 VCC電流

VCCが消費する電流には、内部回路のV3.3電流、VREG電流、バイアス電流が含まれます。合計電流は、これら3つの電流の合計です。

t0からt2の期間、およびV3.3が有効になる前は、VCCの電流は約200μsです。V3.3が有効になっている間、ICが有効になる前(t2からt3およびt7からt9)、VCCの電流はICC_START1です。ICが有効になると、VCCの電流は通常動作ではICC(NOR)になり、昇圧オフモードではICC_BURSTになります。

4.3 PFC出力レギュレーション

PFC出力電圧VBUSは、デジタルPIループによって調整されます。図13のROUT1とROUT2の精度が1%の場合、ADCの精度が約0.6%であることを考慮すると、VBUSの精度は2.5%以内です。

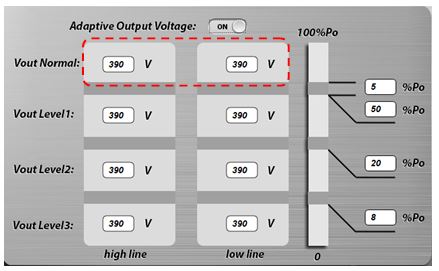

PFCの効率を最適化するために、HR1211はさまざまな入力電圧および出力負荷条件で出力電圧を自動調整できます。例えば、入力電圧が低い場合、出力電圧を低く設定することができます。図24は、いくつかのパラメータを設定する方法を示しています。

図24: 出力電圧レギュレーションのGUIインタフェース

4.4 PFCの昇圧動作

出力負荷が減少しているとき、PFCコンバータは昇圧モード動作で動作します。昇圧モードに入るレベルはプログラム可能であり、VCOMP_FULLのパーセンテージを使用して設定されます。

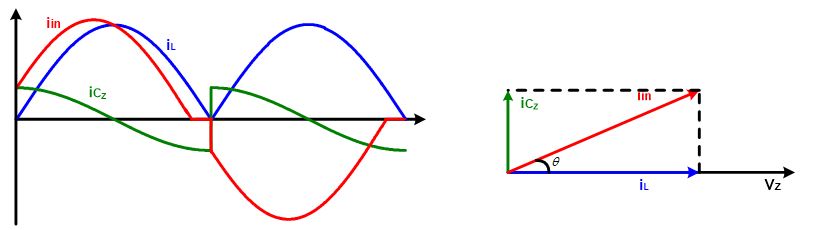

4.7 PF補正

EMI要件を満たすために、Xキャップは通常LラインとNラインの間に接続され、ブリッジダイオードの出力に接続された高電圧コンデンサも常に高電圧キャップと並列に接続されています。図32に示すように、入力電流は歪んでインダクタ電流よりも先にシフトします。CZを流れる電流 (Xキャップとブリッジ後の高電圧キャップ) は、式 (36) で計算できます。

$$i_{C_Z} (t) = C_{Z} \frac {dV_{in} (t)}{dt} = 2 \times \pi \times f_{line} \times C_z \times \sqrt 2V_{in_{rms}} \times cos (2 \times \pi \times f_{line} \times t)$$

ここで、fLINEは入力電圧の周波数です。

図32: 入力電流、C1電流、インダクタ電流の関係

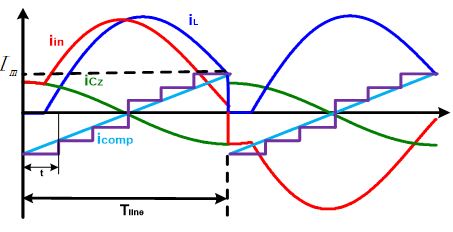

この電流は、軽負荷で入力電流の位相シフトを引き起こし、力率とTHDを悪化させます。HR1211 は、ICZを補正するためにデジタル三角波を実装しています (図34を参照)。

図34: 三角波による補償

4.10 プログラム可能なデジタルフィルタ

4.10.1 電流センスフィルタ

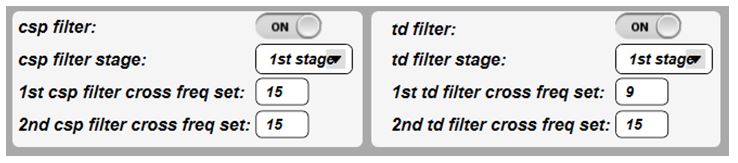

HR1211は、ノイズ耐性を向上させるために、2つのプログラム可能なデジタルフィルタ (cspフィルタとtdフィルタ) を内部に実装しています。

cspフィルタとtdフィルタはどちらも2次フィルタであり、GUIで構成できます (図42を参照)。フィルタ機能は、ボタンセットが「ON」の場合に有効になり、ボタンセットが「OFF」の場合は無効になります。各次数フィルタには15レベルの帯域幅があり、実際のアプリケーションに応じて柔軟に選択されます。

図42: プログラム可能なデジタルフィルタのパラメータ

4.10.2 電圧検出フィルタ

PFC出力電圧検出の干渉防止機能を強化するために、HR1211はFBP検出にプログラム可能なフィルタを実装しています。デジタルフィルタのカットオフ周波数は、3つのレベルでプログラム可能です。電圧検出フィルタを使用すると、Rout2と並列のコンデンサ (C3) を減らすことができ、動的応答を改善し、過電圧保護の精度を向上させることができます。

5. HB共振機能

ハーフブリッジ共振コンバータ (LLC) は、ゼロ電圧スイッチング (ZVS) の利点を備えた高効率を達成できます。HR1211は、LLCコンバータに特許取得済みの電流モード制御方式を使用しています。

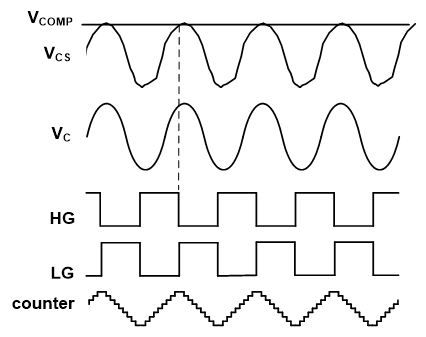

5.1 電流モード制御

図45は、LLCスイッチング周波数を決定するCRおよびFBL電圧を検出することによるLLC電流モード制御戦略を示しています。

図45: LLC電流モード制御戦略

5.2 LLC動作モード制御戦略

スイッチング損失が増加します。HR1211は、出力電圧を制御し、消費電力を制限するために、軽負荷でのスキップモード動作と非常に軽負荷での昇圧モード動作を実装し、平均スイッチング周波数を大幅に低減して磁気損失を低減します。

5.2.2 昇圧モードの動作

負荷がさらに軽くなると、平均スイッチング周波数をさらに制限するために、より長いスイッチアイドル時間がスキップモードに挿入されます。これは昇圧モード動作と呼ばれます。

5.2.2.2 超低電力モード

ICの消費電力をさらに削減するために、HR1211は昇圧オフ期間中に超低電力モードを実装します (PFCとLLCの両方が昇圧モードに入ります)。超低電力モードでは、システムクロックが1/10に短縮され、内部バイアス電流の一部がシャットダウンします。ICの総消費量は ICC_BRUST (通常1.8mA) に削減されます。

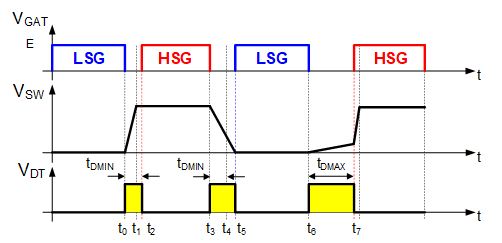

5.4 LLC の適応デッドタイム調整 (ADTA)

アダプティブデッドタイム制御機能により、デッドタイムが自動調整され、LLCコンバータはZVSにより軽負荷から全負荷まで高効率を実現します。

図59は、ADTAロジックで発生する可能性のあるデッドタイムを示しています。デッドタイムには、最小デッドタイム (tDMIN)、最大デッドタイム (tDMAX)、調整済みデッドタイムの3つがあり、値はtDMINとtDMAXの間にあることに注意してください。SWの遷移時間がtDMINより小さい場合、ロジックはtDMINに達するまでHGまたはLGのゲートを防ぎます。これにより、ハイサイドおよびローサイドMOSFETのシュートスルーを回避できます。デッドタイムが長すぎると、デューティサイクルの損失やソフトスイッチングの損失につながる可能性があります。最大デッドタイムtDMAXが設定され、ゲートをスイッチオンに強制します。tDMINとtDMAXの両方をGUIでプログラムできます。

図59: 波形はADTAを示します

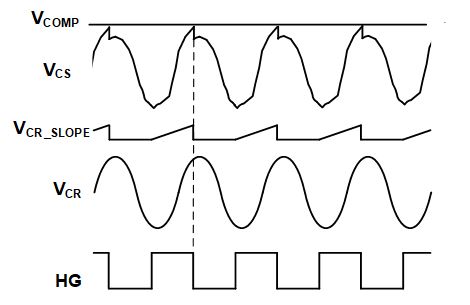

5.5 スロープ補正機能

電流モード制御の安定性のために、デジタル4ビットのプログラム可能なスロープ電圧VCR_SLOPEが検出された電圧VCRに追加され、VCSを生成します (図60を参照)。

図60: スロープ補償波形

5.7 LLC共振タンクのパラメータの設計

オンライン設計ツールはこちらでご利用いただけます。

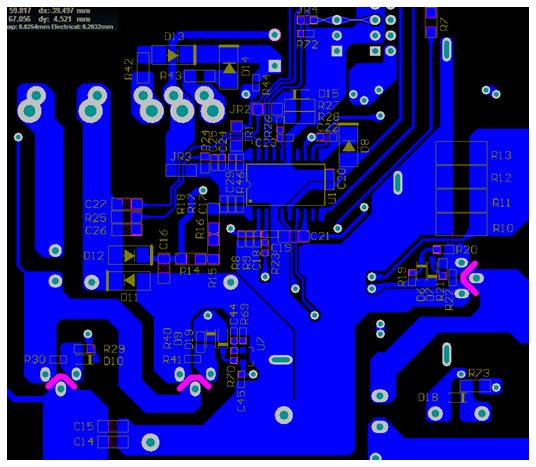

8. レイアウト

このセクションでは、ルーティングおよび主要コンポーネントをレイアウトに配置する際の重要な考慮事項について説明します。

図74に、単層ボードのGND接続の例を示します。PGNDとGNDDを接続し、IC下のグランド面積をできるだけ大きくしてから、バスコンデンサの負ポートに直接接続します。

図74: レイアウト例

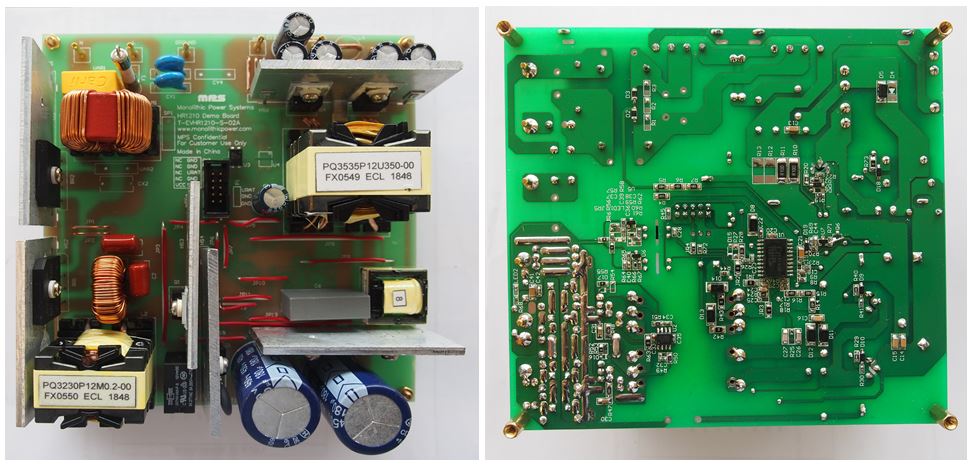

9. 設計例

このEVB (評価ボード) は、HR1211のパフォーマンスの検証と評価のために設計されています。EVBの詳細については、EVBデータシート 9.2 EVBを参照してください。

_______________________

興味のある内容でしたか?お役に立つ情報をメールでお届けします。今すぐ登録を!

アカウントにログイン

新しいアカウントを作成