MPSの電源モジュールはAMD Xilinx Zynq UltraScale+ RFSoCにコンパクトで超低ノイズのソリューションを提供

Heng Yang, Ph.D., MPS シニアアプリケーションエンジニア

ワイヤレスネットワークとデータセンターの帯域幅の増加によって駆動される高性能FPGAおよびASICアプリケーションが増加し、高電力密度、高速負荷過渡応答、およびインテリジェントな電源管理機能を備えた電力レギュレータが必要となります。AMD Xilinx ZYNQ UltraScale+ RFSoCは、マルチギガサンプルRFデータコンバータとソフトデシジョン前方誤り訂正 (SD-FEC) をSoCアーキテクチャに集積します。新しいファミリは、ARM Cortex-A53処理サブシステム、UltraScale +プログラマブルロジック、およびZYNQ UltraScale+デバイスで最高の信号処理帯域幅を備えており、ワイヤレス、ケーブルアクセス、テストと測定、早期警戒/レーダー、およびその他の高性能RFアプリケーションを提供します。ただし、ZYNQ UltraScale+ RFSoCの高度な集積は、電源ソリューションの設計に課題をもたらします。さらに、RFデータコンバータの性能は、電源のノイズレベルと密接に関連しています。MPS電源モジュールは、高効率の動作と最小化されたボードスペースの両方を提供します。このアプリケーションノートでは、AMD Xilinx ZYNQ UltraScale+ RFSoCの電源ソリューションの設計について概説します。RFデータコンバータに超低ノイズ電圧を提供するように設計されたEVREF0102Aリファレンスデザイン電源が示されています。

電源アーキテクチャ

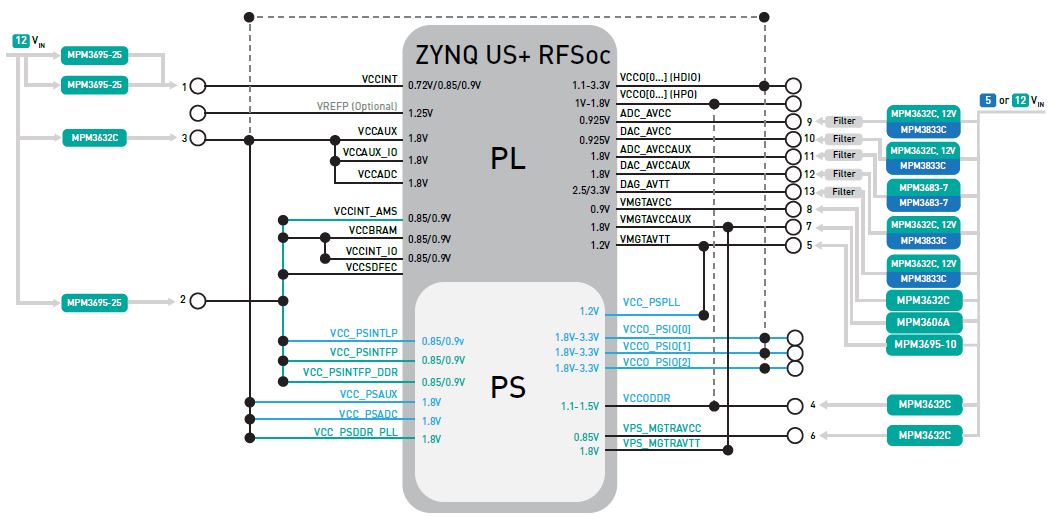

ZYNQ UltraScale+ RFSoCの電源アーキテクチャを図1に示します。図に示すように、RFSoCには30を超える電源レールが必要です。PLドメインの電源レールはRFSoC用であり、PSドメインの電源レールは組み込みARMコア用です。パワーレールは、必要なコンバータの数を最小限に抑えるために集積されています。MPSの電源モジュールソリューションは、PCBスペースを最小限に抑え、電源設計を簡素化します。

図1: ZYNQ UltraScale+ RFSoC用のMPS電源ソリューション

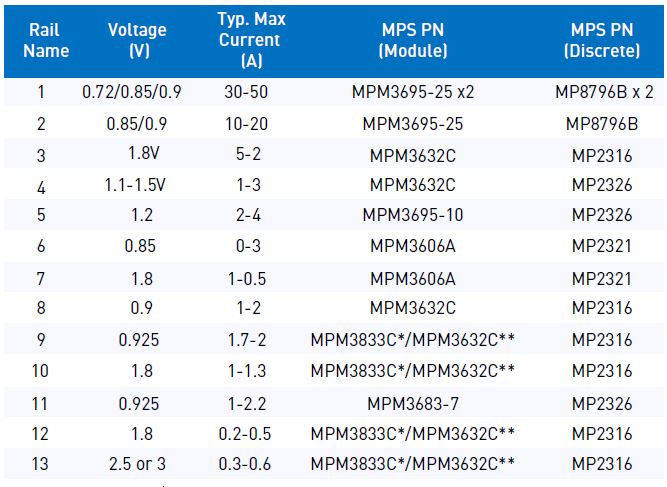

各レールの現在の仕様は、RFSoCで実行される部品番号および特定のアプリケーション / プログラムによって異なります。 表1は、ZYNQ UltraScale+ RFSoCファミリの各レールの一般的な電流要件を示しています。正確な電流要件を見積もるには、電力ソリューション設計の最適化のため、AMD Xilinx 電力見積もり (XPE) ツールを使用することをお勧めします。

電圧と電流の仕様に加えて、AMD Xilinx FPGAパワーレールの電源装置は次の要件を満たしている必要があります。

- すべてのパワーレール (アナログレールを除く) の出力電圧リップルは、定常状態で10mV未満である必要があります。

- すべてのパワーレールの起動は単調でなければなりません。

- コアレールの出力電圧偏差 (VCCINT) は、100A /μsで25%の負荷過渡時に±3%未満である必要があります。

- 電源装置のターンオンおよびターンオフは、AMD Xilinxによって定義された特定のシーケンスに従う必要があります。

*最大6Vの入力電圧をサポートします。**12Vの入力電圧をサポートします。 ディスクリート・ソリューションを見るにはこちらをクリックしてください。

表1: AMD Xilinx ZYNQ UltraScale+ RFSoC用のMPS電源モジュールソリューション

電源モジュールによる最適化された電源ソリューションの実現

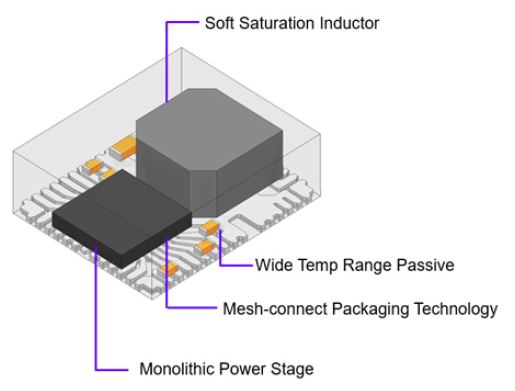

MPS電源モジュールは、高効率で高度に集積された電源ソリューションを提供します。 図2は、MPSの特許取得済みモノリシックIC、インダクタ、および選択された受動部品を単一の成形パッケージに統合した、MPS電源モジュールの典型的な構造を示しています。このコンポーネントはMesh Connect™ パッケージングテクノロジーを使用してリードフレームに取り付けられます。これにより、パワーIC / インダクタとPCB間の熱抵抗が最小限に抑えられます。モノリシックICは、パワーFET、制御回路、およびドライバを単一のシリコンダイに集積します。モノリシック技術は、ドライバ回路とパワーFETのゲート間の寄生抵抗とインダクタンスを最小限に抑えます。その後、スイッチング損失が最小限に抑えられます。

表1に、AMD Xilinx ZYNQ UltraScale + RFSoC向けMPS電源モジュールソリューションを示します。ディスクリート・ソリューションはMPSから入手できます。

図2: MPS電源モジュールの代表的な構造

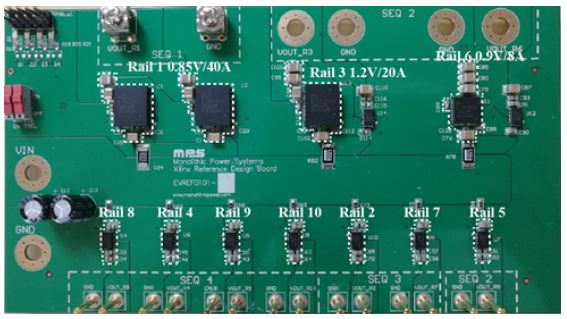

図3は、AMD Xilinx ZYNQ UltraScale + RFSoCのリファレンスデザインボードを示しています (RFデータコンバータレールを除く) 。リファレンスデザインボードは、5つの高度な電源モジュールを採用しています。 MPM3695-25は、16V、20Aの電源モジュールです。コアレールは、最大50Aのピーク電流を提供するために並列に接続された2つのMPM3695-25を利用します。単一のMPM3695-25は、レール2に最大25Aのピーク電流を供給します。MPM3695-10は、14V、7Aの超薄型電源モジュールです。MPM3632Cは、18V、3Aの強制CCM電源モジュールです。

図3: ZYNQ UltraScale + RFSoCのリファレンスデザインボード

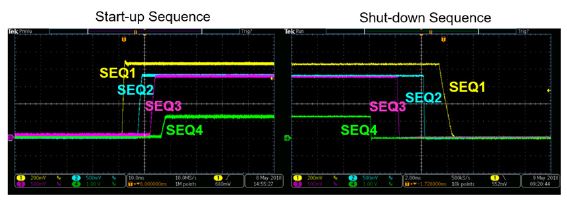

図4: パワーアップおよびパワーダウンシーケンス

MPM3606Aは、21V、0.6Aの電源モジュールです。同じファミリは、1A、2A、および3A電源モジュールを備えたピン互換電源モジュールも提供します。これにより、電源ソリューションの設計に大きな柔軟性がもたらされます。リファレンスデザインのパフォーマンスは、AMD Xilinxの要件を満たすように完全に検証されています。 図4に、電源のオンとオフのシーケンスの波形を示します。

インダクタが集積された高度なMPM3695シリーズの電源モジュールは、FPGAおよびASICに電力を供給するための多用途のソリューションを提供します。MPM3695シリーズの出力電流は、複数のMPM3695-25またはMPM3695-10を並べることで拡張可能です。MPM3695シリーズは、離散的な負荷点 (POL) ソリューションと比較して最大60%の高い電力密度、簡略化されたPCBレイアウトと電力段設計を提供し、しかも最小限の外部コンポーネント、電力コンバータおよび補償ネットワーク設計に対する最低限の専門知識しか要求しません。MPM3695シリーズの電源モジュールは、高度なパッケージング技術を備えた電源ICとカスタマイズされた集積インダクタ設計のモノリシック構造により、競合する電源モジュールと比較して最大40%の実装面積削減を達成します。

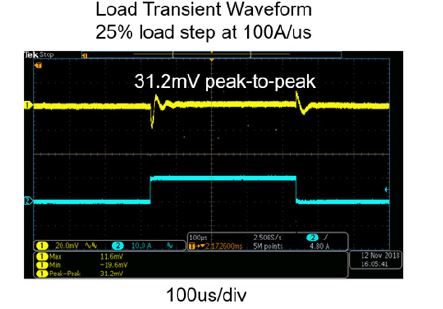

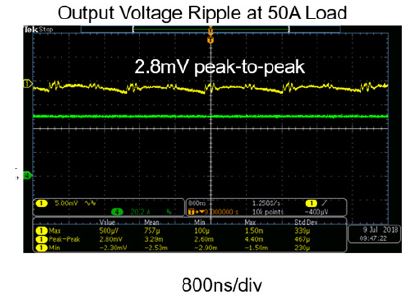

図5と図6は、それぞれ100μA/ sでの25%負荷過渡時の負荷過渡波形と全負荷時の出力電圧リップルを示しています。図に示すように、負荷過渡時の出力電圧偏差は±3%未満であり、定常状態での出力電圧リップルは10mV未満です。

図5: コアレールの負荷過渡波形

図6: コアレールの出力電圧リップル

ZCU1275用アナログ電源モジュール

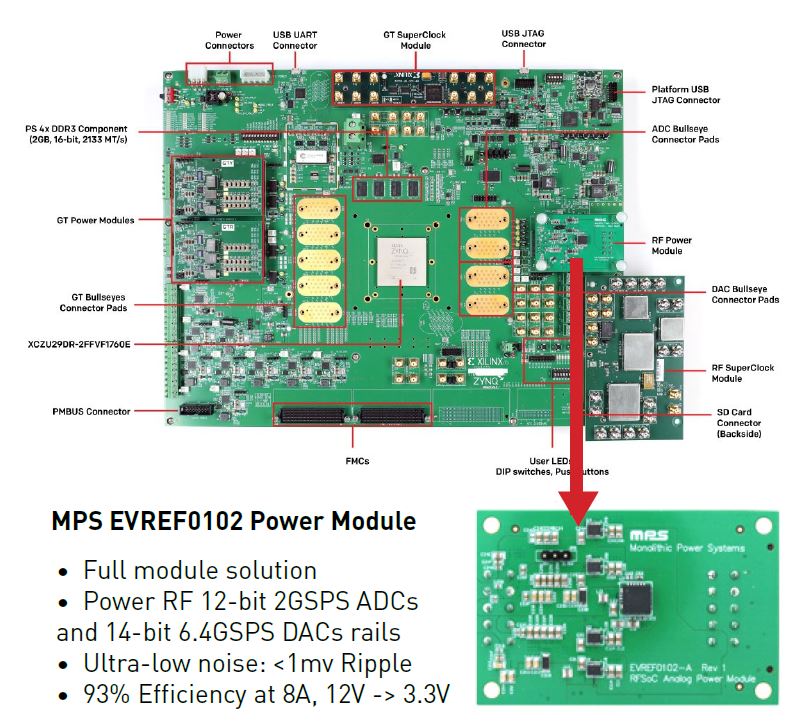

AMD Xilinx UltraScale+ RFSoCには、超低出力ノイズを必要とする高速A/Dコンバータ (ADC) およびD/Aコンバータ (DAC) が組み込まれています。スイッチモード電源 (SMPS) には、従来の低ドロップアウト (LDO) レギュレータと比較して効率が高いという利点があります。そのスイッチングの性質により、SMPSはそのスイッチング周波数とその高調波でノイズを放出します。MPSの電源モジュールソリューションは、2ステージCLCフィルタを活用して、敏感なADCおよびDACレールの出力電圧ノイズを最小限に抑えます。EVREF0102Aは、ZCU1275ZYNQ UltraScale+ RFSoC特性評価キット用に開発されたRFデータコンバータ電源モジュールです。 図7は、EVREF0102電源モジュールを示しています。

図7: EVRF0102 超低ノイズ電源モジュール

すべての高感度RFデータコンバータレールの出力電圧ノイズは1mV未満です。EVREF0102Aは、インダクタが集積された5つの高効率降圧スイッチモード電源モジュールを採用しています。 MPM3833Cは6V、3Aの超小型降圧電源モジュールであり、MPM3683-7は16V、8Aの電源モジュールです。両方の電源モジュールは、OCP、OVP、UVP、OTPなどが集積された保護機能を備えています。従来のLDOソリューションと比較して、EVREF0102Aは最大80%の効率改善を達成できます。EVREF0102Aアナログ電源モジュールは、強制連続導通モード (CCM) 動作を活用し、ポストパッシブフィルタを実装することにより、AMD Xilinx高速データコンバータの仕様を満たす超低ノイズも実現します。CLCパッシブフィルタは2つの最も感度の高いADCおよびDACレールに使用され、容量性フィルタは残りの電源レールに使用されます。参考のために付録を参照してください。

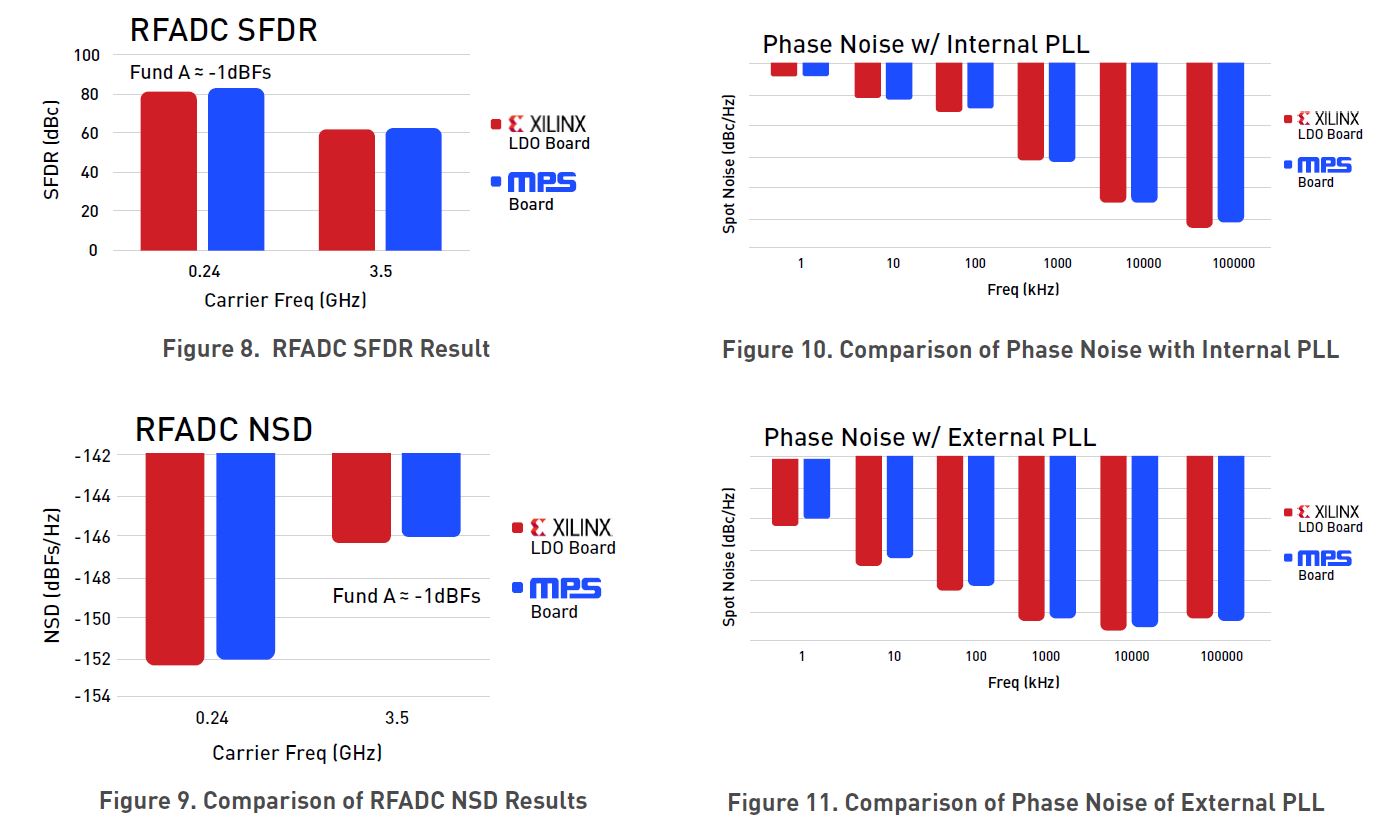

図8-11は、従来のLDOソリューションとMPS電源モジュールソリューションの比較を示しています。実験結果は、ZCU1275開発キットのAMD Xilinxラボで収集されました。図に示すように、MPS電源モジュールソリューションのノイズレベルは、従来のLDOソリューションに匹敵します。

結論

MPS電源モジュールは、AMD Xilinx FPGAに高効率、完全集積、およびコンパクトな電源ソリューションを提供します。この拡張可能な電源モジュールは、コアレールに用途の広いソリューションを提供します。従来のLDOを高感度RFデータコンバータの電源レール用の電源モジュールに置き換えることで、効率が大幅に向上します。完全に検証された性能を備えた2つのリファレンスデザインボードがMPSから入手できます。RFデータコンバータレールの出力電圧リップルを最小化するためのパッシブフィルタの設計手順は、このアプリケーションノートの付録に概説されています。

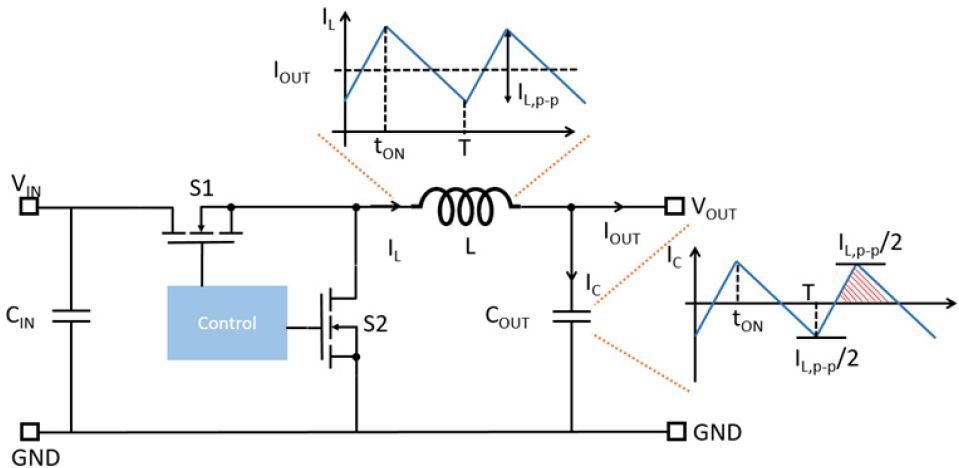

付録: 2段階フィルタ設計

同期バックコンバータは、入力コンデンサ (CIN) 、ボディダイオードを備えた2つのスイッチ (S1およびS2) 、エネルギー貯蔵パワーインダクタ (L) 、および出力コンデンサ (COUT) で構成されています。入力ソースは、S1がオンでS2がオフのときに、パワーインダクタLと負荷にエネルギーを供給します。この間、インダクタ電流が上昇します。インダクタに蓄積されたエネルギーは、S2がオンでS1がオフのときに出力コンデンサと負荷に伝達され、インダクタ電流が低下します。降圧レギュレータのスイッチング動作により、出力電圧が変動します。出力コンデンサCOUTは、定常状態で出力電圧を平滑化するために出力に配置されます。出力コンデンサは、高周波電圧成分がグランドに戻るための低インピーダンス経路を提供することにより、出力電圧リップルを低減します。

図1: 低ノイズフィルタの設計

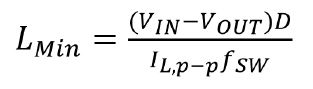

その後の開発では、出力電圧リップルを最小化するために、降圧コンバータが連続導通モード (CCM) で動作すると想定されています。Lのインダクタンスは、インダクタ電流リップル要件を満たすように設計されています。Lの最小インダクタンスは次のように決定されます。

ここで、VINとVOUTはそれぞれ入力電圧と出力電圧を表し、D = VOUT / VINはデューティ比を表し、I_ (L,p-p) はインダクタのピークツーピーク電流リップルを表し、fSWはコンバータのスイッチング周波数を表します。通常、ピークツーピークインダクタ電流のリップルは、出力DC電流の20?40%として選択されます。

出力容量は、出力リップルが指定されたピークツーピーク値を下回るように選択されます。単段容量性フィルタの場合、1mV?2mVの最小出力電圧リップルを実現できます。

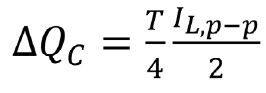

定常状態では、コンデンサに供給される正味の電荷は、1つのスイッチング期間内でゼロになります。図1の影付きの領域のコンデンサの電荷は次のように計算されます。

ここで、Tは1つのスイッチングサイクルの周期です。定義上、特定の期間のコンデンサの電荷は次のように表すこともできます。

(3)

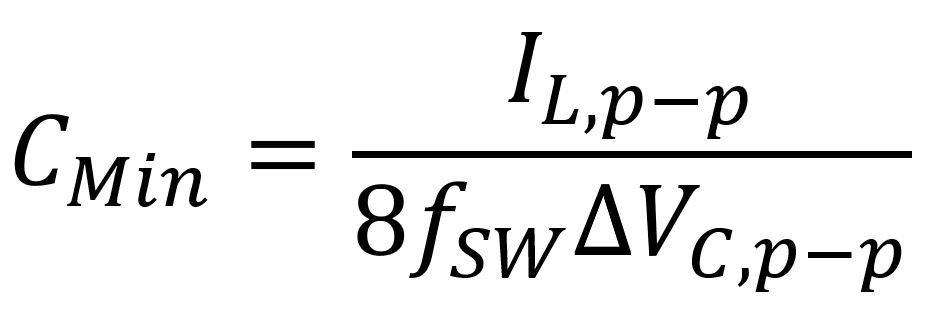

式 (2) および (3) の場合、必要な出力ピークツーピーク電圧リップル (VOUTp-p) を達成するための最小容量は次のように決定されます。

理想的には、より多くの出力コンデンサを並列接続することにより、ノイズシャント機能を向上させることができます。実際の使用では、出力コンデンサはPCB上に横方向に配置されます。PCBに出力コンデンサを追加すると、シャントパスに寄生インダクタンスとAC抵抗が追加され、スイッチングノイズをバイパスする効果が低下します。

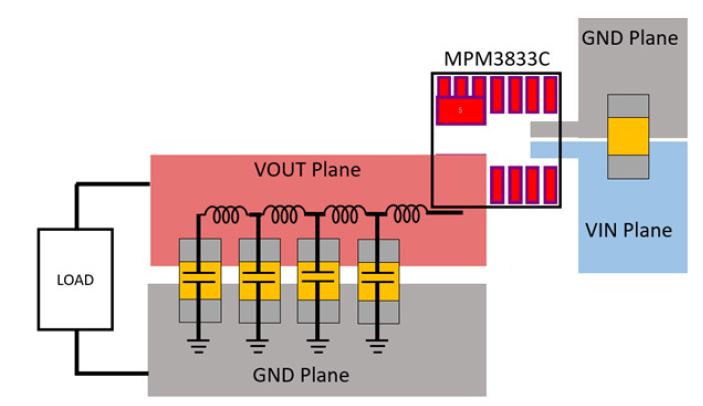

最適化されたインダクタを集積して電力変換器の設計を簡素化するMPS電力モジュールの典型的なPCBレイアウトを図2に示します。MPM3833CのPCBレイアウトでは、電力損失を最小限に抑えるために、出力電力パスに幅の広い銅面が使用されています。出力コンデンサは、出力電流経路に沿って配置されます。図に示すように、出力プレーンに配置されるコンデンサが増えると、追加のコンデンサから電源モジュールの出力ピンまでの距離が長くなります。その結果、電源モジュールから離れた出力コンデンサには、より多くの寄生インダクタンスが含まれます。出力容量を追加すると効果が低下し、最終的にはシャントループが寄生インダクタンスによって支配されます。

図2: MPM3833C電源モジュールの一般的なPCBレイアウト

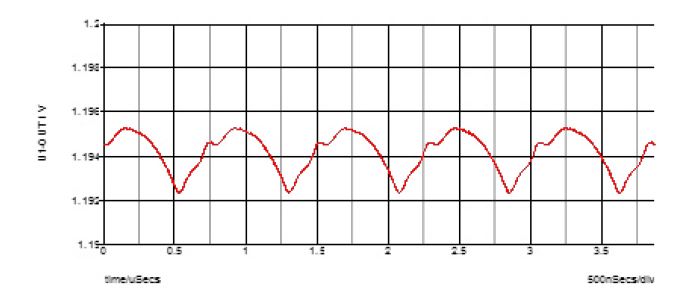

ループ寄生インダクタンスの影響を示すために、さまざまな出力コンデンサを備えたMPM3833CをSimplisを使用してシミュレーションします。追加の出力コンデンサごとに、バイパスループに追加の0.5nHの寄生インダクタンスが導入されると想定されています。 図3は、1つの22uFコンデンサを備えた電源モジュールの出力リップルを示しています。バイパスコンデンサは、5V入力、1.2V出力、および2A負荷で出力リップルを約3mVに効果的に低減します。

図3: 22uF出力コンデンサを1つ備えたMPM3833Cの出力電圧リップル

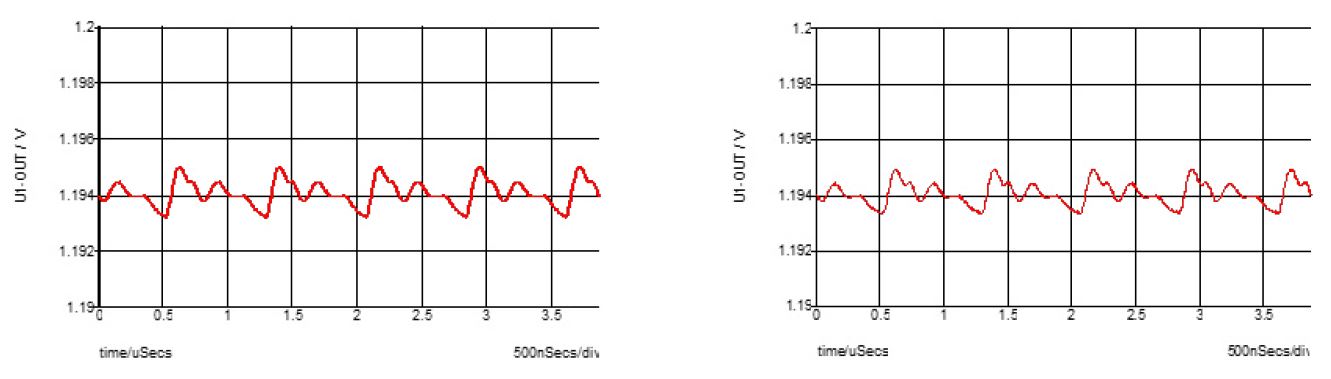

出力電圧リップルをさらに低減するために、1つの追加の22uF出力コンデンサが出力に配置されます。新しいコンデンサは電源モジュールから離れた場所に配置する必要があるため、新しいコンデンサに関連する寄生インダクタンスは1nHです。シミュレートされた出力電圧リップルを図4 (a) に示します。ここでは、出力電圧リップルが2mVに減少しています。1つの22uF出力コンデンサが出力電圧リップルを3mVに効果的に下げる図3に示す波形と比較すると、追加の22uFコンデンサはあまり効果的ではありません。図4 (b) は、もう1つの22μFコンデンサ (合計4 x 2μF) を使用した場合の出力電圧リップルを示しています。最後の22μFコンデンサは、バイパスループに1.5nHの寄生インダクタンスを含みます。図に示すように、追加の22μFコンデンサによって達成される出力リップルの低減は、3 x 22μFを使用した場合と比較して5%未満です。

図4 (a) 4 x 22uF出力コンデンサと (b) 5 x 22uF出力コンデンサを備えたMPM3833Cの出力電圧リップル

図3と図4に示すように、PCBに配置される出力コンデンサが増えると、PCBの銅 / トレースによって導入される寄生インダクタンスが支配的になります。最終的に、コンデンサを追加する利点は、ループに追加される寄生インダクタンスによって打ち消されます。

第2段階のフィルタ設計

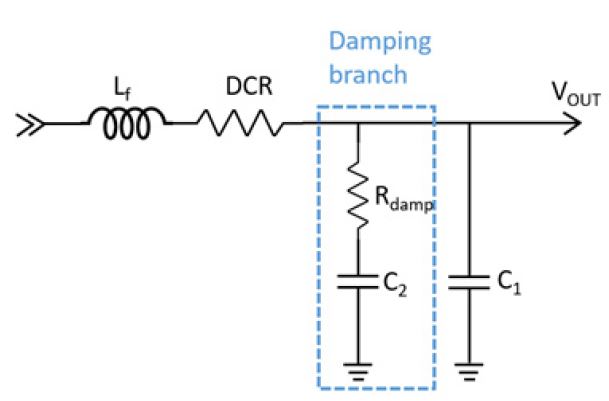

通常、シャント出力コンデンサは、出力電圧リップルを1mVに効果的に低減できます。このポイントを超えるには、出力電圧リップルを小さくするために第2ステージの出力フィルタが必要になります (1mV未満の電圧リップルを実現できます) 。図5は、第1段の出力コンデンサにカスケード接続された第2段のLCフィルタを示しています。第2ステージのフィルタは、1つのフィルタインダクタとその直列抵抗DCR、バイパスコンデンサブランチ、およびダンピングブランチで構成されています。LCフィルタは、出力に高インピーダンスを生成することによって機能します。フィルタリングインダクタLf は、目的の高周波範囲で抵抗性であり、熱の形でノイズエネルギーを放散します。インダクタは追加のシャントコンデンサと組み合わされて、ローパスLCフィルタネットワークを形成します。

図5: 並列ダンピングブランチを備えた第2ステージLCフィルタ

第2ステージのフィルタは、適切に設計されている場合、出力電圧ノイズを低減するのに非常に効果的です。目的の周波数帯域に合わせて、第2ステージLCフィルタのコンポーネントのサイズを決定することが重要です。設計手順の最初のステップでは、式 (4) に基づいて第1段の出力コンデンサを選択します。5mV~10mVの出力電圧リップルは、第1段階の設計では一般的です。通常、10~22uFのコンデンサで十分です。システムの安定性を確保するには、第1ステージのコンデンサCOUTを第2ステージのバイパスコンデンサC1よりも小さくする必要があります。

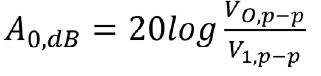

第1ステージのコンデンサCOUTが決定され、指定された出力電圧リップル (特定の周波数で) が与えられると、第2ステージのLCフィルタの必要な減衰は次のように決定できます。

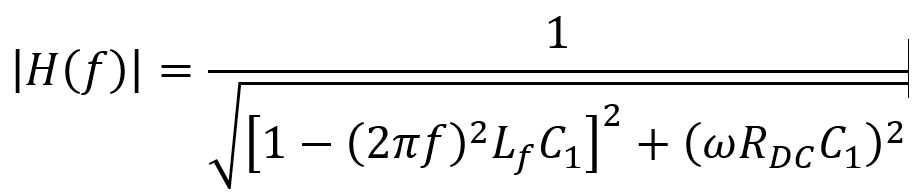

ここで、V1,p-pは出力コンデンサでのピークツーピーク電圧リップルを表し、V0,p-pは (第2ステージフィルタ後の) ピークツーピーク出力電圧を表します。フェーザ分析を使用して、LCフィルタのゲインの振幅は次のように決定されます。

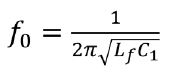

大きな直列抵抗で構成されるダンピングブランチのインピーダンスは、スイッチング周波数でのバイパスブランチよりもはるかに大きいことに注意してください。したがって、図5に示すフィルタは、2次RLCフィルタとして近似されます。フィルタのカットオフ周波数は次のように決定されます。

通常、0.22μHから1μHのインダクタンスを持つインダクタを選択して、必要な出力リップルを実現できます。インダクタは、深刻な抵抗によって消費電力が増加し、出力電圧レギュレーションが低下するため、DCRが最小になるように選択する必要があります。DC電流が増加すると、インダクタのコア材料が飽和し、インダクタのインダクタンスが減少することに注意してください。定格DC電流でインダクタンスが十分に高くなるように注意する必要があります。

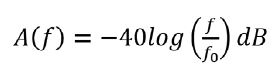

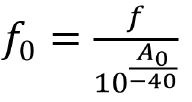

フィルタリングインダクタを選択すると、そのDCRをデータシートから抽出できます。2次フィルタである第2ステージLCフィルタは、カットオフ周波数により10年ごとに40dbのロールオフを与えます。特定の周波数での減衰は、次のように見積もることができます。

式(5)で計算された減衰を使用して、必要なカットオフ周波数は次のように決定されます。

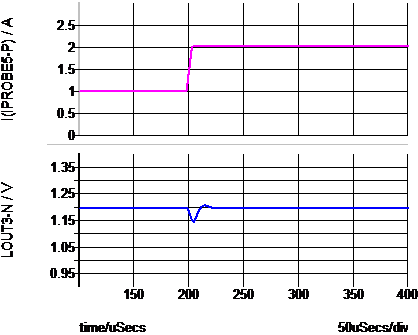

続いて、必要なバイパス容量C1は次のように決定されます。

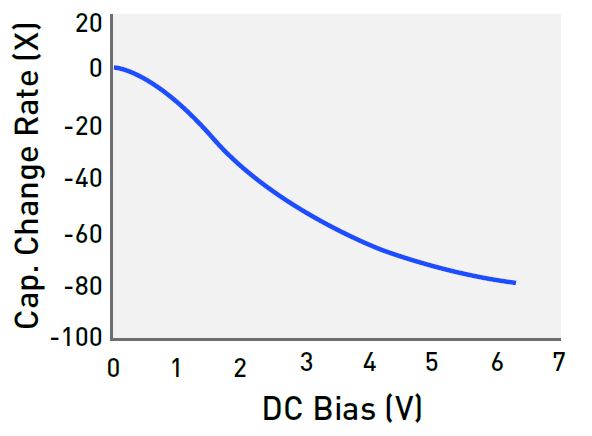

低ESRおよびESLのバイパスコンデンサとしてセラミックコンデンサを使用する必要があります。セラミックコンデンサの静電容量は、DCバイアス電圧で大幅なディレーティングが発生することに注意してください。 図6は、定格6.3Vのムラタ0805セラミックコンデンサのDCディレーティング曲線を示しています。図に示すように、最大定格DCバイアス電圧では、静電容量は公称値の20%に低下します。バイパスコンデンサは、ディレーティングを考慮して、公称DCバイアス電圧で選択する必要があります。

図6: DCバイアスブランチでの典型的なセラミックコンデンサのディレーティング曲線

ダンピング

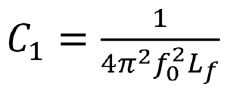

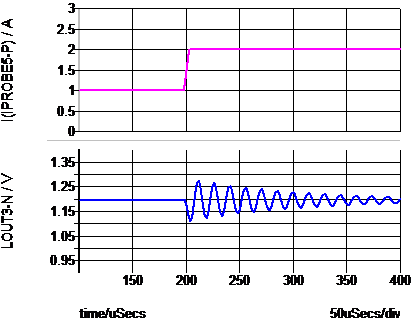

第2ステージのLCフィルタは、適切に減衰されていない場合、共振ピーキングを引き起こす可能性があります。フィルタリングインダクタとバイパスコンデンサ間の共振により、出力リップルが増幅され、負荷過渡時に望ましくないリンギングが発生する可能性があります。 図7 (a) は、第2段LCフィルタを備えたアンダーダンプコンバータシステムの出力電圧を示しています。最初、システムは定常状態で動作します。t =200μSで、1Aから2Aへの負荷過渡が開始され、出力電圧の振動が始まります。 図7 (b) は、過減衰第2段フィルタの負荷過渡時の出力電圧と電流を示しています。負荷過渡時の望ましくないリンギングを回避するには、第2段階のLCフィルタの共振を適切に減衰させる必要があります。ほとんどの設計では、制御の安定性の問題を回避するために、第2段階のフィルタは制御ループの外側に配置されます。したがって、ダンピングは受動部品 (追加のダンピング抵抗) によって実現する必要があります。

図7: (a) アンダーダンプLCフィルタと (b) オーバーダンプLCフィルタのステップ応答

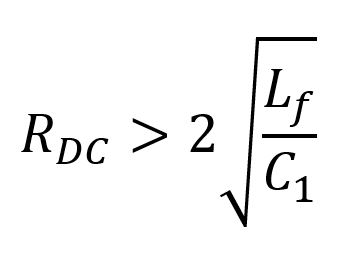

このDCRは、ネットワークにダンピングを与えます。ただし、直列RLC回路に十分なダンピングを提供するには、直列抵抗が

mps-xilinx-artcile-q1-2019-_1.pdf

_____________________________________

興味のある内容でしたか? お役に立つ情報をメールでお届けします。今すぐ登録を!

アカウントにログイン

新しいアカウントを作成