MOSFETの選択による電源効率の最適化

役立つ情報を毎月お届けします

プライバシーを尊重します

はじめに

電源を設計する場合は、効率のために設計を最適化することが常に重要です。効率の向上により、エネルギーが節約され、発熱が減少し、電源のサイズを縮小することさえできます。

本稿では、ハイサイドMOSFET (HS-FET) とローサイドMOSFET (LS-FET) の数の割合をどう選択して、電源設計の効率を向上するかについて説明します。

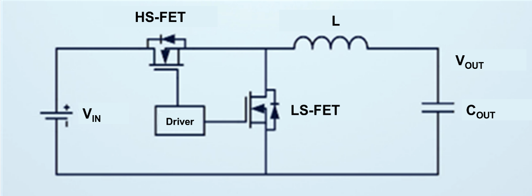

図1に、HS-FETとLS-FETを備えた簡略化回路を示します。

図1 : HS-FETとLS-FETを備えた回路

MOSFETを選択する際には、電力エンジニアは最適な効率を得るためにHS-FETとLS-FETの内部抵抗の分配で苦労する場合があります。

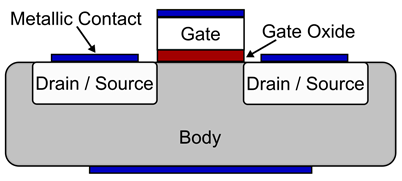

MOSFETの構造と損失の構成

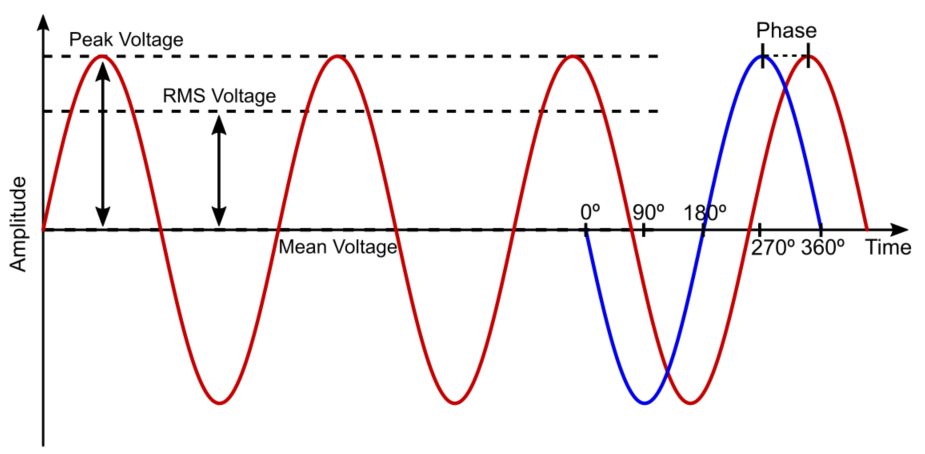

効率を考慮してMOSFETを選択する場合、設計者は伝導損失とスイッチング損失の間で最適化する必要があります。導通損失は、MOSFETが閉じているときに発生し、オン抵抗を流れる電流が原因です。スイッチング損失は、MOSFETをオン / オフするときに発生し、MOSFETがすぐにオン / オフに切り替わらないことにより生じます。これは、MOSFET内の半導体構造の容量性挙動が原因です。

MOSFETは、複数のMOSFETを並列に接続した半導体構造から成る統合された複数部品構造です。抵抗と静電容量の間には相反関係があります。並列に接続されたMOSFETの水晶の数が多いほど、オン抵抗 (RDS(ON)) は小さくなりますが、寄生容量は大きくなります。小さなRDS(ON)は伝導損失を減らしますが、寄生容量は増加し、スイッチング損失が増加します。

MOSFETの選択には十分な検討が必要であり、オンボードテストには多くの時間とリソースが必要になる場合があります。したがって、正確な数学的モデルを作成して損失を分析し、MOSFETの選択に役立てる方が有利です。

関連コンテンツ

伝導損失の計算

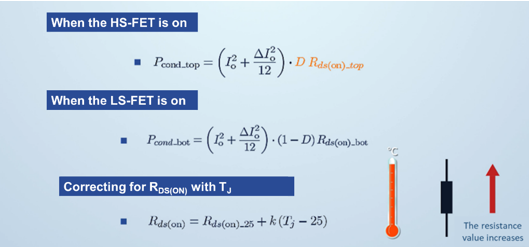

まず、伝導損失を計算します。これは比較的シンプルな計算です。1サイクルで、MOSFETに流れる電流とリップル電流を考慮して導通損失を計算できます。

正確を期すため、この計算を行うときのRDS(ON) と温度間の関係を考慮します。MOSFETの内部抵抗は固定値ではなく、温度が上昇すると増加します。

図2は、伝導損失の計算方法を示しています。ここで、IOは公称電流、 ΔIOは電流リップル振幅、TJは接合部温度、kは温度係数です。

図2 : 伝導損失の計算

スイッチング損失 (寄生)

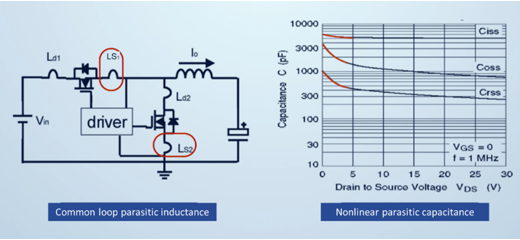

スイッチング損失の計算は難しい場合があります。この計算を行うときは、各ループのインダクタによって生じる寄生インダクタンスと、さまざまな電圧でのMOSFETの非線形寄生容量を考慮しましょう。

図3は、スイッチング損失を計算する際に考慮すべき2種類の寄生成分を示しています。

図3 : 2種類の寄生成分

スイッチング損失 (ターンオン損失)

ターンオン損失には、以下に説明する3つの段階があります。

- 段階1 (HS-FET段階) : HS-FETがオンになると、ドレイン・ソース間電圧 (VDS) が下がり始めます。対照的に、HS-FETのVDS(TOP) 電圧が0Vに低下するか、HS-FET電流 (IHS) が出力電流 (IOUT) に上昇するまで、ドレイン・ソース間電流は上昇します。

- 段階2 (逆回復段階) : 逆回復中、ITOPは、ピーク値に達し、LS-FETでは電圧は増大し始めます。

- 段階3 (発振段階) : IHS変動しなくなると発振が終了します。

図4に、ターンオン損失に関連するスイッチング損失を示します。

図4 : ターンオン損失

スイッチング損失 (ターンオフ損失)

ターンオフ損失には、以下に説明する2つの段階があります。

段階1 (DS電圧上昇) : VDSが上昇するとIDSが低下します。この段階ではIDSが0Aまで下がります。

段階2 (発振) : VDSが発振を停止するまで発振は続きます。

図5にターンオフ損失を示します。

図5 : ターンオフ損失

数理モデルと分析的検証

回路のさまざまな損失が分かったら、数理モデルを確立します。

- 必要な回路パラメータ値を設定します。MOSFETの値は、上記の式と非線形パラメータの補償値を使用して解析する必要があります。

- 定常状態での動作中に、コンバータの少なくとも1つのスイッチング期間にわたって過渡シミュレーションを実行します。

- 電圧波形と電流波形を積分して、MOSFETのスイッチング損失と導通損失を求めます。これは、電力プローブを使用するか、電流とVDS波形を乗算することによって実現できます。

モデルが利用可能になったら、上記の電力損失から取得したデータを使用してシミュレーションした効率を取得し、その値をボード (またはデータシート) から取得した効率曲線と比較します。計算の効率誤差が0.5%以内であれば、モデルは正確です (図6参照)。

図6 : 数理モデルの検証

数学的ツールに基づくMOSの選択

本稿では、総内部抵抗が100mΩである10個のMOSFETを使用し、モデルを使用してさまざまな割合での効率曲線を計算しました。たとえば、1:9の割合を考えてみましょう。これは、1つのHS-FET (高RDS(ON)、低静電容量) および9個のLS-FET (低RDS(ON)、低静電容量) があることを意味します。

曲線を比較することにより、3:7のMOSFETの割合が12V~3.3V、10Aアプリケーションに対して最適な仕様であると結論付けることができます (図7参照)。この効率曲線の集団は、MOSFETの数が同じであっても、割合が異なると効率曲線が異なることを示しています。効率曲線を最適化するための最適な割合を見つけましょう。

図7 : 最適なMOSFET割合

図9は、入力と出力の仕様が同じで出力電流が同じ場合、異なるMOSFET割合での回路の最小損失点をどう見つけるかを示しています。そのため、設計者はMOSFET割合を選択する際にこれらの仕様を念頭に置く必要があります。

図9 : 最適効率の比較

結論

MOSFETの選択は回路効率にとって重要であり、正確な数学的モデルによってMOSFETトランジスタの選択と設計が簡素化されます。正確なモデルを得るには、回路の寄生パラメータを考慮し、効率曲線を使用して結果を検証します。

本稿では、正確な数学的モデリングを通じて適切なHS-FETとLS-FETの割合を選択し、電源の効率を最適化する方法を紹介しました。詳細なMPSのMOSFETドライバと電源ソリューションの情報はオンラインで見つけることができます。

_______________________

興味のある内容でしたか? お役に立つ情報をメールでお届けします。今すぐ登録を!

アカウントにログイン

新しいアカウントを作成