5Gアプリケーション用電力供給ネットワークでの静電容量の最適化

役立つ情報を毎月お届けします

プライバシーを尊重します

はじめに

5Gアプリケーション用の電源システムを設計する場合、設計者は、そのようなアプリケーションに固有の周波数の広い幅である、電圧レギュレータの中域周波数からFPGAコアの高域クロック周波数まで考慮する必要があります。このエンドツーエンドの全二重設計は、電源、電力変換、配電プロセスのパフォーマンスを最適化する上で非常に重要です。

本稿では、効率的な電力供給ネットワーク (PDN) 設計を達成する方法に焦点を当てます。PDNは、電源およびグランドプレーンのレイアウト、受動素子、IC、および主電源レールに接続または結合されているその他の銅部品を含む、電圧およびグランドレールに接続されているすべての部品で構成されます。PDN内の規制要素の動作は、システム全体の動作に影響を与えるため、設計プロセス中に考慮する必要があります。

バイパスコンデンサとデカップリングコンデンサは、PDNの重要な部品です。容量が不十分だとシステムが不安定になり、パフォーマンスの問題が発生する場合があるため、PDN設計におけるコンデンサの選択と配置には特別な考慮が必要です。

デカップリングコンデンサとバイパスコンデンサの重要性

バイパスコンデンサは電圧レギュレータモジュール (VRM)で使用され、入力リップル電流をフィルタリングすることにより、コンバータに低インピーダンスの電圧源を提供します。また、電源とICグランド接続の結合によるスイッチングノイズによって生成される潜在的なグランドバウンス電圧も補償します。

降圧電圧レギュレータの出力において、デカップリングコンデンサの主な目的は、出力電圧リップル (∆VOUT) を低減することにより、出力電圧 (VOUT) を保証します。したがって、静電容量は、コンバータの負荷が突然変化することで引き起こされる電圧変動の制限も考慮に入れながら、負荷入力仕様によって設定された振幅に∆VOUTを制限するように選択されます。

バイパスコンデンサの配置戦略

バイパスコンデンサは信頼できる降圧コンバータ動作を確実にするために最も重要な要素です。ICを配置した後、バイパスコンデンサはレイアウトに最初に配置される部品であり、ICの配置直後に配線する必要があります。コンバータのスイッチングと組み合わされた不適切な配線による余分な寄生インダクタンスにより、過剰な電圧スパイクが発生し、ICの故障につながる可能性があります。

図1は、MPQ8655、ポイントオブロード (PoL) コンバータ用のバイパスコンデンサ (CI21およびCI26) の最適な配置を示しています。

図1 : MPQ8655用のバイパスコンデンサの配置

バイパスコンデンサ ループに生じる寄生インダクタンスは、コンデンサの寄生インダクタンスと、インダクタとIC間の電流経路レイアウトによって生成されるインダクタンスの2つの部分に分けることができます。PCBレイアウトの形状によって生成されるインダクタンスは、固有のコンデンサインダクタンスよりも全インダクタンスに対して重要であるため、ここに設計の重点を置く必要があります。ループインダクタンスを最小限に抑えるには、バイパスコンデンサをできるだけICの近くに配置する必要があります。また、コンデンサのパッドをできるだけICピンに近い電源 (PWR) およびグランド (GND) ネットに直接接続するためにビアホールを使用する必要があります。これにより、電流経路が最小限に抑えられます。

デカップリングコンデンサの選択

デカップリングコンデンサの必要なタイプと数は、周波数領域でのコンデンサの動作によって異なります。デカップリングコンデンサは、コンバータのスイッチング動作によって生成され、VRMの∆VOUTを最小限に抑え、電源が応答できるまで高周波でFPGA / ASICに瞬時電流を供給するよう設計されています。その結果、動作周波数スペクトル全体を考慮する必要があります。

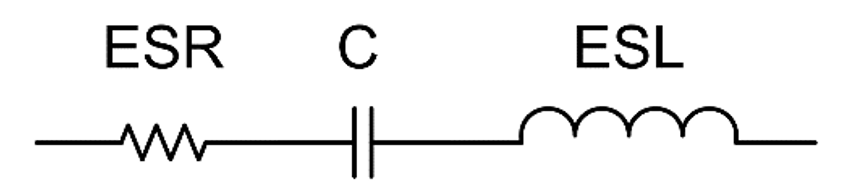

基本的なコンデンサモデルには、静電容量 (C)、等価直列抵抗 (ESR)、および等価直列インダクタンス (ESL) という3つの重要な要素が含まれています (図2参照)。

図2 : コンデンサの等価回路モデル

ESRは部品内の導電要素のインピーダンスによって発生し、共振周波数での最小インピーダンスを決定します。ESLはコンデンサに流れる電流の影響で発生し、共振周波数を決定します。共振周波数は、コンデンサのインピーダンスプロファイルにおいて、部品がインダクタのように動作し始め、周波数に比例してインピーダンスが増加するポイントです。

低周波数 (最大50kHz) で、降圧コンバータ は低インピーダンスです。しかし、高周波における降圧コンバータのインピーダンスは主に誘導性です。PCBに追加された各コンデンサは、特定の周波数でPDNインピーダンスを低減します。つまり、正確な配置と選択により、設定されたターゲットインピーダンスのプロファイルを実現できるようになります。したがって、検出ポイントから測定することにより、特定の周波数でのターゲットインピーダンスを実現できます。

ターゲットインピーダンス (ZTARGET) は式 (1) で計算できます。

$$Z_{TARGET}=\frac {∆V_{NOISE}}{I_{TRANSIENT\_MAX}}$$ここで、∆VNOISEは最大許容リップル電圧、ITRANSIENT_MAXは コンバータが提供する必要がある最大負荷ステップです。必要な入力と出力容量も計算できます。

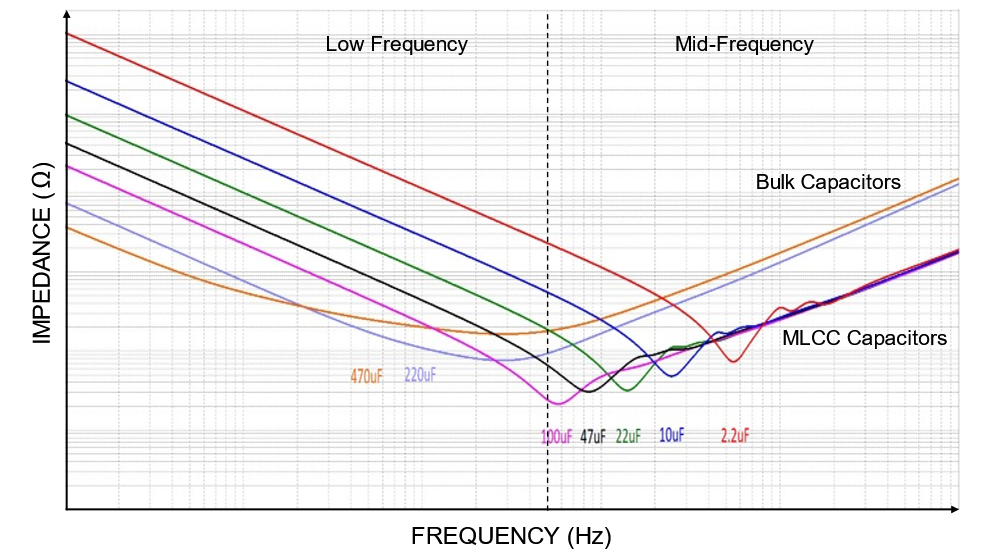

インピーダンスを目標レベル以下に維持するには、設計を制約し、寄生インダクタンスを低減する必要があります。バルクコンデンサは最大10MHzの周波数幅内のインピーダンスを下げますが、MLCCコンデンサは中高周波数幅内のインピーダンスを下げます。

図3は、バルクコンデンサとMLCCコンデンサのインピーダンス周波数特性を示します。

図3 : 代表的なバルクコンデンサおよびMLCCコンデンサのインピーダンス周波数特性

デカップリングコンデンサの配置戦略

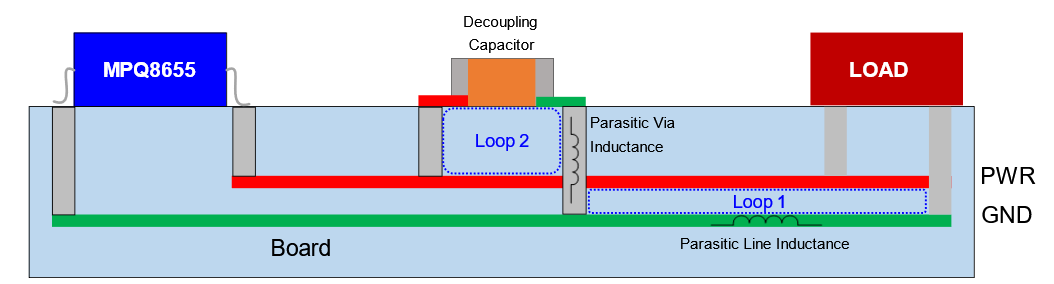

静電容量が計算され分析されると、PCB内のデカップリングコンデンサの最適な配置が重要になります。レイアウトの形状、ビアの配置、距離は主に電源プレーンのループインダクタンスに影響し、PDN応答に影響します。図4は、コンバータ、デカップリングコンデンサ、および負荷によって生成される電流ループを示しています。これらのループは構造的に固有のものであり避けられないため、これらのループをできるだけ最小限に抑えることが重要です。

図4 : レイアウト形状、距離、ビアによるデカップリング コンデンサのループインダクタンス

ループ1は水平方向のループ部品であり、コンバータ (MPQ8655) とデカップリングコンデンサ間の距離によって決まります。ループ2は垂直方向のループ部品であり、コンデンサを電源プレーンに接続するビアの高さによって決まります。電源プレーンは通常、PCBの一番奥の層に配置されます。

テストボードは、ASIC / FPGA電源レールの一般的な値である0.9VのVOUTと50Aの最大出力電流 (IOUT_MAX) をもつデュアルフェーズ動作で2つのMPQ8655デバイスを使用します。テストボードを使用してさまざまなシナリオのシミュレーションを実行し、コンデンサの最適な配置を決定できます。

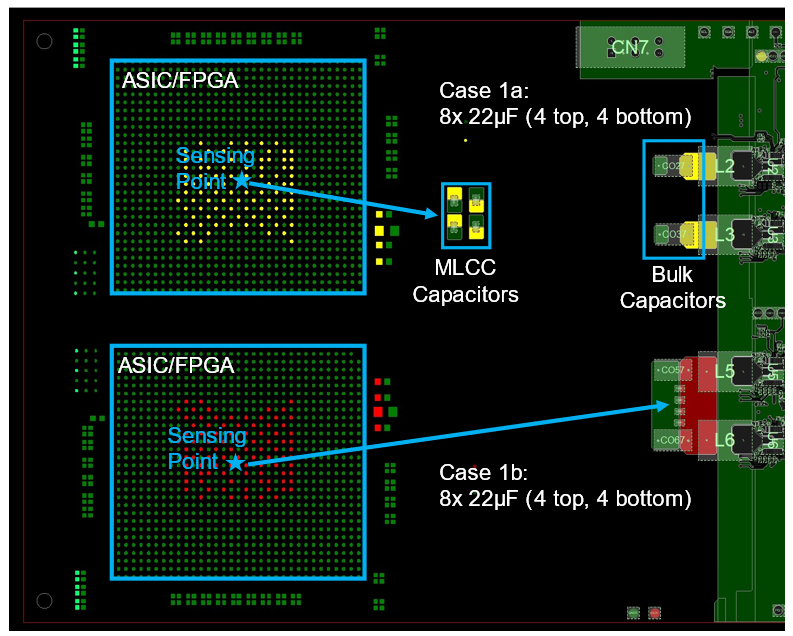

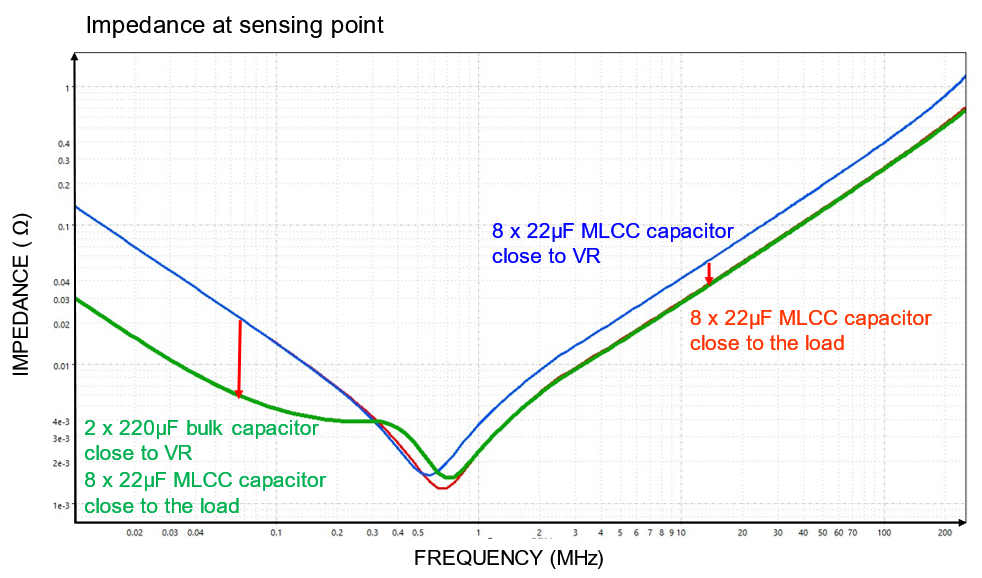

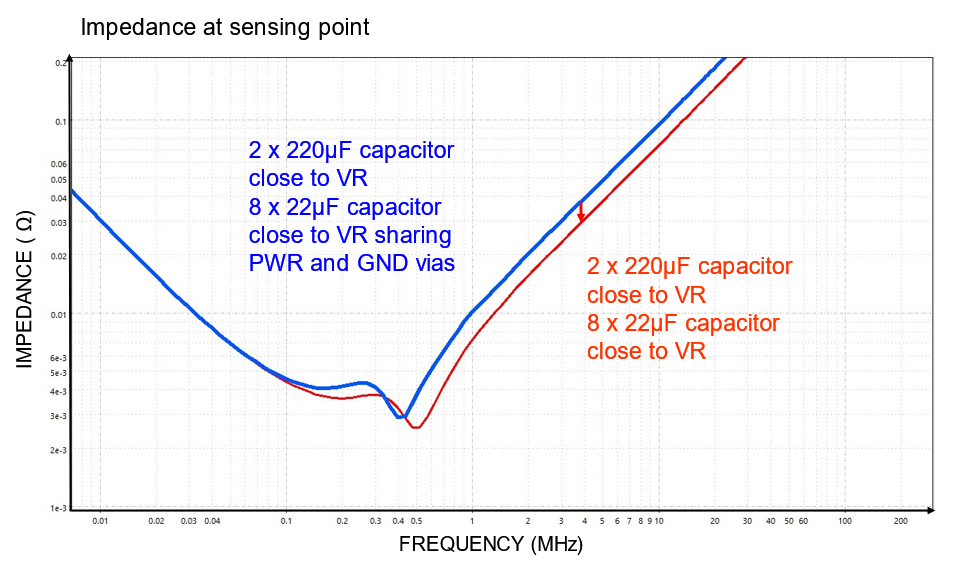

最適なコンデンサの配置を評価するために、ASIC / FPGAセンター内のボードレベルの検知ポイントでインピーダンスが測定されます。式 (1) の解析を使用すると、VRMインピーダンスプロファイルは8 x 22μFのMLCCコンデンサと2 x 220μFのバルクコンデンサを使用して実現できます。電圧レギュレータの安定性を維持するために、バルクコンデンサは出力インダクタの直後に配置されます。テストボードでは、ケース1aおよびケース1bでの22μFのMLCCコンデンサの異なる配置を検討します (図5参照)。

図5 : デカップリングコンデンサの配置

ケース1aでは、MLCCコンデンサがASIC / FPGAの直前に配置され、ループ1のサイズが削減されます。ケース1bでは、MLCCコンデンサがバルクコンデンサの隣に配置されるため、ケース1aと比較して、MLCCコンデンサと検知ポイント間の距離が2倍になります。

図6は、降圧コンバータの近くにバルクコンデンサを配置した場合のシミュレーション結果を示しています。これにより、低周波数幅 (緑色のトレース) のインピーダンスが低下します。MLCCコンデンサを負荷 (赤いトレース) の近くに配置すると、高周波幅のインピーダンスが低下し、コンデンサがFPGA / ASIC 負荷に必要な瞬時電流ステップをより効果的に供給できるようになります。

図6 : ループ1のサイズ変動に対するテスト結果 (デカップリングコンデンサの配置)

従来の設計ガイドラインは、基板スペースを削減して電力密度を高めるために、IC下のPCB底部にデカップリングコンデンサを配置することを推奨しています。ただし、コンデンサを基板の底部に配置すると、ASIC / FPGAが配置されている反対側に到達するために長いビアが必要になります。これにより、図4でループ2として示されている垂直経路のサイズが増加します。

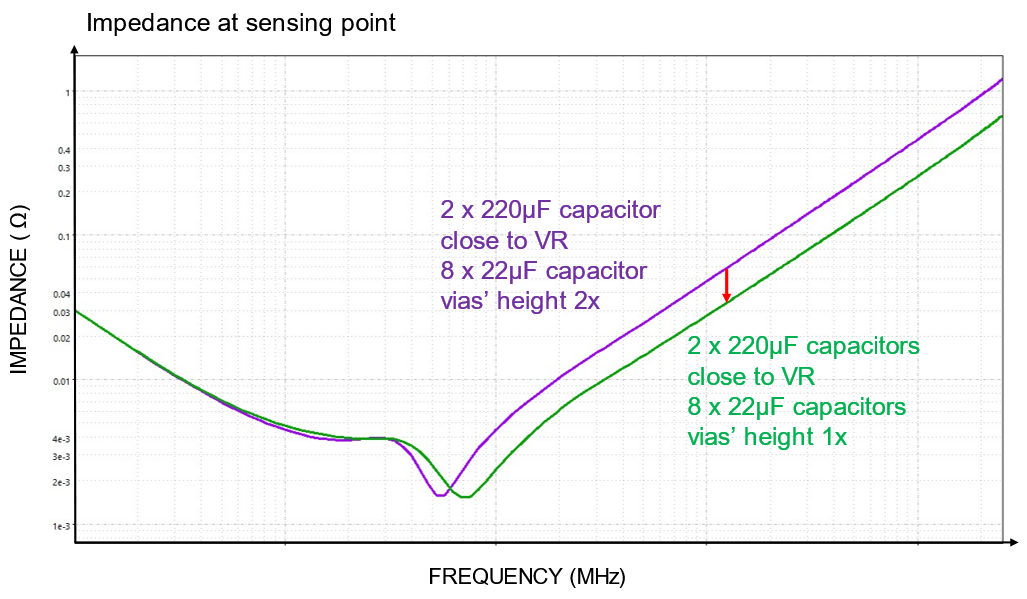

ループ2のサイズを大きくした場合の影響を分析するために、ビアの高さを2倍にして追加テストを実施しました。図7は、ループ2のサイズの変動に対するテスト結果を示しています。同様の傾向が観察され、ビアの高さが増加すると、中周波数から高周波数範囲のインピーダンスが増加します。

図7 : ループ2のサイズ変動に対するテスト結果 (ビアの高さの増加)

デカップリングコンデンサのループインダクタンスを最小限に抑えることは、コンデンサの量と同様に重要です。ループインダクタンスを低減するには2つの方法があります。1つ目は、ICとコンデンサ間の水平方向の距離を短くする方法です。2番目の方法は、電源プレーンとグランドプレーンを上層に配置してビアの高さを減らすことです。

基板スペースを削減するために複数の部品を狭い領域に配置すると、多くの場合、コンデンサがビアを共有することになります。コンデンサがビアを共有する場合、ビアの配置と数量を考慮しないと、コンデンサの適切な選択と配置による全体的な改善効果は大幅に減少するか、無視できる場合さえあります。したがって、ビアのレイアウト設計もループインピーダンスを低減するための鍵となります。

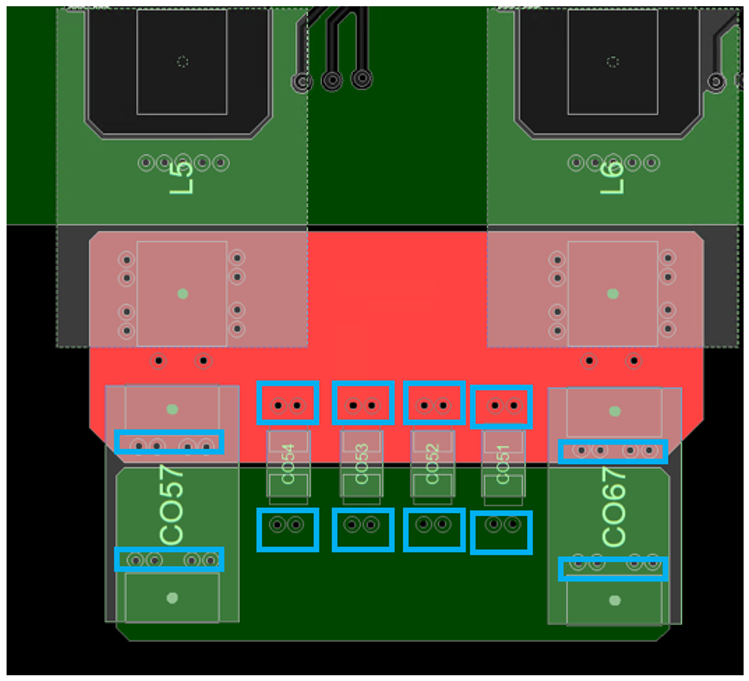

ビアの位置と数量の影響を分析するために、2つの一般的な設計推奨事項の基板ビア配置を使用して2回目のテストが実施されました。最初のセットアップでは、各コンデンサに電源プレーンとグランドプレーンへの独自のビアセットがあります (図8参照)。

図8 : 最適なコンデンサビア配置

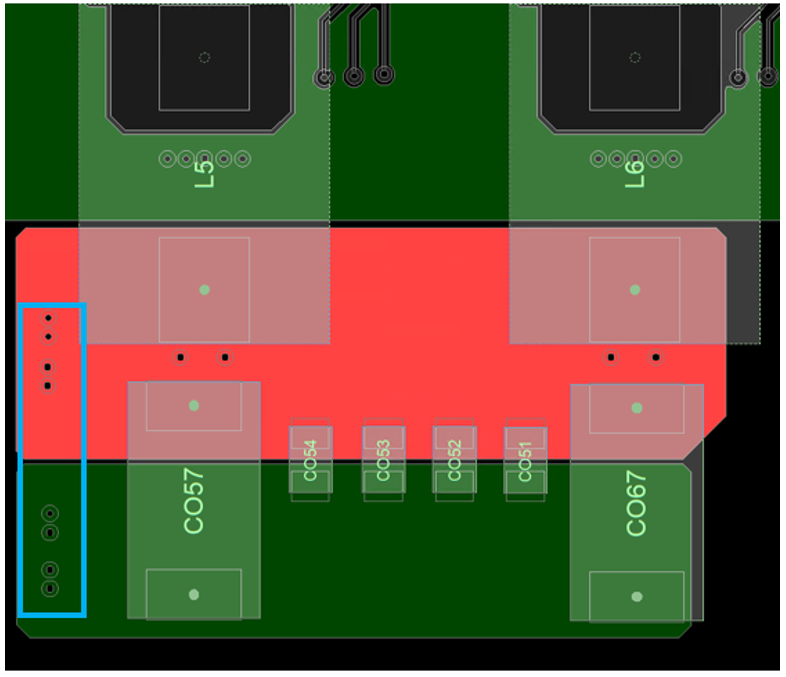

2番目のセットアップでは、すべてのコンデンサがプレーンの片側に配置されたビア一式を共有します (図9参照)。

図9 : 複数のコンデンサ間でのビア共有

図10は、ビア配置の変動に対するテスト結果を示しています。ビアをコンデンサから離して配置すると、ループ1のサイズが大きくなり、ループインダクタンスが増加します。したがって、ビアを共有すると高周波インピーダンスが増加します。

図10 : ビアの配置変動に対するテスト結果

その後のテストから、0805パッケージと0603パッケージの両方で、バルクコンデンサには少なくとも4つの電源ビアと4つのグランドビアを使用し、MLCCコンデンサには少なくとも2つの電源ビアと2つのグランドビアを使用することが推奨されています。ビアはコンデンサのできるだけ近くに配置する必要があります。

結論

FPGA / ASICシステムや、大電流と高速負荷過渡現象を必要とする回路を設計する場合、システムパフォーマンスを最適化するには PDN全体を考慮することが重要です。FPGAで見られるような高速ロードステップでは、回路全体に強力な高周波電流が発生します。このような高い周波数では、通常は無視できるPDN内の寄生要素によって、デバイスが突然誤動作する可能性があります。設計者は、PDNの寄生要素が最小限に抑えられるように注意する必要があります。

本稿では、MPQ8655を使ったVRMのデカップリングコンデンサの電流経路によって生じる寄生インピーダンスを低減することに焦点を当てました。最適なパフォーマンスを得るには、電流ループを垂直軸と水平軸の両方でできるだけ短く保つ必要があります。電流ループを負荷のできるだけ近くに配置し、電源配線を外層に残すことで、ビアの長さを効果的に短縮できます。ビアを適切に配置することも、寄生インダクタンスを低減する鍵となります。ビアの全寄生インダクタンスと各ビアを流れる電流を低減するために、複数のビアを各コンデンサのパッドのできるだけ近くに配置することをお勧めします。

5Gアプリケーション用の電力システムの安定性とパフォーマンスを向上するには、MPSの電源管理ソリューションの詳細をご覧ください。

_______________________

興味のある内容でしたか? お役に立つ情報をメールでお届けします。今すぐ登録を!

アカウントにログイン

新しいアカウントを作成