48V配電の2段階ソリューションを使用したデータセンターの電力密度と効率の向上

Qian Ouyang、Rohan Samsi、Jinghai Zhou

現在のデータセンターでは、通常12Vのバックプレーンと配電が基板上に用意されており、電圧を約1Vに変換する必要があります。これは通常、シングルフェーズまたはマルチフェーズの同期整流降圧レギュレータで実現されます。これらのデータセンターのラックは通常、最大20kWの電力定格になります。業界では、これらのデータセンターのサイズを縮小するために、ラックあたりの電力密度を約100kWに増やす必要があります。これは、48Vのバックプレーンと配電で実現できますが、このアプローチにはいくつか課題があります。ボードまで48Vを駆動するには、従来の同期整流降圧レギュレータは信頼できません。では、コストを増やすことなく、データセンターの密度をどのように高めるのでしょうか。本稿では、次世代のサーバー電力供給に役立つ柔軟で拡張可能な費用効果の高い方法で、48Vを負荷ポイント (POL、約1~5V) まで駆動する2段階のソリューションの概要を説明します。

提案

データセンターの需要が高まるにつれ、すべてのユーザーのニーズに対応するためにデータセンターのサイズと密度を増やす必要があります。重要な制限要因の1つは、ラックあたりのサーバーの約20kWという電力制限です。この制限は、最適ではない配電ネットワークが原因で発生します。ほとんどのミッドプレーンとバックプレーンは12Vで動作します。これには大量の銅線が必要であり、ラックあたりの電力が制限されます。オープンコンピュートプロジェクト (OCP) とGoogleは、動作電圧を48Vに上げ、それによってラックあたりの設置容量をラックあたり50~100kWに増やすアイデアを提案しました。このアーキテクチャがまだ成功していない主な理由の1つは、ダウンストリームソリューションの欠如です (48Vをプロセッサ、メモリバンク、その他ASICを含む基板に搭載されたPoLにいかに落とし込むか)。

48V入力のPOL分配問題に対処するために提案されたいくつかの異なるアプローチがあります。克服すべき主な課題には、拡張可能性、コスト、効率、およびサイズが含まれます。

スケーラビリティとコスト

レールに使用される小電流、2~5Vで数百ミリアンペアを消費するUSBやVBAポート、さらに1V近くで数百アンプを消費するプロセッサへのスケールアップを含む多様な負荷に対して48Vを配分するのは非常に困難です。いくつかの利用可能なソリューションには、中間バスを正確に調整し、最後の降圧にDC/DCコンバータを使用することにより、電圧を48Vから負荷電圧 (1~5V) に直接駆動することが含まれます。

これらのソリューションは大電流レールには効果的ですが、スケールダウンが難しく、大部分の低電流レールにはより高価であり、大電流レールでもさらに高価になる可能性があります。これらの問題を解決して、単純な同期整流降圧ソリューションを使用して直接変換を実行するために、窒化ガリウム (GaN) の使用などの他のソリューションが提案されています。コストと大量生産が実現可能になったときに非常に有望と考えられますが、現在、これらのソリューションはまだ実現には遠いようです。

効率とサイズ

基板のソリューションは、現在のサーバー基板に収まるように、高効率で小型サイズである必要があります。最新の変換効率は12Vから1Vへの変換で95%であるため、48Vから1Vへの変換の効率は少なくとも93%以上である必要があります。48Vから1Vへのコンバータのサイズは、業界標準のラックとバックプレーンに接続する平面ボードの寸法の制限により、12Vから1Vへのコンバータより大きくてはなりません。

ソリューション

ここで48Vから低電圧への配電のために提案するソリューションは、既存のデータセンターと比較して効率、拡張可能性、およびコストを改善する2段階のプロセスです。

第1段階

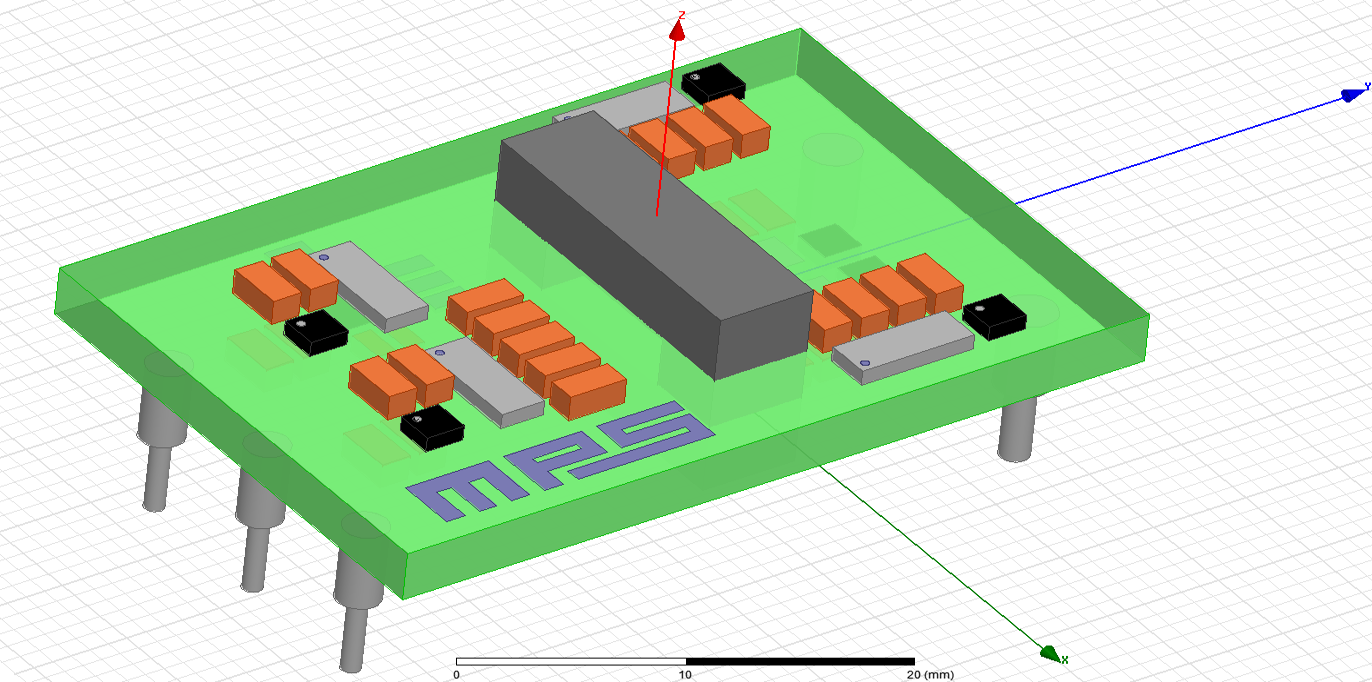

VINレール (48V) は基板全体に分配され、その後、可変の中間電圧 (通常は5~8V) に降圧されます。可変の5~8Vは、CPUとメモリの電力用にクラスタで生成できますが、残りの配電 (合計約50W) は別のコンバータから生成できます。中間フローティングレールは完全なソフトスイッチングを保証し、ハーフブリッジの共振LLCコンバータを使用することで98%のピーク効率を達成します。入力電圧が60V未満なので、絶縁は不要です。LLCネットワークの一部としてインダクタの代わりにトランスを使用することで、機能の分離をより簡単に実現できます。これは、48Vから5~8Vへの降圧にも役立ちます。基本的な考え方は、この第1段階のソリューションをモジュール化することです (図1を参照)。

図1: 第1段階モジュールの正面図

第1段階のモジュールは、供給される電力の関数として縮小できますが、一般的なシングルプロセッササーバーの場合、必要なモジュールは2つだけです。この第1段階のもう1つのユニークな機能は、マルチソース化できることです。GaNなどのテクノロジーが普及すると、ダウンストリームソリューションに影響を与えることなく、これらのモジュールをシームレスに置き換えることができます。可変の5~8Vの規制されていない電圧は、相互運用性が維持されるように、システム全体に影響を与えることなく、5~8Vの厳密に規制された電圧に置き換えることもできます。

第2段階

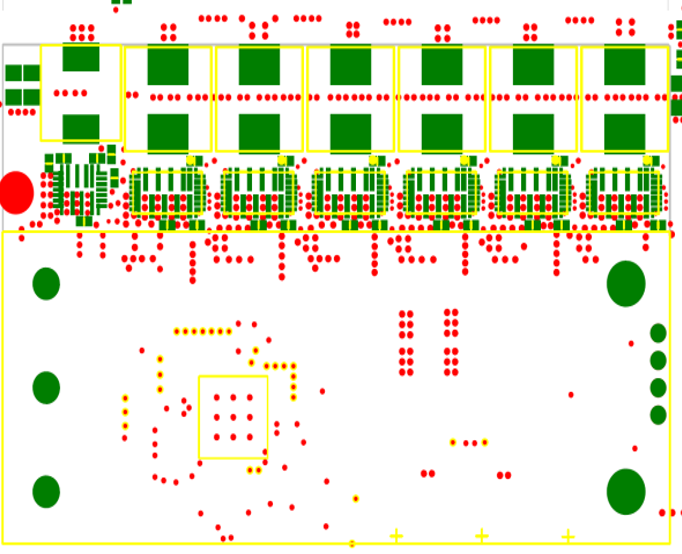

第2段階は、供給される電力に完全に依存します。ミリアンペア負荷の場合、第2段階は、リニア低ドロップアウト (LDO) レギュレータを使用するのと同じくらい簡単です。電力レベルが上がると、第2段階では、豊富にあるシングルフェーズ同期整流降圧レギュレータを利用できます。入力電圧の低下により、低デューティ比の必要性が減少し、電界効果トランジスタ (FET) と効率を最適化して、損失を低減できます。通常の12Vレールと比較すると、高耐圧FETの必要性を減らすことにより、ICのコストが削減され、効率、性能指数が向上します。プロセッサとメモリの高電流ソリューションには、インターリーブされたマルチフェーズレギュレータを使用できます (図2を参照)。

入力電圧を下げることで、これらのマルチフェーズコンバータは約97%のピーク効率を達成できます。これらのコンバータのほとんどでフィードフォワード制御が改善されているため、フローティング入力電圧 (5~8V、第1段階の出力) を簡単に処理できます。これらのコンバータのサイズは、より小さなインダクタとより少ないコンデンサを使用する高周波変換を使用することによって小さくなります。

図2: 第2段階

結論

このソリューションの全体的な効率は約95%であり、48Vから1Vへの変換の93%の目標を上回り、12Vから1Vへの最新式の変換効率と一致します。モジュールは垂直方向に取り付けることができるため、基板のサイズは大きくなりません。第2段階のサイズ縮小に続く利益は、第1段階のサイズの増加を相殺します。第2段階のコンバータを使用し、それに応じて第1段階のコンバータのサイズを縮小する柔軟性により、拡張可能性が向上します。このソリューションにより、データセンターはコストとサイズを増やすことなく、ラックあたり100kWの高密度を達成できます。

__________________________

アカウントにログイン

新しいアカウントを作成