過度の放熱を減らすための同期整流ソリューション設計 (第2部)

役立つ情報を毎月お届けします

プライバシーを尊重します

はじめに

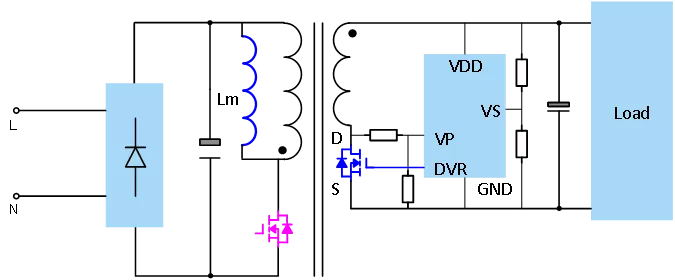

本稿は、超小型の高速充電アダプタ用の二次側同期整流を設計する方法を探る2部構成のシリーズの第2部です。第1部では、同期整流のトポロジー設計と電源について説明しました。第2部では、同期整流がどのように開閉するか、および新しいICがどのようにクイックシャットダウンテクノロジーを利用するかを確認します。

同期整流をオフにする

セルフパワー回路は、二次MOSFETを開くために必要な接続を提供します。設計者は、同期整流を開放するタイミングを考慮する必要があります。

第1部で最初に説明したMP9989は、連続導通モード (CCM) および不連続導通モード (DCM) 付きのフライバックの理想ダイオードです。一次側MOSFETがオフになると、二次側MOSFETはボディダイオードをフリーホイールで走らせ、正のVDSは-0.7Vに低下します。チップがこの電圧シフトを検出すると、二次MOSFETを開いて、電流が継続的に流れるようにします。

二次MOSFETの単純なプロセスと比較すると、間欠モードで動作しているときの無効電力供給には問題があります。図1に、間欠モードでのVDSと側方電流の波形を示します。電流が流れなくなると、MOSFETが閉じます。これに続いて、VDS電圧ショックが発生する可能性があります。特定の動作条件下では、VDSショックの大きさは比較的大きく、谷電圧は0Vに達することさえあります。二次側同期整流が誤ってMOSFETを開く可能性があり、その結果、連続的な電流が流れるために異常が発生します。

図1: 間欠モードでのVDSと側方電流波形

元のエッジMOSFETのシャットダウン中およびDCM中のVDS波形を観察すると、VDSは、通常のオープニングシーケンス中に変化するときよりも、発振するときの方がはるかにゆっくりと変化することがわかります。この違いに基づいて、MP9989には、内部クロックが開始したときとサイドVDSが2Vに低下したときのスルーレートが含まれています。VDSが30ns以内に-80mVに低下しない場合、異常信号が検出され、デバイスはオンになりません。これにより、偶発的な伝導による誤動作を招く信号を防ぎます。

同期整流の信頼性の高いシャットダウン

同期整流のシャットダウンプロセスには、さまざまな考慮事項が必要です。原則として、同期整流は、サイドMOSFETが閉じている間にエッジMOSFETが開いているときにシャットダウンします。ただし、サイドエッジ間に通信メカニズムがないため、サイドMOSFETがエッジMOSFETのリード通信信号に時間内に応答することは困難です。

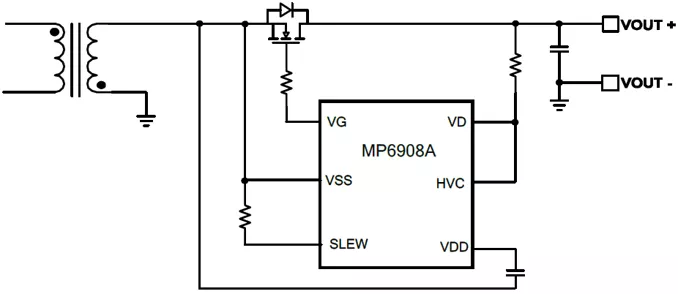

従来のアプローチでは、励起インダクタのボルト秒バランス方式を使用し、ICがシャットダウンするタイミングを計算します (図2を参照)。理論的には、シャットダウン時間はサイドMOSFETに基づいて計算され、サイドMOSFETをいつオフにするかを決定できます。

図2: 共通のボルト秒バランス方式

負荷が増加すると、それに応じて元のエッジ巻線の磁束が変化し、出力電圧が安定します。動的調整中は、ボルト秒バランスは無効です。したがって、二次MOSFETが設定時間内にシャットダウンしない場合、短絡が発生します。

さらに、ボルト秒バランスの原則は、トランスの励起インダクタンス電圧はICがオンおよびオフの間に測定されるべきであることを意味しています。寄生パラメータによって引き起こされる電圧サンプリング抵抗と電圧ショックの精度は、ボルトと秒のバランスを計算するときにエラーを引き起こす可能性があり、信頼性に大きな影響を与えます。

同期整流のシャットダウンプロセスの要点を以下に要約します。

- ボルトと秒のバランスは、定常状態の条件下でのみ確立される。これは、二次MOSFETが動的条件下でオフにならず、短絡が発生することが多いためです。

- ピーク電圧 (VP) サンプリングとVSサンプリングは、周辺抵抗の精度の影響を受け、計算エラーが発生する可能性がある。

- 寄生パラメータによって引き起こされる振動により、VPのサンプリングが不可能になり、計算エラーが発生する可能性があります。

クイックシャットダウン技術

クイックシャットダウン技術は、同期整流のMOSFETのゲート電圧を動的に調整します。たとえば、MP9989のMOSFETの開放遅延は、VDSが正から負の電圧に急速に低下したときに連続フローを開始します (図3を参照)。

図3: MP9989のVDS圧力降下により、MOSFETのオープン遅延が発生します

この間、サイドMOSFETには大きな連続電流が流れ、VDSは電流にオンインピーダンスを掛けたものに等しくなります。電流が流れ続けると、VDSは減少します (図4を参照)。

図4: MP9989のVDSは、大きな側の連続電流で減少します

VDSが40mVに達すると、MP9989はゲート駆動電圧を動的に低下させ、オンインピーダンスを増加させます。MP9989は、電流が低下し続けている間に40mVに低下するときにVDSを制御します (図5を参照)。この時点で、MOSFETは半分オンの状態になり、ゲート電圧は低くなります。

図5: MP9989のVDSの動的制御が40mVに低下

次のデューティサイクルでリアクティブエッジのMOSFETが開いている場合、二次MOSFETのチューブゲートを以前の低い電圧レベルからすばやくオフに切り替えることができます。これにより、信頼性の高い操作が保証されます。クイックシャットダウン技術の追加により、MPSの同期整流製品は600kHzのスイッチング周波数 (fSW) をサポートし、CCM、DCM、準共振、アクティブクランプ、およびその他の還流アプリケーションに適応できます。この製品には、MP9989およびMP6908Aが含まれます。

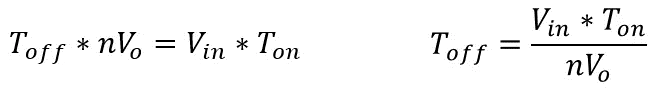

MP9989は、次の機能を提供します。

- 集積された100V / 10mΩ MOSFET

- ハイサイドまたはローサイド整流用の補助巻線は不必要

- 0Vまでの広い出力電圧 (VOUT) 範囲

- DCM中の誤ったターンオンを防ぐためのリンギング検出

- 110μA静止電流 (IQ)

- DCM、CCM、および準共振動作をサポート

図6に、MP9989の代表的なアプリケーションを示します。

図6: MP9989の代表的なアプリケーション図

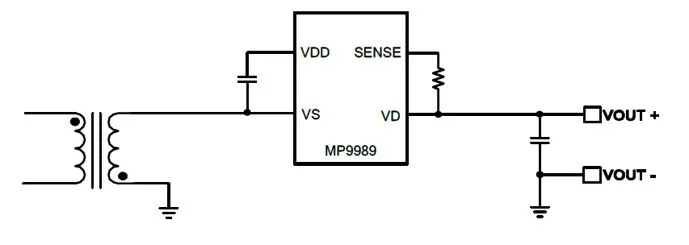

MP6908Aは、次の機能を提供します。

- 最大600kHzのfSW

- 30nsの高速ターンオフおよびターンオン遅延

- ハイサイドまたはローサイド整流用の補助巻線は不必要

- 0Vまでの広いVOUT範囲

- リンギング検出は、誤ったターンオンを防止

- 静止電流~100μAt

- アクティブクランプフライバックのDCM、CCM、および準共振動作をサポート

- TSOT23-6パッケージで提供

図7に、MP6908Aの代表的なアプリケーションを示します。

図7: MP6908Aの代表的なアプリケーション図

結論

本稿では、二次側の同期整流が開いたりシャットダウンしたりする時に役立つ戦略的な考慮事項について説明しました。また、MP9989を使用したクイックシャットダウン技術の有効性も確認しました。本稿の情報に基づいて、MOSFETを使用した二次側同期整流ソリューションは、標準的な同期整流ソリューションの主要な課題を克服して、超小型の高速充電ソリューションを作成できます。

_______________________

興味のある内容でしたか? お役に立つ情報をメールでお届けします。今すぐ登録を!

アカウントにログイン

新しいアカウントを作成