デジタルコントローラを使用したマルチフェーズ降圧型コンバータの設計

役立つ情報を毎月お届けします

プライバシーを尊重します

はじめに

ここ数十年の間に、サーバーおよびコンピューティングシステムの複雑さは、Power Delivery (PD) 要件とともに増大してきました。これは、より高い効率と高速の動的応答、および電力損失削減とMOSFETのサイズの間での妥協が必要になるため、レギュレータの設計をより困難にします。

サーバーには、高電流、低電圧、高速過渡応答をもつ電源が必要です。つまり、これらの機器は、他でのアプリケーションよりもはるかに高い周波数で動作する必要があります。これらのニーズを満たすには、(マルチフェーズ降圧型コンバータと呼ばれる) 複数の降圧型コンバータを並列に動作させて、共通の負荷を駆動することが重要です。マルチフェーズ降圧型コンバータは、高電力の要件を満たすためにサーバーおよび通信業界で一般的に使用されています。

マルチフェーズ降圧コンバータの利点

システムの基本周波数は、使用される位相の数で効果的に乗算されます。これにより、コンバータが非常に高い周波数で動作できるようになります。つまり、コンバータは、より小さな部品とより少ない出力容量で、より高い電流要件を満たすことができます。

降圧型コンバータは、高速過渡応答をもつ必要があります。つまり、入力から出力にエネルギーをすばやく転送できなければなりません。シングルフェーズ設計の場合、これには小さなインダクタンスが必要であり、大きくて非実用的な電流リップルが発生する可能性があります。並列コンバータを使用して負荷を駆動することにより (および各分岐が同じ位相シフトで動作することにより)、定常状態の電圧リップルと入力と出力の両方のRMS電流が減少し、必要な入力および出力の容量が小さくなります。

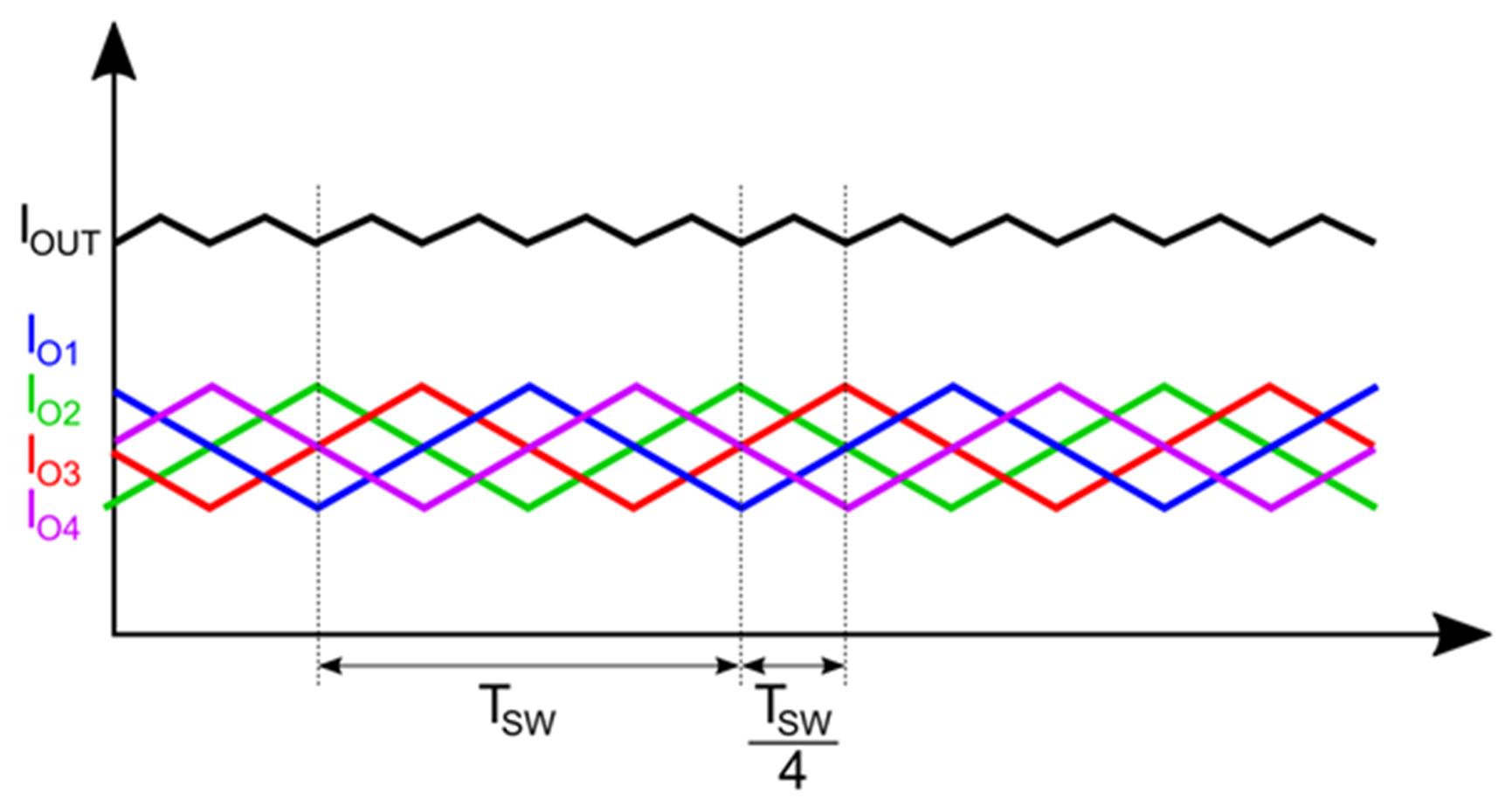

この電流リップルをキャンセルすることで、より小さなインダクタンスを効果的に使用できるようになり、過渡的な電圧スパイクも減少します。これは、リップルの振幅がN個の分岐で除算され、その周波数がN倍大きくなる周波数乗算効果によって起こります。たとえば、4相のアプリケーションでは、総インダクタ電流リップル (IOUT = IO1 + IO2 + IO3 + IO4) は4分の1に小さくなり、リップル周波数は各位相で4倍大きくなります (図1を参照)。

図1: 総出力電流リップル

マルチフェーズコンバータは、コンバータの熱効率も向上させます。電流を複数の位相に分配することにより、電力損失も分担されます。これにより、各分岐への熱応力が最小限に抑えられ、ヒートシンクのサイズが小さくなり、ソリューション全体の費用対効果が高まります。

マルチフェーズ降圧型コンバータの課題

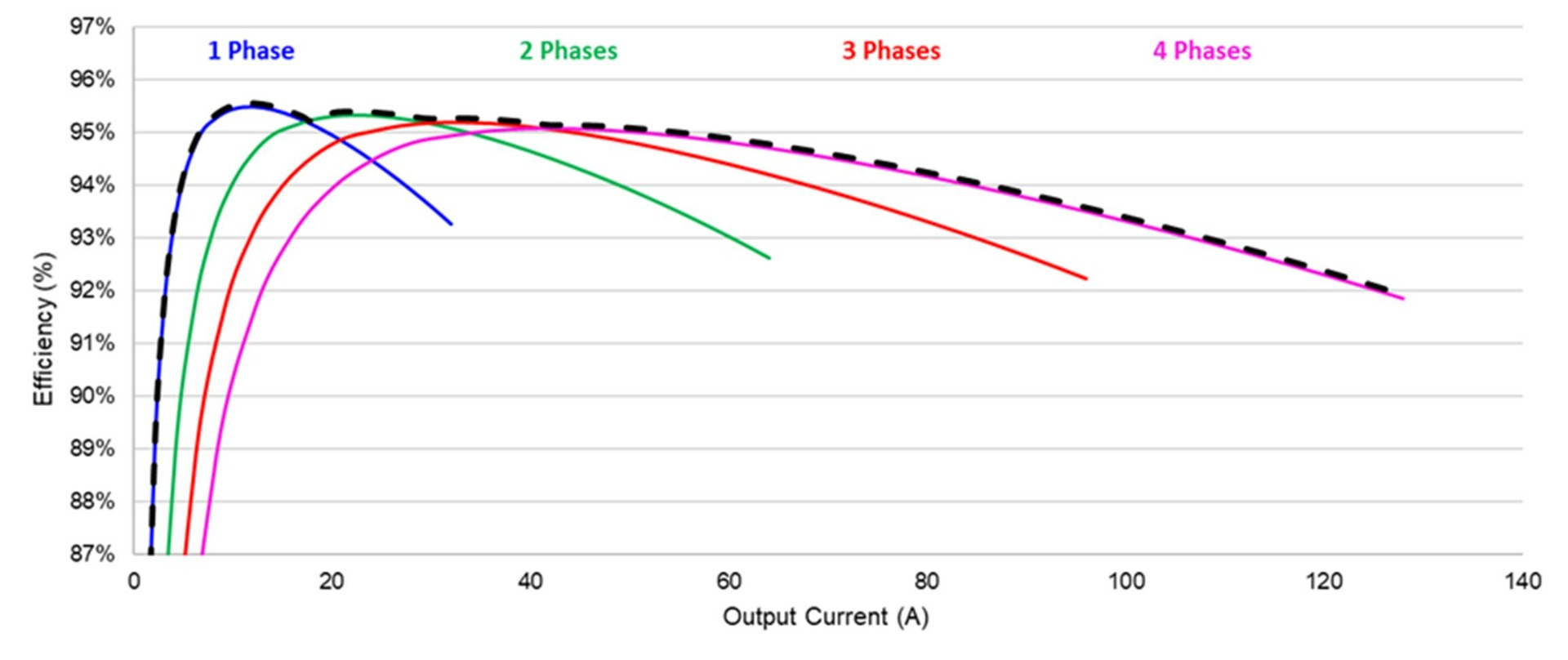

マルチフェーズコンバータは、非常に高速の応答時間で高電力レベルを実現するための鍵です。ただし、サーバーの電源装置などの一部のアプリケーションでは、システムに必要な電力が大きく異なります。たとえば、出力電流が100Aの場合、電流を供給するためにはすべての位相が必要ですが、電流が10Aに低下した場合、過剰な相数は追加の電源スイッチのスイッチング損失により、効率を低下させます。

デジタルコントローラの実装

デジタルコントローラは、負荷電流に応じて位相操作を変化させる、適応性のあるフェーズシェディングや位相制御などの制御方式を採用することで、さらに効率を向上させることができます。設計者は、これらの戦略を使用して、すべての負荷電流範囲にわたって望んだ目標効率を得ることができます。

図2: フェーズシェディング

設計仕様

表1に、平均的な電源レールの要件を示します。入力電圧 (VIN) は12Vに設定されています。これは、ほとんどのアプリケーションで一般的な値です。出力電流 (ITDC) は220A、出力電圧 (VOUT) は1.8Vです。これは、サーバーアプリケーションの電圧レールの一般的な値です。

表1: 電源レールの仕様

ドライバとMOSFETの選択

ほとんどのマルチフェーズコンバータでは、各位相のピーク電流を40A程度に制限するように設計されています。ただし、業界内の革新により、最大70Aの連続電流を供給するMP86957のようなICなどを使用して、非常に高いピーク電流を処理できるソリューションが生まれました。この設計ルールは、スペースの制約、ヒートシンクの使用やそれらの熱特性など、他のパラメータにも依存します。

マルチフェーズコンバータソリューションの実装

マルチフェーズコンバータの利点を説明するために、本稿では、7相設計で実装された分岐あたり約40Aの保守的な電流分布を目標に使用します。この設計により、最大電流が十分に低く保たれるため、熱放散と電力損失をより管理しやすくなります。

選択したスイッチング周波数 (fSW) は500kHzです。7相設計では、周波数逓倍効果により、総出力リップル周波数は3.5MHzになります。

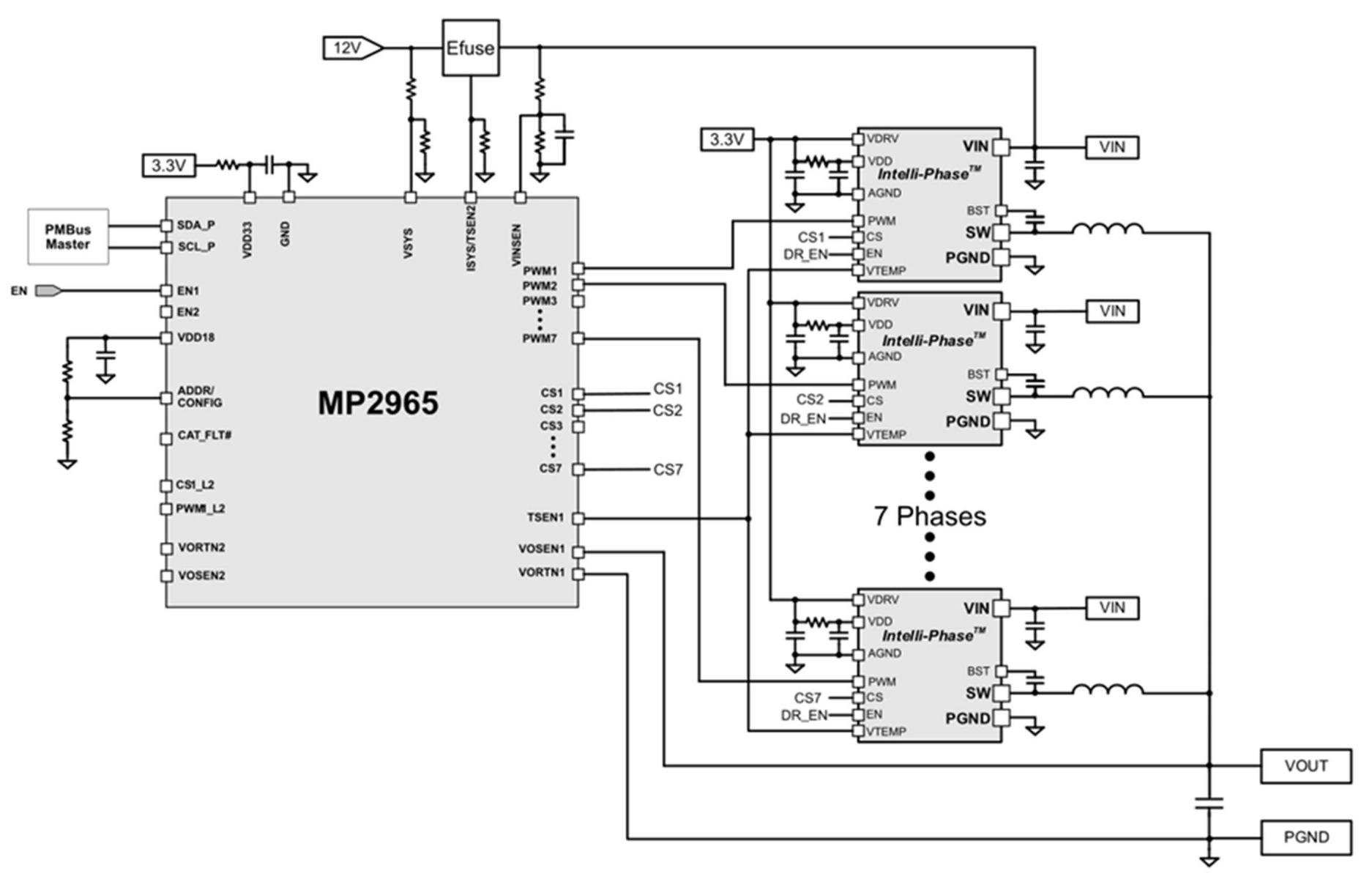

MP2965は、最大7相動作まで設定可能なため、デジタルコントローラとして選択されました。このコントローラは、パルス幅変調制御を使用して、入力電圧と出力電圧に応じてPWMのオン時間をリアルタイムで調整します。マルチフェーズ電圧レギュレータソリューションを完成させるために、この設計では 最大60Aの連続出力電流を実現できる、モノリシックなハーフブリッジであるMP86945Aも使用します。

図3: インタリーブ降圧コンバータのブロック図

出力インダクタの選択

インダクタ電流の過度に大きなリップルは、速度と効率の問題を起こすため、出力インダクタンスは重要なパラメータです。各位相の最大電流リップル (ΔIL) は、最大相電流の20%から40%の間に設定する必要があります。この例では、30%の電流リップルが選択され、目標効率(η)は90%に設定されました。

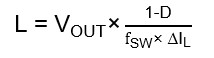

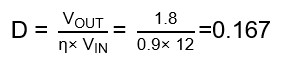

インダクタンス (L) は、式(1)で推定できます。

ここで、Dはデューティサイクルであり、式(2)で計算されます。

アプリケーションの値を入力した後、式(3)で推定されるように、推定インダクタンス (L) は220nHであることがわかります。

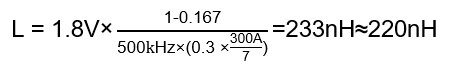

出力コンデンサの選択

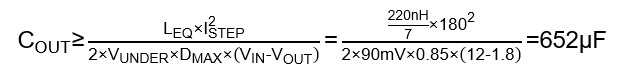

インダクタ電流の連続動作を保証するため、通常、出力電圧リップルを制限するように降圧型コンバータの最小容量が選択されます。このリップルは通常、平均出力電圧の1%に制限されます。システム仕様によれば、電圧リップルは18mVに設定されています。出力容量 (COUT) は、式(4)と式(5)で計算できます。

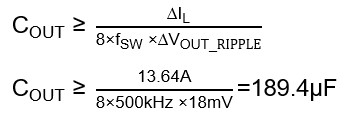

出力容量を決定する場合には、コンバータの突然の電流変化によって引き起こされる電圧変動の制限を考慮します。つまり、出力電圧を過電圧 (VOVER) および不足電圧 (VUNDER) のしきい値内に保つように、出力容量も計算する必要があります。VUNDERは、式(6)で推定できます

ここでLEQは等価インダクタンス (7相の場合、L / 7)、そしてDMAXは最大デューティサイクルです。

式(6)のCOUTは、式(7)で計算できます。

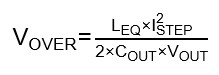

VOVERは、 式(8)で推定できます。

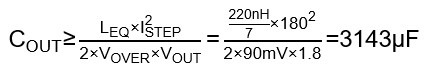

式(8)のCOUTは、式(9)で計算できます。

すべての動作要件を満たすために、上記の式の中から最も高い値を選択してください。

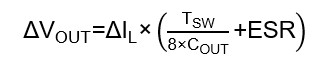

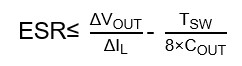

出力容量を決定した後、コンデンサの等価直列抵抗 (ESR) を計算します。これにより、コンバータが定常状態で動作するときの出力電圧リップルが制限されます。出力電圧リップルは、式(10)で推定できます。

ESRは式(11)と式(12)で計算できます。

期待されるESR値が非常に小さいことに注意してください。コンデンサの値やサイズを小さくせずにこのような小さなESR値を取得するには、いくつかの小さなコンデンサを並列に配置します。これは、ESRを低減しながら容量を合計します。

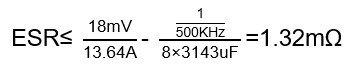

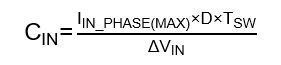

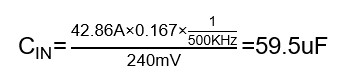

入力コンデンサの選択

入力コンデンサは、コンバータに低インピーダンスの電圧源を提供し、入力電流リップルをフィルタリングします。さらに、設計に位相を追加すると、トータルの入力RMS電流が減少し、自己発熱の影響が最小限に抑えられます。図4は、相数とコンバータのデューティサイクルに応じた電流の正規化された値を示しています。

図4: デューティサイクルと相数の関数として正規化されたRMS電流

降圧コ型ンバータの入力容量は、通常、アプリケーションの仕様に従って入力電圧リップルを制限するように選択されます。このアプリケーションでは、ΔVINの値は240mVで、入力容量 (CIN) は式(13)と式(14)で推定できます。

結論

サーバーシステムの厳しいパフォーマンス要件により、過渡応答要件を満たし、大電流に耐えられるようにするために、ほとんどのサーバーおよびコンピューティング設計においてマルチフェーズ降圧コンバータが必要です。MP2965デュアルチャネル、マルチフェーズコントローラは、最小限の出力コンデンサで優れた設計の柔軟性と高速過渡応答を提供します。MP86945Aのパワーステージは、ドライバとMOSFETを集積して、高効率とパフォーマンスを実現します。

_______________________

興味のある内容でしたか? お役に立つ情報をメールでお届けします。今すぐ登録を!

アカウントにログイン

新しいアカウントを作成