CISPR25 Class5に適合する熱最適化2層車載用PCB設計

役立つ情報を毎月お届けします

プライバシーを尊重します

はじめに

カーエレクトロニクスのサプライヤは、自動運転、コネクテッド、および電動ソリューションの生産競争において、コストに対する圧力の高まりに直面しています。設計コストを削減する効果的な方法の1つは、2層の車載用PCBを使用することです。しかし、2層PCBは熱特性が悪く、性能が低下する可能性があるため、特別な注意が必要です。

本稿では、車載のエキスパートがMPSのMPQ4323-AEC1を使用して、2層PCBの回路図およびレイアウト設計を微調整して最高の熱特性を実現し、CISPR25 Class5の基準を十分に満たすことができるようにするための実践的なアドバイスをします。

2層レイアウトの使用

必要な層の数は、プリント基板のスペースと部品の数、および計画された生産コストによって異なります。ハードウェア設計者は多くの場合、2つの層しか使用できません。2層の車載用PCB設計において、DCスイッチング電源は、EMCおよび温度要件を満たすために慎重な部品配置が必要です。

関連コンテンツ

方法

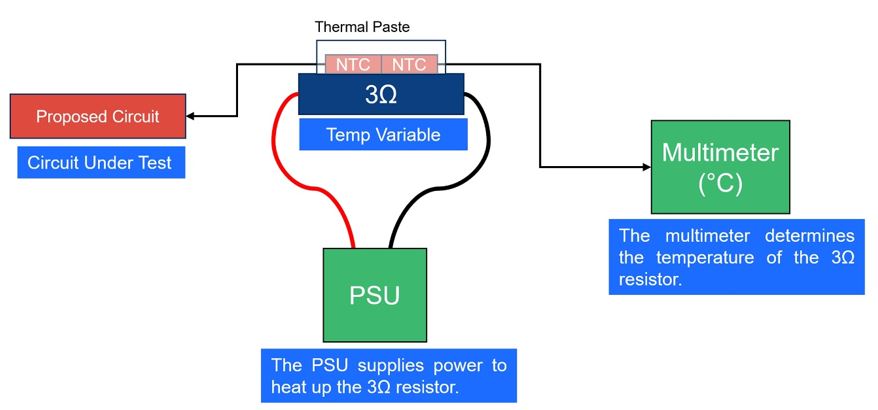

本稿では、9つの2層レイアウトをテストしました。各レイアウトには他のPCBと比較して、独自の部品位置とわずかな変更があります。また、ポリゴンとビアの配置も異なります (図1参照)。9つのレイアウトの使用目的は、EMCと熱対策が向上したソリューションを見つけるためでした。本稿では、これらのレイアウト間の熱およびEMCパフォーマンスの違いに焦点を当てます。

図1 : 9つの異なるレイアウトのPCBパネル

2層レイアウトの推奨事項

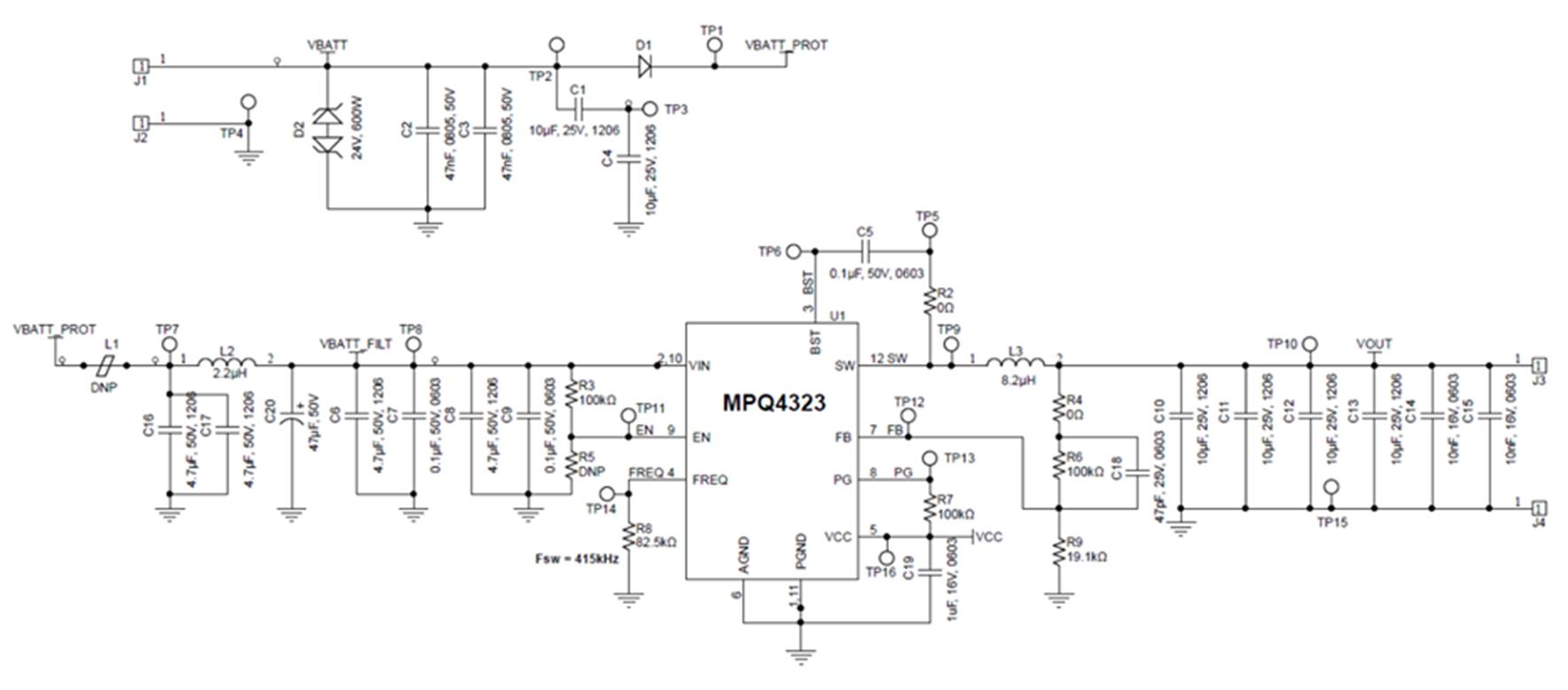

特定の設計ルールに従うことで、熱とEMCに対して最適化されたソリューションを実現できます。図2に、MPSのMPQ4323-AEC1を使用した回路の例を示します。このDC電源は、自動車のEMC CISPR25 Class5の要件を満たし、熱的に最適化された2層レイアウトを使用するDC電源です。

図2 : 車載EMCに適合した温度最適化MPQ4323の回路図

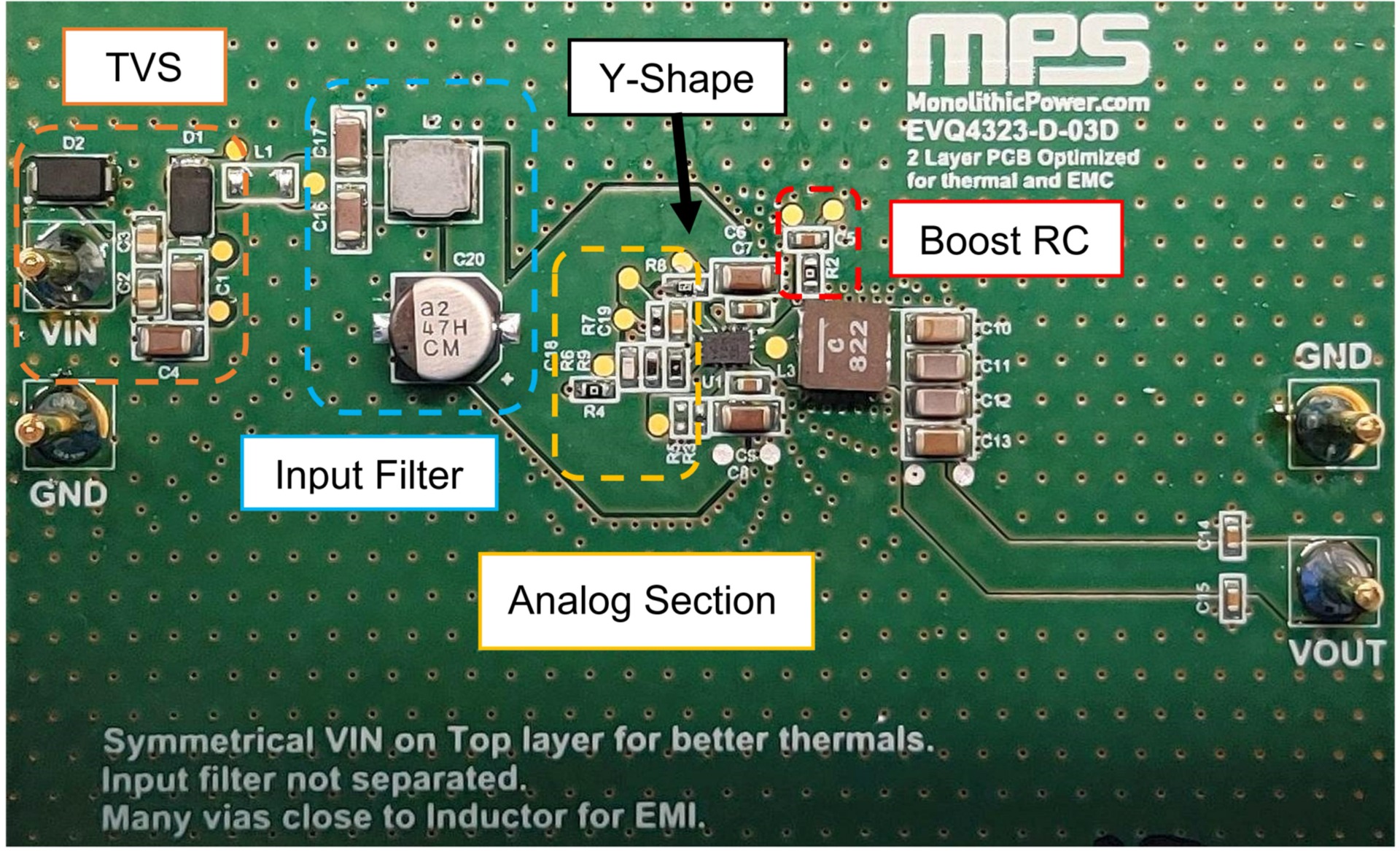

図3は、図2の回路図を使用したPCB部品の配置を示します。

図3 : MPQ4323 2層PCB構成部品の配置

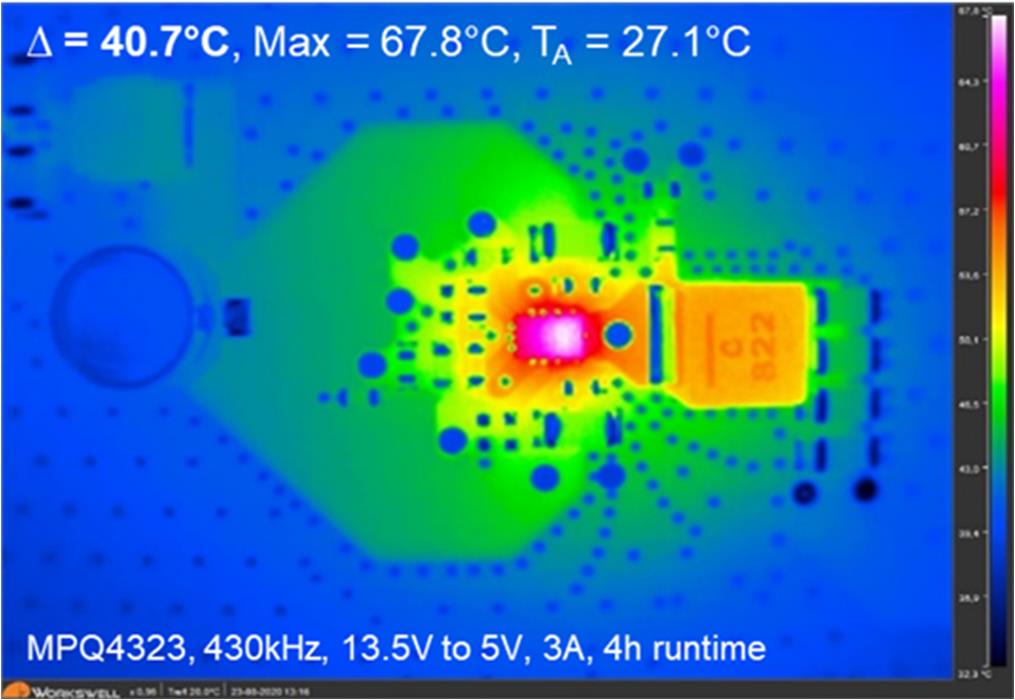

推奨レイアウトは、ソリッドな上面、底面のGNDプレーン、および大きなVINのポリゴンがあることです。また、上部と下部の層を接続するPGNDビアも利用します。図4は、 MP8030の熱画像です。Y字の形をしたVINのヒートシンク・ポリゴンは、上層の熱を引き出します。PGNDビアは、上部および下層に接続され、第2の有効なヒートシンクとして機能します。

図4 : MPQ4323の2層PCB熱画像

インダクタ (L3) は効果的なヒートシンクとして機能します (図4参照)。この例では、ピン12上のスイッチングノードは、その急速に変化する電圧 (高いdu / dt) のために放出アンテナとして作用しないように、表面積が小さい必要があります。インダクタをピン12のできるだけ近くに配置します。短い距離がインダクタへの最適な熱流を可能にするためです。すぐれたEMCを実現するには、インダクタの巻線の印を付けた側をピン12に合わせます。これにより、インダクタンス外側の銅巻線は、高いdu / dtを有するインダクタコイルのノイズの多い内側領域をシールドできます。図5はパッケージ内の熱分布を示しています。

図5 : MPQ4323パッケージ内の熱分布

PCBに熱を伝達するのに最も効果的なピンは、VIN、PGND、およびSWです。内部リードフレームは、これらのピンをハイサイドおよびローサイドMOSFET (それぞれHS-FETおよびLS-FET) に直接接続します。リードフレームは、効果的な熱流のために、ダイの下に内部はんだ付けされています。

MOSFETは内部で熱が発生する場所であるため、MOSFETに近いほどダイは熱くなります。この効果は、マゼンタの領域 (約62°C) と比較した場合に、パッケージの白の領域 (最大67.8°C) で確認できます。銅の熱伝導率は388W/mKであり、シリコンの熱伝導率は180W/mKです。これは、熱が銅の中で、より均等に分配されることを意味します。なお測定された温度はパッケージの表面であり、内部のダイ温度は数度高くなっています。

アナログピン (BOOT、VCC、AGND、FB、PG、およびEN) は、リードフレーム上の内部全長が短いMOSFETと比較して、熱伝導率はそれほど効率的ではありません。したがって、レイアウトを設計する場合、電源ピン (VIN、PGND、SW) には、デバイスを冷却するための大きな銅の面が必要です。電源ピンの近くの上層は、最も効果的なヒートシンクです。

上部GND層と下部GND層の間に配置されたビアは、それが電源ピンに近いほど、より効果的に熱を流すことができます。ビアは高温の場所に配置することをお勧めします。ただし、隣接するビアの数が多すぎないようにしてください。穴の数が多すぎると、銅が足りずに上部層の熱流が妨げられることがあります。

熱流のためには、上部層が直接銅に接続されていることが重要です。下部層はビアとの熱による直列接続により劣化します。熱対流を向上するために、DC電源スイッチング電源を上層に配置することをお勧めします。

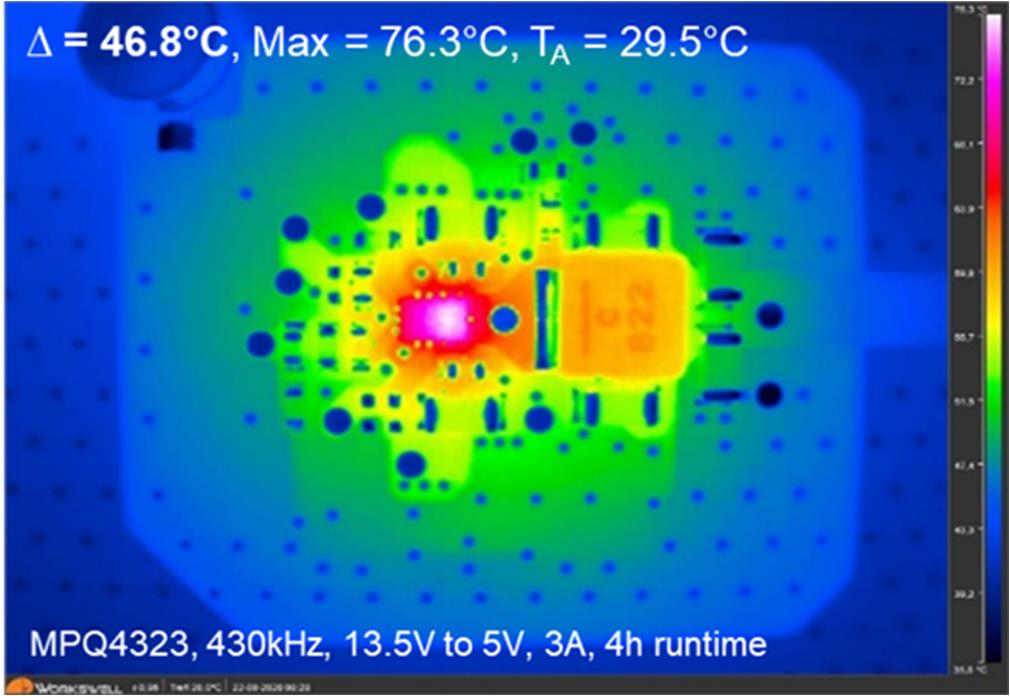

図6は、DC/DCコンバータ周囲のGNDをカットした従来のレイアウトを示しています。一方、下層にはVINがY字状に接続されています。

図6 : PCBへの熱流入が少ない従来レイアウトのMPQ4323

両方のレイアウト間の最大TJUNCTION (白色エリア) とTAMBIENT間の温度差 (ΔT) を比較します。図4 (熱最適化された推奨レイアウト) では、ΔTは40.7°Cです。従来のソリューションでは、ΔTは46.8°Cです。

推奨レイアウトでは、従来のレイアウトよりも6°C低い温度で実行されます。これらはすべて、余分な部品やより大きなボードスペースを使用することなく実行されます。この改善は、5つの電源ピンすべてを賢く使い、VIN領域を拡大し、上部GNDとボットGND層との間に十分なPGNDビアを設けることで可能です。

MPQ4323-AEC1と類似ソリューションとの比較

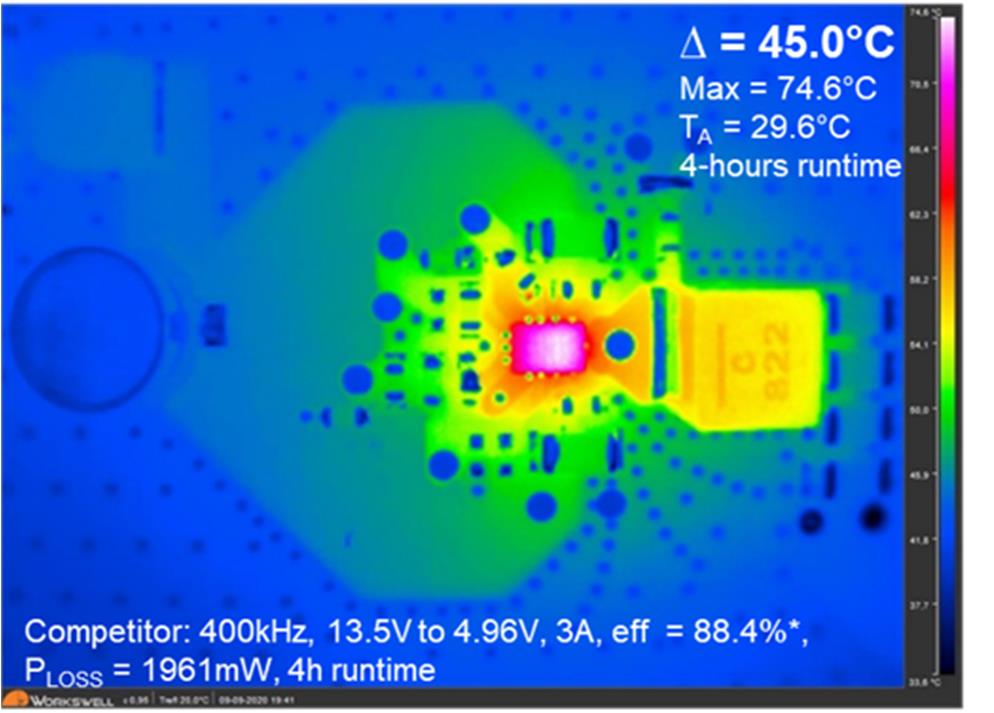

図7は、ソリューション (ソリューション2) とMPQ4323-AEC1を比較したものです。両方のデバイスが同じICパッケージサイズを使用し、両方のICが同じ外付け部品と同じレイアウトで動作することに留意してください。

図7 : ソリューション2 PCBの熱結果

表1に、両方のソリューションの特性を示します。

表1 : MPQ4323 vs. 類似ソリューション

| MPQ4323-AEC1 (図4) | ソリューション2 (図7) | |

| ∆T | 40.7K | 45K |

| スイッチング周波数 (fSW) | 430kHz | 400kHz |

| 入力電圧 (VIN) | 13.5V | 13.5V |

| 出力電圧 (VOUT) | 4.93V | 4.96V |

| 出力電流 (IOUT) | 3A | 3A |

| 効率 | 89.9% (1) | 88.4% (1) |

| 電力損失 (PLOSS) | 1841mW (4時間稼働時) | 1961mW (4時間稼働時) |

注 :

1) 効率測定には、入力フィルタ、保護ダイオード、および電力インダクタの損失が含まれます。

MPQ4323-AEC1の温度が低いのは、MPSの高度なパッケージ技術の結果であり、これはより多くの熱をPCBに流すことができます。

EMC結果

図8は、MPQ4323-AEC1の伝導エミッションおよび放射エミッションに対するCISPR25 Class5のEMC測定結果を示しています (150kHz~30MHz)。

図8 : 伝導エミッション (150kHz~108MHz) および放射エミッション (150kHz~30MHz) (合格)

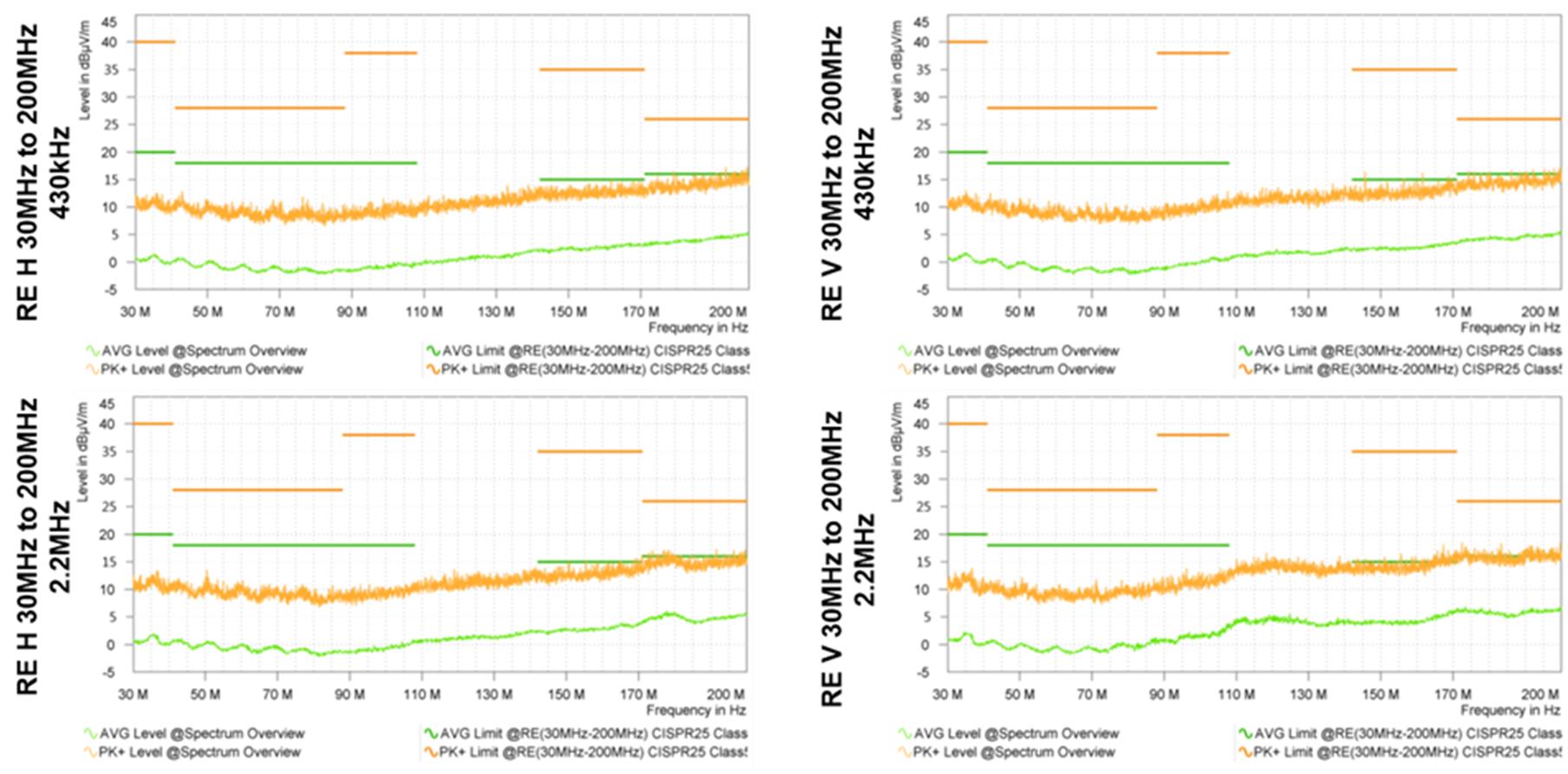

図9は、MPQ4323-AEC1の伝導エミッションおよび放射エミッションに対するCISPR25 Class5のEMC測定結果を示しています (30MHz~200MHz)。

図9 : 水平放射エミッション (30MHz~200MHz) および垂直放射エミッション (30MHz~200MHz) (合格)

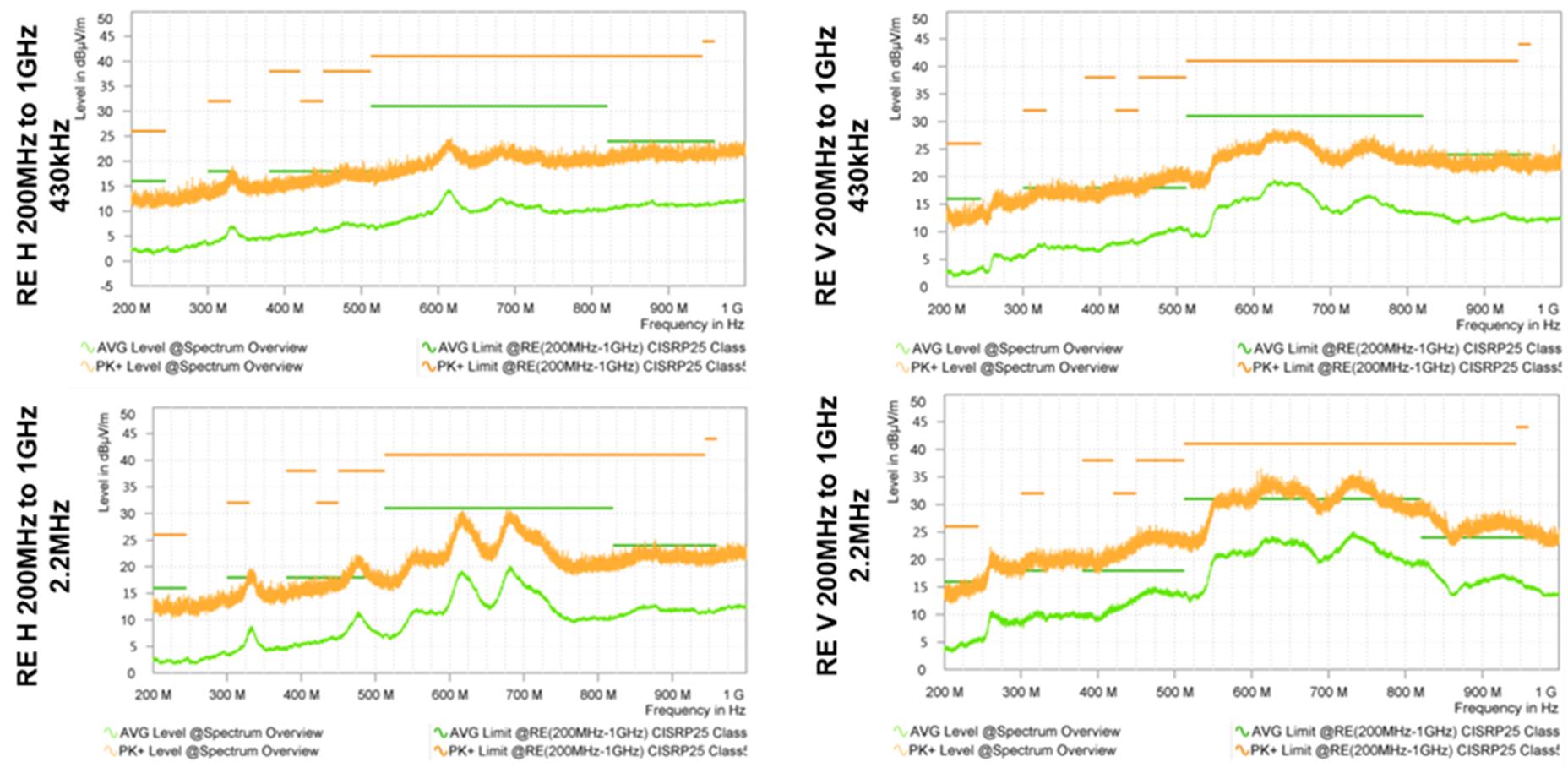

図10は、伝導エミッションおよび放射エミッションに対するCISPR25 Class5のEMC測定結果を示しています (200MHz~1GHz)。

図10 : 水平放射エミッション (200MHz~1GHz) および垂直放射エミッション (200MHz~1GHz) (合格)

2層PCBのみを使用して車載用のEMC要件を満たすことは、通常厳しい要求の作業ですが、すべてのEMC測定値が要求される制限値を下回っています。4層PCBは、車載用DCスイッチング電源の一般的で標準的なソリューションですが、4層レイアウトはコストを増加させます。本稿での方法は、2層PCBが、熱上昇を低く維持しながら、車載用のEMC要件を満たすことができることを示しています。

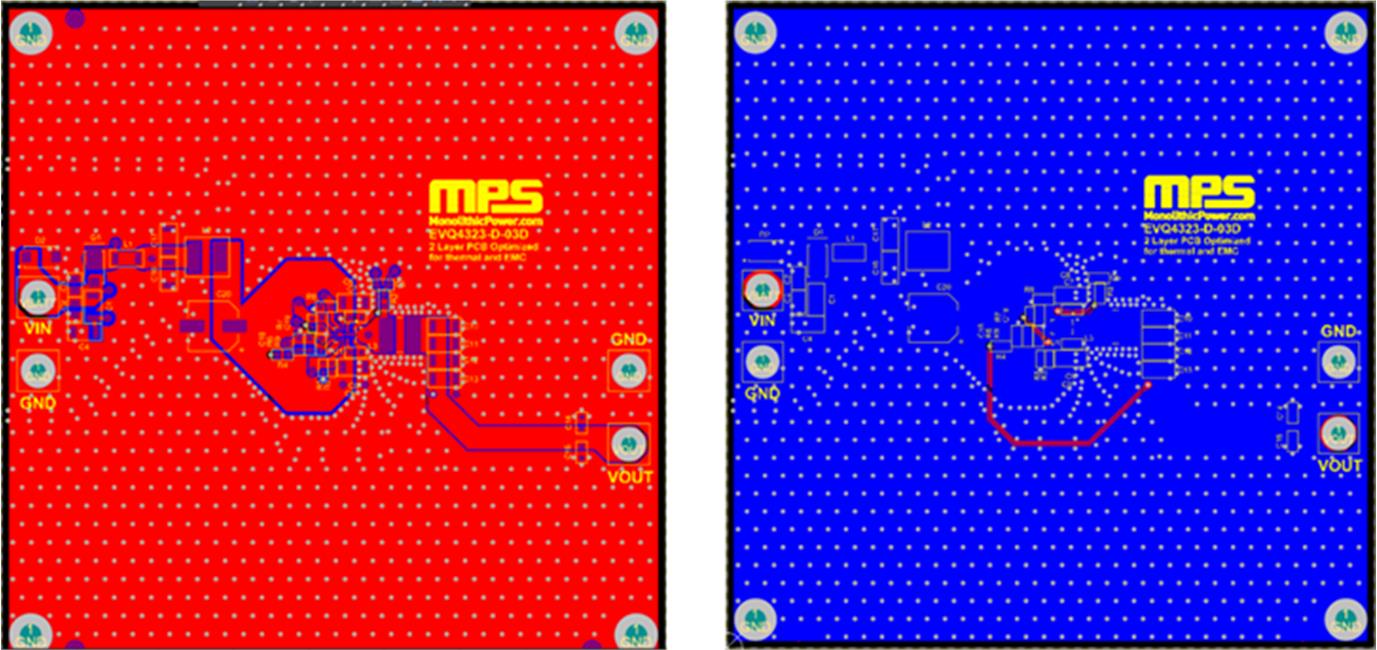

推奨PCBレイアウト

推奨PCBレイアウトを図10に示します。上層は、インピーダンスとノイズが低いVINをもつ、Y字型のポリゴンを示しています。上層には、ICの近くにビアや導体は配置されていません。上部から下部の層へのビアは、熱流がある場合にのみ、電源ピンの近くに配置されます。

図11 : 新しい推奨レイアウト (左 : 上層、右 : 下層)

構成部品を適切に配置した結果、両方の層間に配線部分が3つだけになります (下層に赤色で表示)。最も長い配線は、FBフィードバック抵抗器に至るVOUT検出配線です。VOUTは静かで (EMCに対して良好)、イミュニティに影響されません。これらの配線は、EMCに対して配線をシールドする下部GND層に完全にカプセル化されています。

C13とR4との間のVOUTの配線は、スイッチングノードの急速に変化する電界に対するイミュニティを向上するために、スイッチングノードから離れて配線される必要があります。GND層内の距離とシールドがカップリングを減らします。

最も影響を受けやすい配線は、R6とフィードバック (FB、ピン7) の間です。この配線は上層に配線し、できるだけ短くする必要があります (長さは数ミリメートル)。ICの下には、大きくて途切れのないGNDプレーンが必要です。つまり、下層の3つの配線がICの近くのGNDプレーンを分断しないようにします。GNDプレーンを分断すると、周波数に比例してインピーダンスが増加します。無傷のGNDプレーンは、良好なEMCおよび回路パフォーマンスの基礎です。

2層の車載用PCBを設計する場合は、次の点に注意してください。

- 上層は、下層より熱の流れが良い。

- 電源ピンの近くに配置されたビアは、遠くに配置されたビアと比較して、熱の流れが良い。

2層PCBを最適化するには、以下のガイドラインに従ってください。

- 電源ピンがPCBへの効果的な熱流に最も大きな影響を与えるため、電源ピンの銅面積を最大にする。

- ヒートシンクの電源ピンには、アナログピンよりも高い優先順位を設定する。

- インダクタンスの印を付けた側をスイッチングノードのできるだけ近くに置き、銅の面積を最小限に抑える。

- 冷却電源のポリゴンを導線で分断しない。これは、ピンからPCBへ流れる熱を大幅に減少させる可能性があるため、電源ピンのすぐ近くでは特に重要。

敷設された各配線と、干渉、放射、および耐性への影響を考慮した上で、可能な限り最適な位置、配線幅、およびビア接続を選択します。

結論

過酷な環境で良好に機能することができる費用効果の高い2層PCBの設計をすることが可能です。低コスト設計はMPQ4323-AEC1を用いて実証したようにCISPR25とOEMの制限を受けたEMI試験に十分な余裕をもって合格できます。この車載用PCB設計で、ICは、放熱のために十分な銅面積が与えられた場合、400kHz動作で約100℃、または、2.2MHz動作で約80℃の周囲温度の下で、ほぼ完全な出力動作を達成できます。MPSは、より高い効率のために熱強化リードフレームを設計して、コンパクトでスペースに制約のあるシステム内で動作できる熱的にすぐれたソリューションを実現します。

_______________________

興味のある内容でしたか? お役に立つ情報をメールでお届けします。今すぐ登録を!

アカウントにログイン

新しいアカウントを作成