5G基地局の複雑さが低EMI DC/DCモジュールソリューションの必要性を促進

役立つ情報を毎月お届けします

プライバシーを尊重します

5G通信規格は、家庭や産業の自動化、自律走行車、ヘルスケア、スマートウェアラブルなどの市場で、スマートフォンやスマートコネクテッドデバイスからのデータ量への要求がどこまでも増加し続けるのをサポートすることを目的としています。5Gは「大規模な多入力多重出力」(大規模MIMO) アンテナアレイと呼ばれるものを使用して、基地局ごとにより多くのデータ接続を可能にします。

既存の4G基地局は、アレイあたり最大4つの送信機と4つの受信機要素(4x4 MIMO)を使用できます。これに対し、5Gは最大64の送信機と64の受信機の大規模なMIMOアレイを使用することが期待されています。基地局ノードあたりのチャネル数が多いだけでなく、5Gは、約1msの非常に短い待ち時間で、4Gネットワークよりも最大100倍のデータレートをサポートできます。

このことは、基地局ごとに、より多くのモデム、データ変換器、高速ベースバンドデジタル処理が必要になることを意味します。推定によると、5G基地局は既存の4G設計の3倍の電力を必要とします。ハードウェア設計者は、この追加処理と電子機器を既存の4G基地局のエンクロージャと同様の形状要素に絞り込む電源ソリューションを見つけるという課題に直面しています。ボードコンポーネント密度の向上には、従来の個別のDC/DCおよび外部インダクタベースのソリューションよりも高い効率と低いEMIを備えた省スペースソリューションが必要です。

基地局は通常、48V入力でDC/DCコンバータによって24Vまたは12Vに降圧される電源を使用し、ベースバンド処理段階でASICに電力を供給するために3.3Vから1V未満の範囲の多くのサブレールにさらに降圧します。

非常に多くの電源レールを生成することになるので、従来の個別の降圧DC/DCコンバータを使用して、コントロールICと内部または外部電源MOSFETを使用し、外部インダクタとコンデンサを使用するなら、複雑で時間のかかる作業が発生しします。正しいインダクタのサイジングと構造、入力容量、入力フィルタリング、出力容量を、各コンバータで考慮する必要があります。動作の頻度やシーケンス機能などの追加の要因も考慮する必要があります。

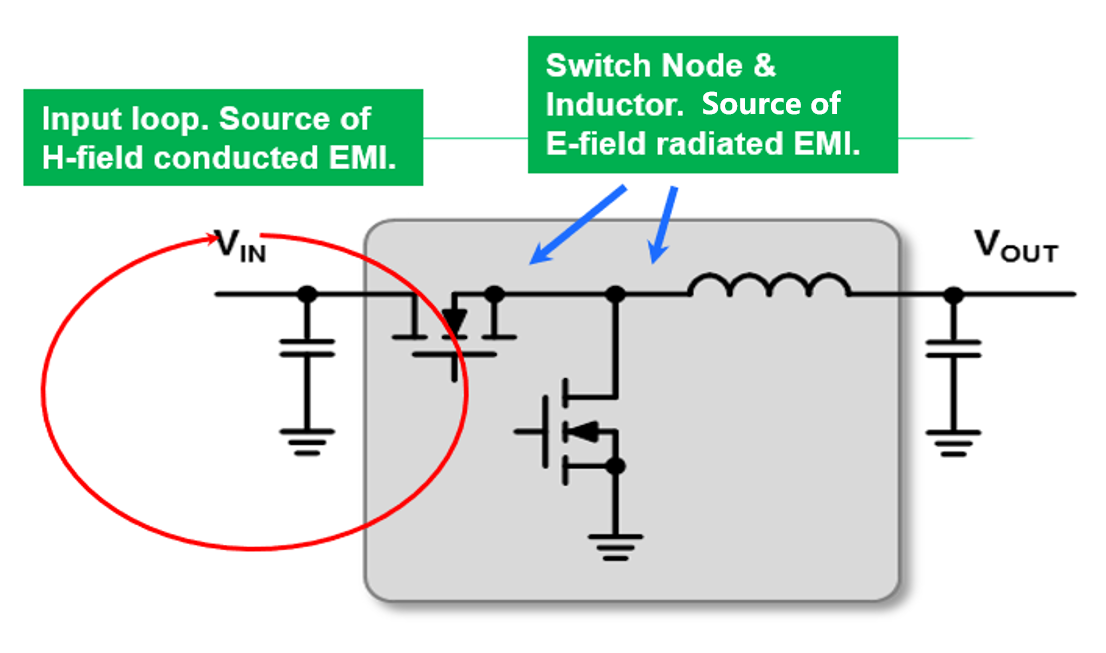

コンバータとインダクタ回路のスイッチング電流によって生じるEMIの伝導と放射を最小限に抑えるためには、慎重なコンポーネントのレイアウトとフィルタコンポーネントの配置が必要です。DC/DCコンバータは、通常、出力パワーMOSFETスイッチングノード出力からグランドへ、そして入力コンデンサからグランドへの間に形成される電流ループパスからの磁場から伝導EMIを生成します。また、MOSFETスイッチングノードからインダクタ接続に放射電界EMIを生成し、高い入力電圧レベルからグランドへの連続的な切り替えがあるため、およびインダクタ自体で発生する電磁場から高いdV/dtが生じます (図1参照)。

図1: DC/DCステップダウン・コンバータからの標準的なEMI ソース

設計を正しく行わないと、設計のやり直しやEMIラボの再テストを行ない高く付く可能性があります。

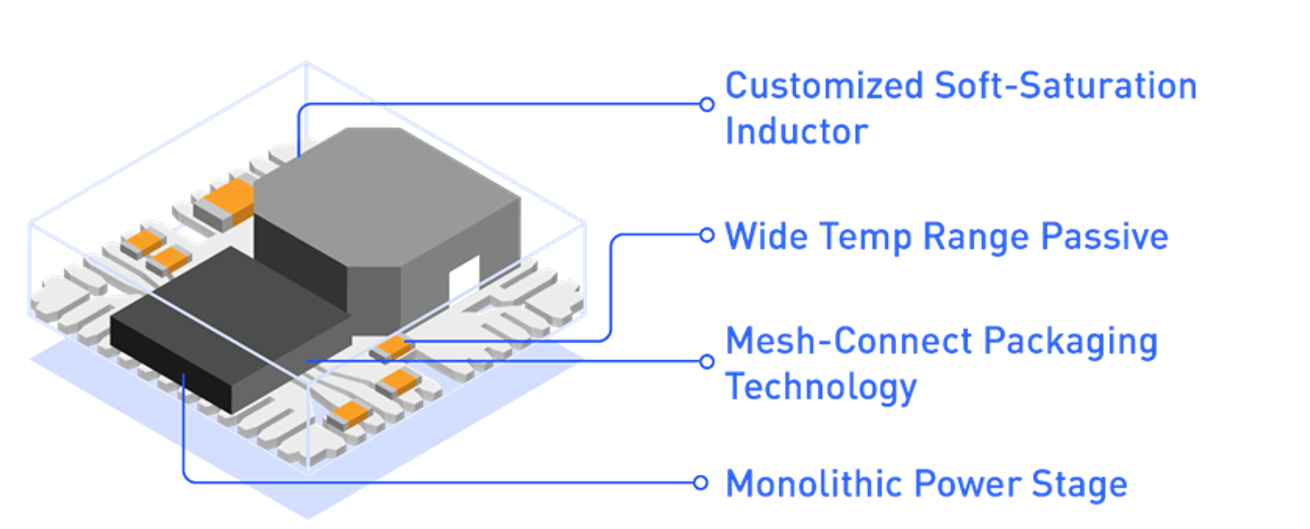

設計を簡素化し、市場投入までの時間を短縮するための別のアプローチは、各電源レールに自己完結型のDC/DCコンバータモジュールを用いることです。半導体プロセス技術とパッケージ構築の進歩により、最新世代のDC/DCモジュールは、小型形状で非常に高い電力密度、高効率、優れたEMI性能を実現しています。パッケージ内フリップチップやMesh Connect™リードフレーム技術などの新しい製造技術は、IC、インダクタ、受動部品をワイヤボンディングや追加の内部PCBなしでリードフレームに直接取り付けることができることを意味 します (図2参照)。

図2: 統合モジュールDC/DCステップダウン・コンバータ構造

この新しい形の構築は、相互接続のリードフレームを利用することで、いくつかの利点があります。EMIは、より良く制御され、放熱が改善され、実装面積が小さくなります。

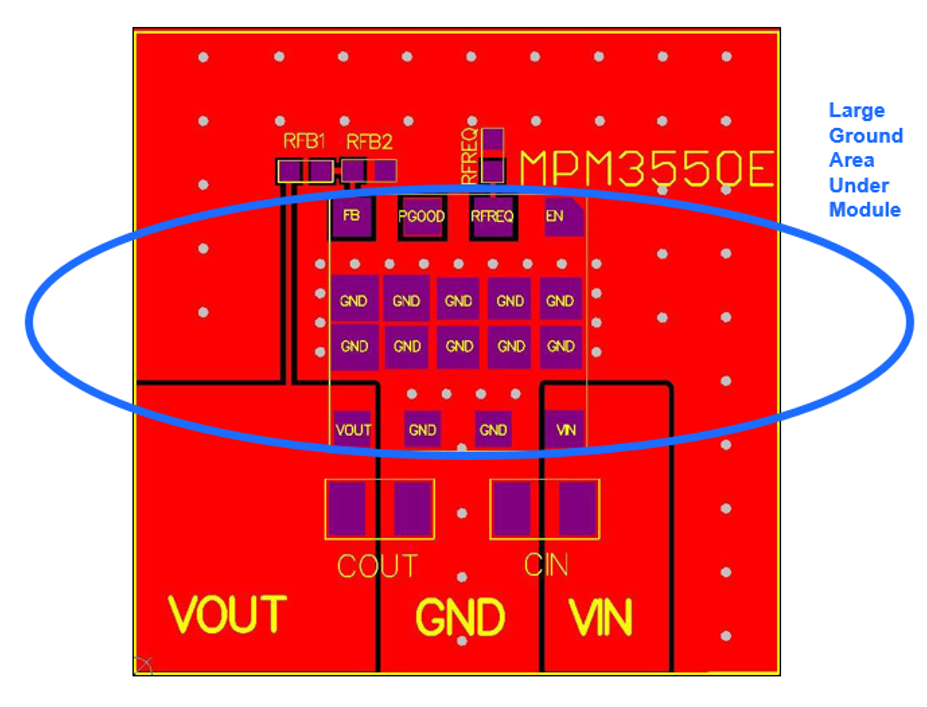

内部PCB基板またはワイヤボンディングを使用する古い構造スタイルと比較して、接続配線長を最小限に抑えることができ、受動部品への直接接続はEMIを最小限に抑えるためにインダクタンスを低く保ちます。ターゲットPCBに直接サーフェスマウントされるランド・グリッド・アレイ (LGA) パッケージ形式を使用すると、EMI を放射し得るリードを備えた代替 SIP / SILスタイルコンバータよりも低いEMI特性を提供できます。LGAパッケージにより、ソリッド アースプレーンがモジュールの下の領域の大部分をカバーできるため、渦電流ループを閉じ、EMIをさらに削減するのに役立ちます (図3参照)。 一部のモジュールタイプでは、金属缶でカバーすることができ、放射EMIの減衰を追加することができます。

図3: モジュールの大きなアース層実装面積はEMIを減らすのに役立つ

MOSFET電源段階からの熱伝導は、MOSFETダイ源とドレインからモジュールのリードフレームへの直接銅柱接続と、下のターゲットPCB銅への直接接続によって改善されます。これにより、ボンドワイヤや内部回路基板が放熱に対して断熱バリアとなる従来の構造よりも小さなモジュールサイズが可能になります。

MPSのMPM3550Eは、集積モジュールアプローチでスペース節約を際立たせています。このモジュールは、最大36V入力を受け付け、12V~1Vの調整可能な範囲で、5A定格出力電流を使用できます。パッケージ寸法はLGA形状形式で12mm x 12mm x 4.2mmです。

従来の36V、3.5A個別部品DC/DCレイアウトとは異なる外部インダクタと受動部品の実装面積で、MPM3550Eの実装面積は約30%の節約になります (図4参照)。

図4: 集積モジュールDC/DCステップダウン・コンバータ・ボードの領域対従来のディスクリートDC/DCの領域

省スペースの向上に加えて、デザイナーは、個々の部品選択やコンバータレイアウトの作業から解放されました。これらの問題は、モジュールの内部構成においてメーカーによって既に検討されています。ソフト飽和コア、最適化された電流ループパス、集積された入力フィルタリングを備えた封入磁気パスインダクタの使用により、最終的な設計を放射および伝導EMI規制に確実に適合させる作業が簡単になります。

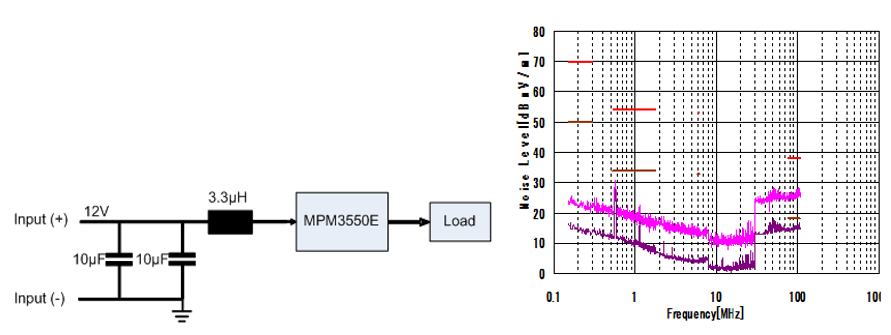

2つの10μFコンデンサと3.3μHインダクタからなるシンプルなLCローパスフィルタは、CISPR22クラスBおよびCISPR25クラス5を含む、伝導放出規格を満たすのに十分です (図5参照)。

図5: 外部EMIフィルタによるモジュールの効果と、結果としての伝導EMI特性

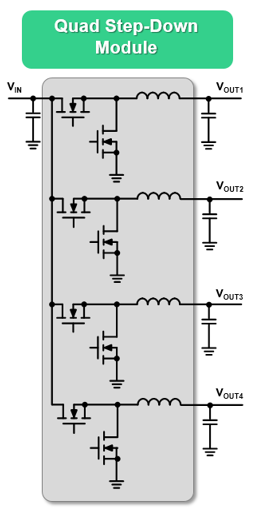

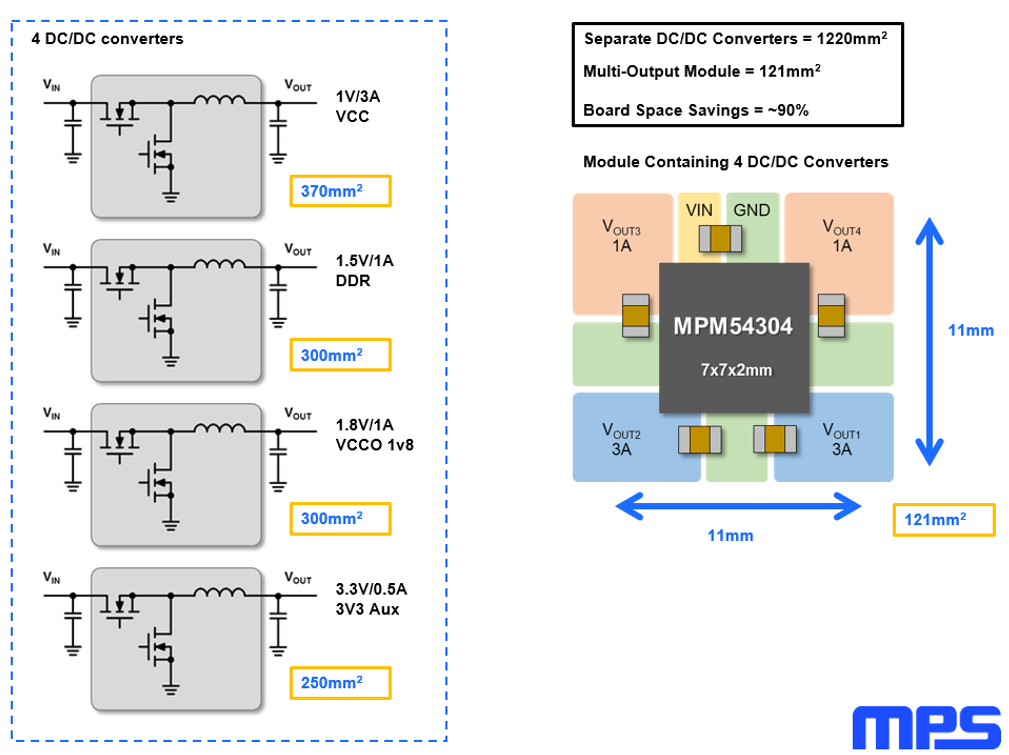

さらに回路基板のスペースを節約するために、複数のDC/DCコンバータを1つのモジュールに組み合わせることでアプローチを拡張することができます。これは、ASICなどの低電圧回路に特に適しています。全体的な電力レベルが低いほど、複数のコンバータをモジュールに集積しながら、管理可能な電力密度と消費電力レベルを達成できます (図6および図7を参照)。

図6: 4つのDC/DCコンバータを集積したモジュールの例

図7: コンパクトな4つのDC/DCモジュールパッケージ

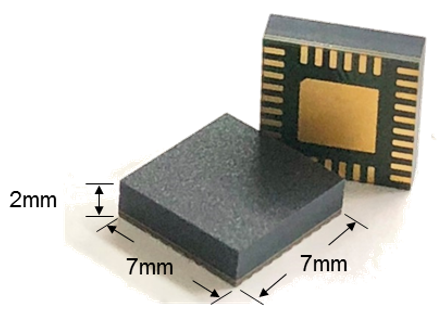

マルチレールモジュールアプローチによって実現されるボードの省スペースは、外部インダクタと受動素子を備えた個々のDC/DCコンバータの使用に比べて90%も高くなる可能性があります。たとえば、図8はMPSのMPM54304モジュールを示しており、インダクタと受動素子を内蔵した単一の7mm x 7mm x 2mmのモジュールに4つの降圧コンバータを集積したものです。

図8: 4つの個別DC/DCコンバータとモジュールアプローチのボードスペースの合計比較

5Gは、設置のキャビネットサイズとラジオマストのローディング機能の限界によって制約されながら、ベースバンドと無線ボードの設計において、より高いレベルの電子回路の集積と電力密度を要求することは確実です。統合されたDC/DCモジュールの使用は、ボードスペース領域の節約に役立つだけでなく、よりシンプルなレイアウトとEMIの削減を含む利点を提供します。これらの要因はまたリスクを軽減し、市場投入までの時間を短縮することにもなります。

_________________________

興味のある内容でしたか? お役に立つ情報をメールでお届けします。今すぐ登録を!

関連記事

アカウントにログイン

新しいアカウントを作成