AN183 - LLCトポロジーを使用した絶縁ゲートドライバ電源の設計

役立つ情報を毎月お届けします

プライバシーを尊重します

概要

調整されていないフライバックコンバータおよびプッシュプルコンバータは通常、インダクタンス漏れによる電力損失を低減するために密結合トランスが必要となる絶縁ゲートドライバ電源アプリケーションに使用されます。現代の高出力システムは、スイッチングノードでのバス電圧 (VBUS) およびdV/dtが高くなることが多くあります。より高い絶縁電圧 (VISOLATION) 定格と低い巻線間容量がトランスの設計に必要ですが、これらは密結合トランスでは実現できません。

共振トポロジーはこの問題に対する理想的なソリューションです。インダクタンス漏れを利用し、疎結合のトランスを実現します。共振トポロジーの利点には、巻線間容量とトランスのサイズの削減、高効率、ロードレギュレーションの向上などがあります。

AN183は、低コストのLLCコンバータのステップバイステップの設計ガイドを提供します。このコンバータは、IGBTおよびSi / SiC MOSFETデバイスの絶縁ゲートドライバ用に設計されています。この設計は、電気自動車のモータドライバ、オンボードチャージャ、グリッド接続インバータなどの自動車および産業用アプリケーションに最適です。

はじめに

ハーフブリッジの一次側MOSFETとハーフブリッジの二次側整流器は、必要なスイッチとダイオードの数が少ないため、低電力アプリケーションに適しています。LLCコンバータの設計では、トランス (T1)、磁化インダクタンス (Lm)、およびインダクタンス漏れ (Ll1、Ll2) が採用されています。共振コンデンサ (Cr) とLC 共振タンクからのインダクタンス漏れ。共振タンクの周波数 (fr) と同様のスイッチング周波数 (fSW) は、共振タンクのインピーダンスを約0Ωに保ちます。LLCコンバータの変換比がトランスの巻数比 (T1の1 : N) に等しい場合、LLCコンバータはDCトランスとして動作できます。経験的に、Lm > 10 x Ll1である限り、この記述は正しいです。LmがLl1に匹敵する場合、変換比はトランスの巻数比 (N) を超え、以下になります。 $$N(1+ \frac{L_{l1}}{L_M})$$

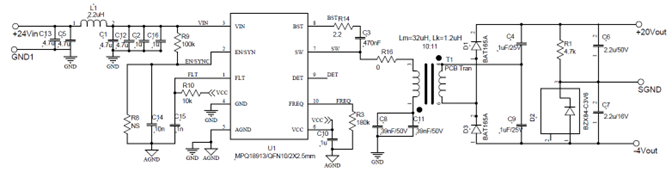

図1はLLCトポロジースキームを示しています。

図1: LLCトポロジースキーム

1. LLCトポロジーを使用したMPSゲートドライブ電源ソリューション

LLCコンバータ設計では、ハーフブリッジトランスドライバとしてMPQ18913を採用しています。高いfSWと広い入力電圧 (VIN) 範囲を備え、システム設計の柔軟性を実現します。図2は、SiCデバイスのゲートドライバ電源設計の概略図を示しています。

図2: SiCデバイス用ゲートドライバ電源設計図

ツェナーダイオードは出力電圧 (VOUT) を2つのレールに分割します。これは、IGBTまたはSiCドライバの使用に適しています。

表1は、MPQ18913を使用したLLCコンバータの部品選択と計算式を示しています。

表1: LLCコンバータの設計計算式と部品の選択

| パラメータ | 計算式と説明 | 注 |

| スイッチング周波数 (fsw) | $$f_{sw} = \begin{cases}

0.5\, \text{MHz} - 0.75\, \text{MHz}, & P_{out} < 6\,W \\

0.75\, \text{MHz} - 2\, \text{MHz}, & P_{out} < 3\,W \\

1.5\, \text{MHz} - 5\, \text{MHz}, & P_{out} < 2\,W

\end{cases}$$

fSWが高いとトランス巻線の交流抵抗が大きくなり、出力電力を制限します。 |

MPQ18913 fSW = 5MHz |

| トランスで増加するインダクタンス (Lm) | $$\text{L}_m \le \frac{\text{Dead Time}}{8 \times \text{Coss} \times f_{sw}} = \frac{25\,ns}{8 \times 0.15\,nF \times f_{sw}}$$

このLmは一次側スイッチのゼロ電圧スイッチング (ZVS) を保証します。 |

T1の設計の詳細については、トランスの設計セクションをご参照ください。 |

| 整流ダイオード (D1とD3) | $$I_{PEAK}=\pi \times I_{OUT}$$

ショットキーダイオードを使用してスイッチング損失を最小限に抑え、ZVSを実現します。 |

D1とD3の推奨事項はセクション3で示されます。 |

| 出力コンデンサ (C6とC7) | $$C_6 = C_7 \geq \frac{Q_g}{V_{\text{RIPPLE}}}$$

ここで、Qgは、電源供給を受けるデバイス (例えば、SiCまたはIGBT) のゲートチャージャであり、VRIPPLEは最大電圧リップルです。 |

C6とC7を22μF以上にする必要がある場合は、設計にMPQ18913の代わりにMPQ18913Aを選択します。 |

| 周波数設定抵抗器 (R3) | $$R_3 = \frac{100k\Omega}{f_{sw} \text{(MHz)}}$$ | |

| 共振コンデンサ (Cr) | $$C_r = \frac{1}{4 \times \pi^2 \times (2 \times L_{l1}) \times f_{sw}^2}$$ | インダクタンス漏れ (Ll1) はトランスの設計後に決定されます。 |

2. トランスの設計

トランスの主な仕様は、磁化インダクタンス、電力損失、絶縁電圧 (VISOLATION) 定格、および結合容量です。設計が容易で結合容量が少ないため、推奨されるトランスには2種類 (トロイダルとプレーナー) があります。

2.1. コア材料の選択

MPQ18913の高いfSWを活用するには、コアが高周波で動作できる必要があります。コア材料は相対透磁率が低い必要があります (100~1000)。コア材料のオプションには、P9L (0.5MHz~1.5MHz、Encore製)、PC50 (1MHz ~ 2MHz、TDK製)、61材料 (?2MHz、Fair-Rite製) などがあります。

2.2. トロイダルトランス

トロイダルトランスをセットアップするには、以下のガイドラインに従ってください。

1. トロイダルトランスの巻数比を選択する。

共振周波数 (fr)、LLCコンバータの電圧利得はトランスの巻数比 (N) に等しく、式 (7) で計算できます。

$$N=\frac{V_{OUT\_MIN}+2V_f+V_{RESISTIVE\_DROP}+V_{HEADROOM}}{V_{IN\_MIN}}$$ここでVFは整流ダイオード (D1とD3) の電圧降下、VRESISTIVE_DROPは一次側MOSFETの電圧降下とトランス巻線の抵抗、VOUT_MINはVOUTの下限値、VIN_MINは最低のVIN、およびVHEADROOMはダミーロード (例えば、R1の電力損失や20VOUTおよび-4VOUTに接続された余分な抵抗負荷) によるVOUT降下です。

VRESISTIVE_DROPは負荷電流 (ILOAD) に比例し、ゲートドライバ電源のロードレギュレーションに重要です。ロードレギュレーションの場合、トランスの巻線の抵抗を減らすために最小巻数 (N) が推奨されます。

(2VF + VRESISTIVE_DROP) は式 (8) で推定できます。

$$2V_F+V_{RESISTIVE\_DROP}=(4N+4) \times I_{LOAD}$$図3はトロイダルトランスを示しています。

図3: トロイダルトランス

2. ウィンドウのサイズを選択する。

トロイダルトランスのウィンドウサイズは、巻線に合わせて慎重に選択する必要があります。巻数が与えられた場合、磁石ワイヤの直径は式 (9) で計算できます。

$$D_{TOTAL}=D_{CONDUCTOR}+2 \times T_{INSULATION}$$ここで、DTOTALは巻線の直径、DCONDUCTORは導体の直径、TINSULATIONは絶縁層の厚さです。

DCONDUCTORは?fSWでの表皮深さの4倍になる可能性があります。TINSULATIONはVISOLATIONの定格に関連しています。必要なVISOLATIONが2kV未満の場合、破壊電圧 (VBREAK) がトランスのVISOLATION定格を越えるエナメル線を選びます。必要なVISOLATIONが2kVを超える場合は、二重または三重絶縁電線の使用を推奨します。巻数比 (N) が1でない場合、巻線の低電圧側に厚い絶縁層を使用します。2つのサイドでVISOLATION定格の2倍に等しいVBREAKを持っています。

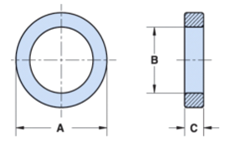

図4はトロイドコアの幾何学的構造を示しています。

図4: トロイドコアの幾何学的構造

トロイドコアの内径 (B) は巻線にフィットできる必要があります。Bは、式 (10) で計算できます。

$$N_1 \sin^{-1}\frac{D_1}{B-D_1}+N_2 \sin^{-1}\frac{D_2}{B-D_2}\lt\frac{2}{3}\pi$$ここで、N1およびN2は巻き数、D1およびD2線径です。

3. コアサイズは、スクエアターンあたりのインダクタンス (AL) とコア損失に基づいて選択します。

ALは式 (11) で計算できます。

$$L_m=N_1^2 \times A_L$$ここで、Lmはトランスで増加するインダクタンスであり、式2で計算できます (4ページの表1を参照)。他の2つの幾何学的パラメータ (AとC) は、ALに応じて選択できます。

最大磁束密度 (BMAX) は、コア損失が許容できるかどうかを確認できます。BMAXは、式 (12) で推定できます。

$$B_{MAX}=\frac{V_{IN\_MAX}}{4 \times f_{SW} \times N_1 \times (A-B) \times C}$$fSWとBMAXにおけるコア損失密度 (コア材料ベンダーから提供) について考えてみましょう。性能のためコア損失密度は150mW/cm3を超えてはいけません。アプリケーションで密度が150mW/cm3を超える必要がある場合有効面積が大きいコア、または巻数が多いコアを選択します。

4. トランスボビンを選択する。

コアと巻線に適合するトランスボビンを選択します。トランスのボビンのサイズと一次側と二次側のリード間の沿面距離は重要です。3kVのVISOLATION定格では3.5mm以上の沿面距離、および5kVのVISOLATION定格では7mm以上の沿面距離分離が推奨されます。

トランス組み立て後、二次側の2つの端子を短絡した状態で、一次側でその漏れインダクタンスを測定できます。次に、共振容量は式6で計算できます (4ページの表1参照)。

2.3 プレーナートランス

プレーナートランスをセットアップするには、以下のガイドラインに従ってください。

1. プレーナートランスの巻数比を選択する。

プレーナートランスの巻数比を決定する方法は、トロイダルトランスの場合と同じです。4ページのトロイダルトランスセクションの手順1に従って、プレーナートランスの巻数比を決定します。

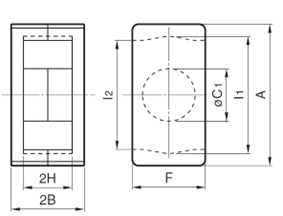

図5はERコアを備えたプレーナートランスを示しています。

図5: ERコア付きプレーナートランス

2. ウィンドウのサイズを選択する。

6層PCBレイアウトを使用する場合は、次のように中間層を使用して一次側と二次側を形成します。

- コイルを使用して中間層1と中間層2を直列に接続して一次側を形成します。

- コイルを使用して中間層3と中間層4を直列に接続して二次側を形成します。

ハイポットでの故障によってコアが隠れるのを避けるため、上層と下層のコイルを接続しないでください。

図6はERコアの幾何学的構造を示しています。

図6: ERコアの幾何学的構造

ウィンドウサイズ (l1 - C1) は式 (13) で計算できます。

$$\frac{l_1-C_1}{2}\ge \frac{N_X}{2} \times W_{TRACE}+(\frac{N_x}{2}-1) \times W_{CLEARANCE}+2 \times L_{INSULATION}$$ここで、NXは一次側 / 二次側の巻数、WTRACEはPCB配線幅 (1オンスPCBの0.25負荷の場合は10ミル)、WCLEARANCEは2つのPCB配線間のクリアランスで (通常、1オンスのPCBでは4ミル以上のクリアランスが必要)、LINSULATIONはPCB配線とコア間のクリアランスです。

また、LINSULATIONは式 (14) で計算できます。

$$L_{INSULATION}=\frac{V_{ISOLATION}}{2 \times E_b}$$ここで、Ebはプリプレグ材料の誘電強度です。

一次側と二次側との間の全方向のクリアランスは式 (15) で計算できます。

$$T_{INSULATION}=\frac{V_{ISOLATION}}{E_b}$$代表的なPCBレイアウトの場合、絶縁強度は250V/milである必要があります。

3. スクエアターンあたりのインダクタンスを決定する (AL)。

最適なALは?6ページの式11または式2 (4ページの表1参照) で計算できます。選択したコア材料の透磁率が高い場合、ALを減らすためにエアギャップが必要です。エアギャップコアは、エアギャップ付きERコアを示す図7に示されています。

図7 : エアギャップ付きERコア

4. コアサイズを選択する。

プリント基板全体の厚みに応じて、内側の高さ (2H) を選択します。次に、PCBとコイルに適合するコアを選択します。

BMAXはコア損失が許容できるかどうかを確認できます。BMAXは、式 (16) で推定できます。

$$B_{MAX}= \frac {V_{IN\_MAX}}{8 \times f_{SW} \times N_1 \times A_e}$$fSWとBMAXにおけるコア損失密度 (コア材料ベンダーから提供) について考えてみましょう。熱性能のためコア損失密度は200mW/cm3を超えてはいけません。アプリケーションで密度が200mW/cm3を超える必要がある場合有効面積が大きいコア、または巻数が多いコアを選択します。

トランス組み立て後、二次側の2つの端子を短絡した状態で、一次側でその漏れインダクタンスを測定できます。そして、共振容量は式6で計算できます (4ページの表1参照)。

3. 整流ダイオードの選択

ダイオードの容量 (CT) および逆電流 (IR) は整流ダイオードの2つの重要なパラメータです。CTおよびIRは負荷調整に悪影響を及ぼす可能性があります。

CTはLLC共振ネットワークの一部であり、軽負荷時にLLCコンバータのゲインを上げます。小さなCTはロードレギュレーションの向上のため推奨されます。

IRはダイオードの温度が上昇すると増加します。負荷が重い場合、ダイオードの温度が上昇し、IRがLLCコンバータに余分な負荷を加えます。これにより、ロードレギュレーションが向上します。

これらのパラメータを考慮すると、整流ダイオードにはBAT165 (40V、0.75A、AEC-Q101) またはPMEG6010CEJ (60V、1A、AEC-Q101) を使用することをお勧めします。

_______________________

興味のある内容でしたか? お役に立つ情報をメールでお届けします。今すぐ登録を!

アカウントにログイン

新しいアカウントを作成