Advantages of Constant-On-Time Control in DC/DC Converters

Get valuable resources straight to your inbox - sent out once per month

We value your privacy

November 22, 2019 —This article explores why constant-on-time control (COT) has proven to be a more effective control mode for DC/DC converters than the traditional current mode control scheme.

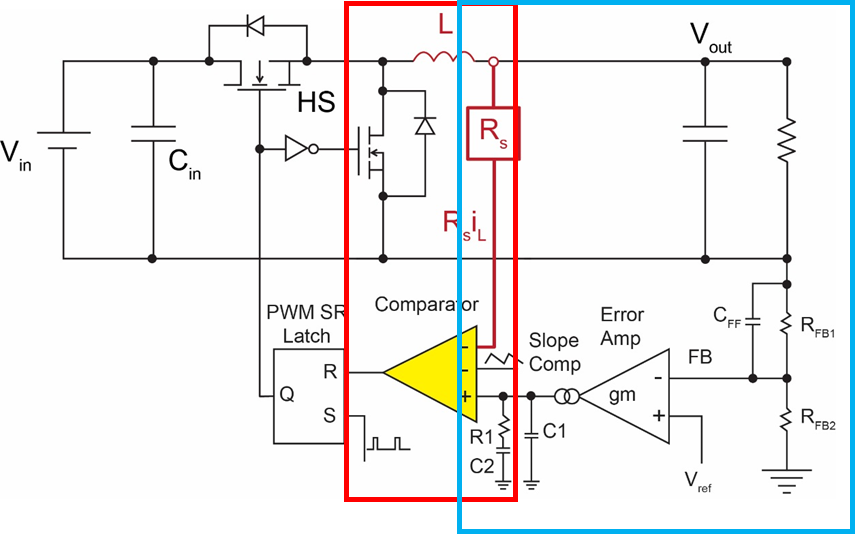

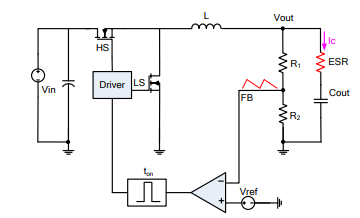

Figure 1 shows the architecture of a traditional current mode DC/DC converter. The sensed current information (outlined in red) is compared with the output of the error amplifier in the voltage feedback loop (outlined in blue) to generate the PWM pulse that controls the MOSFETs.

Two factors in this control architecture impact the transient response performance to output load changes.

The first is due to the error amplifier block. In the voltage feedback loop, the error amplifier in the compensation network acts as a low-pass filter, which slows down the converter’s response time to any variation in the output voltage.

Figure 1: Current Mode DC/DC Architecture

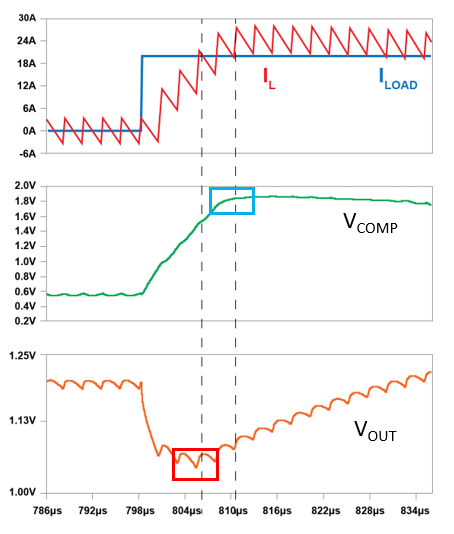

Figure 2 shows the effect of this error amplifier delay on the loop transient response. In this example, the load current steps from 0A to 20A with a fast slew rate. In the bottom curve, VOUT drops significantly before recovering. The green curve is the output of the error amplifier. It does not reach its maximum value until two cycles after the maximum undershoot has occurred. This delay is caused by the inherent low-pass filter of the error amplifier.

Figure 2: Effect of Error Amplifier Delay on Output Undershoot

Figure 3: Effect of the Internal PWM Clock Period on Output Undershoot

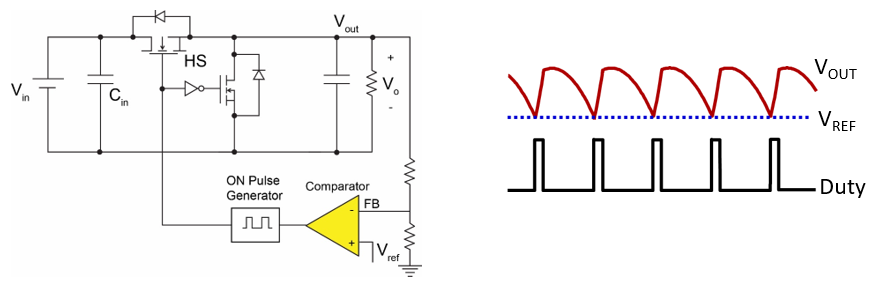

With constant-on-time architecture, the control structure is very simple compared to traditional voltage/current mode control. When employing COT, the output voltage is sensed via feedback resistors (see Figure 4). The valley of the output ripple voltage is compared directly with the reference voltage to generate a fixed on-time pulse to turn on the high-side MOSFET. When the on-time pulse expires, the high-side MOSFET turns off (and the low-side turns on).

Figure 4: Constant-On-Time DC/DC Architecture

COT architecture does not require the traditional compensation network of voltage or current mode DC/DC control. This makes the converter easier to design by requiring fewer components and eliminating the need to spend time tuning the compensation values. Reliable COT operation does require that the output voltage ramp at the feedback node is large enough for jitter-free operation. To ensure this, the ramp should be larger than any random system noise on the feedback input.

If the output capacitors have sufficient equivalent series resistance (ESR), then the feedback ramp voltage caused by this ESR dominates the inductor’s smaller series resistance. In this case, a simple resistive divider network is sufficient (see Figure 5). This is typically used for electrolytic or POSCAP capacitors.

Figure 5: COT Feedback Input Ramp Voltage Derived From Output Capacitor ESR

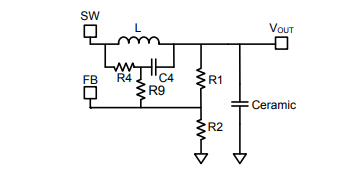

Figure 6: COT Feedback Input Ramp Voltage Derived from Inductor Ramp Generator Circuit

If low-ESR ceramic capacitors are preferred, then an additional “ramp generator” circuit can be used to create the required feedback ramp voltage (see Figure 6).

The important point to note is that the feedback voltage is fed directly into the comparator driving the constant-on-time control block. There is no error amplifier block or internal fixed-frequency clock that can introduce a delay to affect the transient response time.

Rather than use a fixed-frequency clock, the COT control architecture uses the reference comparator output to trigger a fixed-on-time pulse generator. The frequency at which the pulses occur is determined by the output load current. In continuous conduction mode with a steady output current requirement, the COT control operates at an approximately fixed frequency. However, during a load-step transient where more current is required, the COT pulse generator block outputs a high pulse rate to minimize the output undershoot. Once the normal output voltage is attained, the pulse rate reduces to the level required to maintain a steady regulated output voltage.

COT control has a transient response time up to two times faster than traditional voltage or current mode control. Lower undershoot makes it easier to meet load voltage tolerance specifications. This also means that COT-based convertors require less output capacitance to meet a given load transient response compared to voltage or current mode converters, saving space and cost.

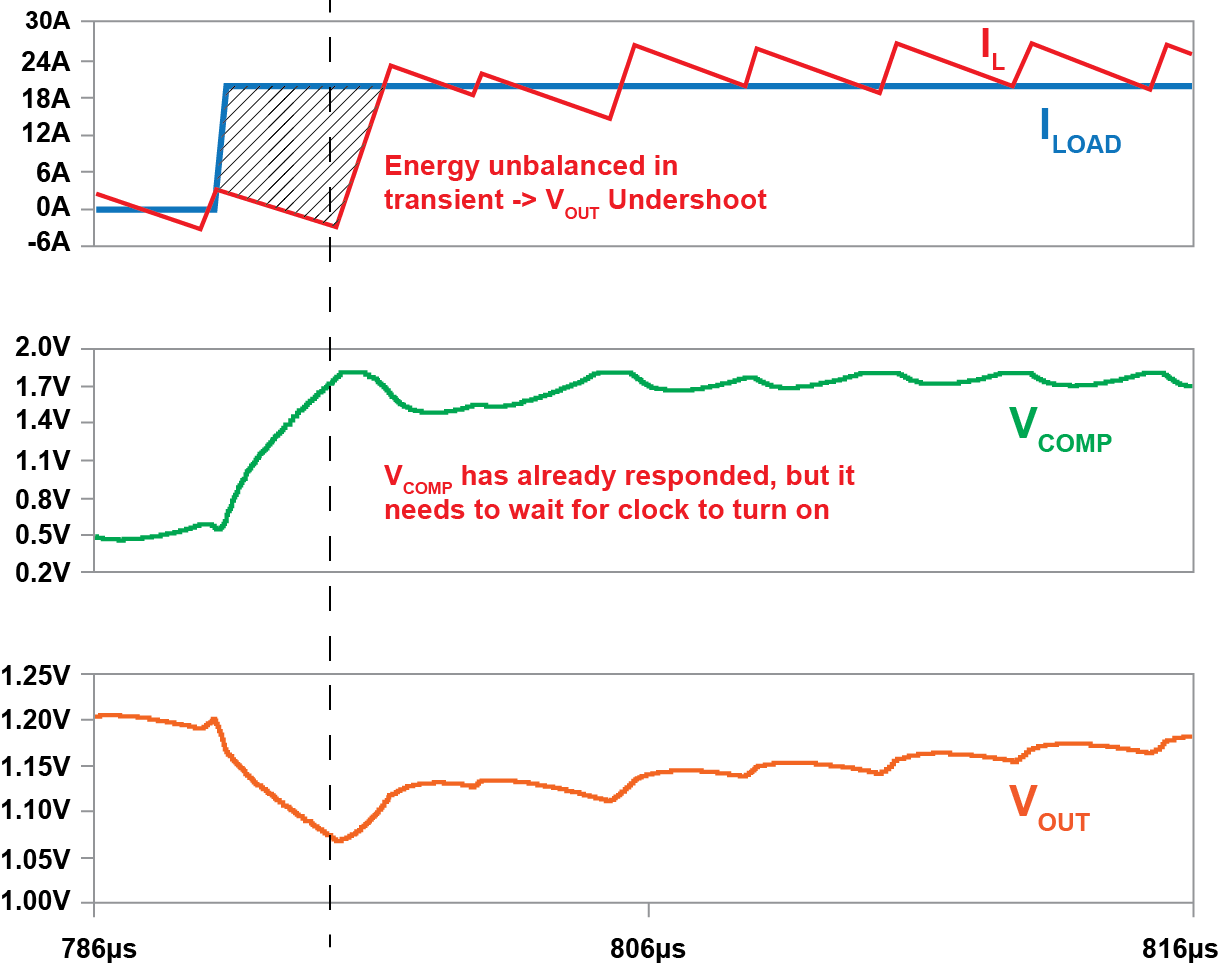

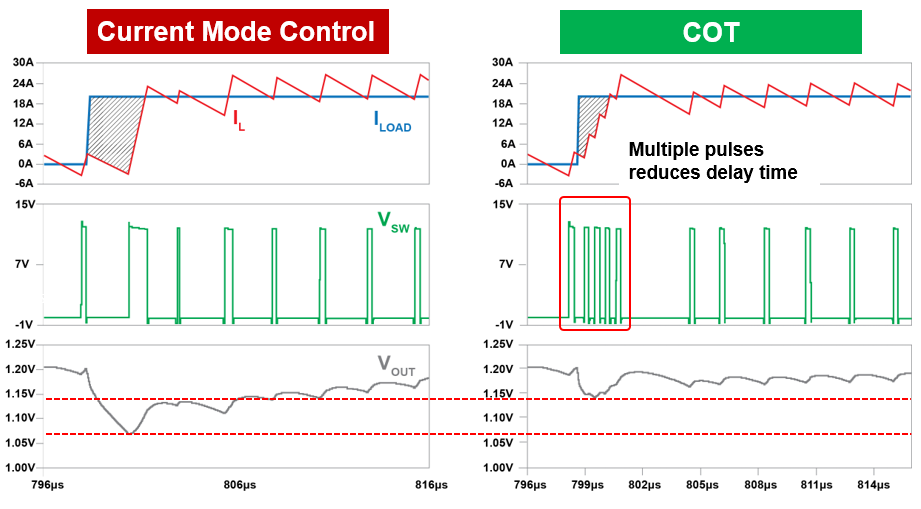

Figure 7 shows a comparison between current mode control and COT control. For the same load current step-up, COT control can switch faster to reduce the gap between the inductor and output current and further reduce output undershoot

Figure 7: COT Transient Response to Load-Step Compared to a Current Mode Control Scheme

Another advantage of COT variable frequency control architecture is that at light loads, the pulse rate is further reduced and high efficiency is maintained. Because pulses are only issued when the output load demands it, internal switching losses are minimized compared to a voltage or current mode architecture with a permanently switching clock. This means COT-based DC/DC converters have very high efficiency under light-load or no-load conditions, making them excellent choices for battery-powered devices or equipment with power-save modes.

In summary, COT control has become the de facto solution over traditional current and voltage mode control methods due to its faster transient response, higher efficiency, fewer components, and ease of design.

Log in to your account

Create New Account